时序比较器课程设计报告

时序比较器课程设计报告

《时序比较器课程设计报告》由会员分享,可在线阅读,更多相关《时序比较器课程设计报告(35页珍藏版)》请在装配图网上搜索。

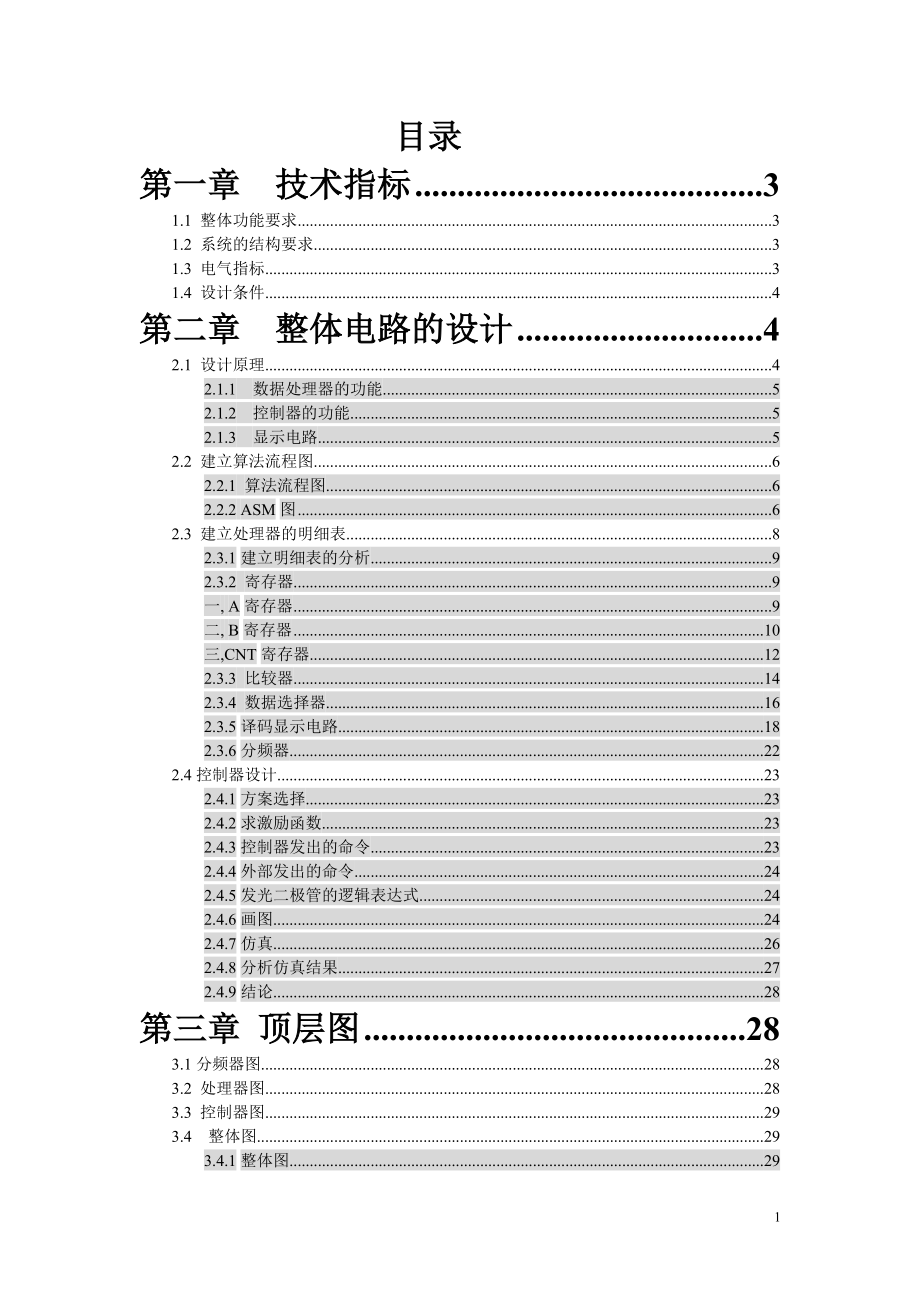

1、 目录第一章 技术指标31.1 整体功能要求31.2 系统的结构要求31.3 电气指标31.4 设计条件4第二章 整体电路的设计42.1 设计原理42.1.1 数据处理器的功能52.1.2 控制器的功能52.1.3 显示电路52.2 建立算法流程图62.2.1 算法流程图62.2.2 ASM图62.3 建立处理器的明细表82.3.1建立明细表的分析92.3.2 寄存器9一, A寄存器9二, B寄存器10三,CNT寄存器122.3.3 比较器142.3.4 数据选择器162.3.5译码显示电路182.3.6分频器222.4控制器设计232.4.1方案选择232.4.2求激励函数232.4.3控制

2、器发出的命令232.4.4外部发出的命令242.4.5发光二极管的逻辑表达式242.4.6画图242.4.7仿真262.4.8分析仿真结果272.4.9结论28第三章 顶层图283.1分频器图283.2 处理器图283.3 控制器图293.4 整体图293.4.1整体图293.4.2 仿真图303.4.3分析仿真结果313.4.4结论323.5 整体结论32第四章 实验小结334.1 实验小结334.2 心得体会33第一章 技术指标1.1 整体功能要求 现代工业控制和微机系统中离不开数据处理器。时序比较器是数据处理器的一个部分,它能将输入的8421BCD码存储并进行比较,最终以十进制数显示其大

3、小。时序比较器的功能是,用同一组输入端口分两次送入两组数据,经过比较显示出数值大的一组数据值。 1.2 系统的结构要求时序比较器的总体结构方框图如图1-1所示。在图1-1中:RESET:开机后按复位键,低电平有效,为整个系统的复位。AJ:当一组数据(X3X0)设置完毕时,按“确认”键后输入的这组数据有效。Y1:第一组X3X0数据输入,若第一组为大数,则Y1=1,LED1亮。Y2:第二组X3X0数据输入,若第二组为大数,则Y2=1,LED2亮。D3D0:较大数输出端,驱动显示电路显示十进制。1.3 电气指标(1)数据输入采用并行送数,系统先后收到两组8421BCD码后比较其大小,将大数输出,用十

4、进制数显示出来。(2)显示时间8S,显示结束电路自动清零,进入初始状态。(3)仅在开机后人工操作RESET开关,使RESET=0整机清零,整机立即进入工作状态;LED1点亮表示允许输入第一组数据Xa。(4)按一次AJ键,表示输入一脉冲信号,Xa被确认后LED2点亮,表示允许输入第二组数据Xb。(5)再按一次AJ键,Xb被确认,电路立即比较大小,输出显示大数。(6)对比较结果:XaXb ,Xa=Xb 或 XaXb 时,LED1闪亮; Xa ASM图: 原则1:在算法的起始点安排一个状态; 如:图2-2 图 2-2原则2:必须用状态来分开不能同时实现的寄存器传输操作;如:图2-3 图 2-3原则3

5、:如果判断框中的转移条件受前一个寄存器操作的影响,应在它们之间安排一个状态。 如:图2-4 图 2-42,根据课题分析,RESET信号为外部控制信号,即根据算法流程图可以得到ASM图2-5。图2-5 时序比较器ASM图2.3 建立处理器的明细表根据ASM图可列出处理器的明细表,如表2-1所示:2.3.1建立明细表的分析首先根据明细表可知,处理器有三个寄存器,即:A寄存器、B寄存器和CNT寄存器;其次处理器有比较器、数据选择器、译码器和振荡器。2.3.2 寄存器一, A寄存器 1,A寄存器的功能从处理器明细表,可知A寄存器有三个功能: 保持、置数和清零。 2,讨论,求出其控制命令 根据分析A寄存

6、器的功能以及数字电路第六章的学习,我们选取74194芯片作为实现其三个功能寄存器。从74194功能表可知,它有两个功能控制端M1M0,即:功能控制端的功能表如表2-2所示。同时74194芯片清零为异步清零。 3,获得电路图(1)芯片设计图(如图2-6):(2)仿真设计图(如图2-7): 4,仿真(如:图2-8)5,分析仿真结果 (1)RESET=1,T0=T1=AJ=0,系统整体清“0”,即虽然X3X0=0110,但是A3A0=0000;(2)RESET=0,T0=1,T1=AJ=0,系统整体清“0”,即虽然X3X0=0110,但是A3A0=0000;(3)RESET= T0=0, T1=1,

7、AJ=0,因为AJ=0,故不可以置数:A3A0=0000;(4)RESET= T0= T1=0,电路保持,即虽然AJ=1,但是A3A0=0000;(5)RESET= T0=0,T1= AJ=1,X3X0=0110,置数成功:A3A0=0110。6,结论(1)RESET和T0中只要有一个置为1,则系统整体清“0”;(2)T1和AJ中两个都为1时,置数才会成功;反之,保持。(3)通过仿真,该74194能达到所要满足的A寄存器的功能。二, B寄存器1,B寄存器的功能从处理器明细表,可知B寄存器有三个功能: 保持、置数和清零。 2,讨论,求出其控制命令根据分析B寄存器的功能以及数字电路第六章的学习,我

8、们同样选取74194芯片作为实现其三个功能寄存器。从74194功能表可知,它有两个功能控制端M1M0,即:功能控制端的功能表如表3所示。则M1=M0=SET Xb=T2AJ, CR=RESET+T0。3,获得电路图(1)芯片设计图(如图2-9):(2)仿真设计图(如图2-10): 4,仿真(如图2-11)5,分析仿真结果 (1)RESET=1,T0=T1=AJ=0,系统整体清“0”,即虽然X3X0=1001,但是A3A0=0000;(2)RESET=0,T0=1,T1=AJ=0,系统整体清“0”,即虽然X3X0=1001,但是A3A0=0000;(3)RESET= T0=0, T1=1,AJ=

9、0,因为AJ=0,故不可以置数:A3A0=0000;(4)RESET= T0= T1=0,电路保持,即虽然AJ=1,但是A3A0=0000;(5)RESET= T0=0,T1= AJ=1,X3X0=1001,置数成功:A3A0=1001。6,结论(1)RESET和T0中只要有一个置为1,则系统整体清“0”,RESET信号为外部清零,T0信号为系统同步信号;(2)T1和AJ中两个都为1时,置数才会成功;反之,保持。(3)通过仿真,该74194能达到所要满足的B寄存器的功能。三,CNT寄存器1,CNT寄存器的功能从处理器明细表可知,它主要是作为定时器使用。定时长度为:8s,即为M=8的加法计数器。

10、当控制器进入T3状态时,计数器开始计数;当所计的数为“8”时,计数器停止计数并清零返回到初始状态。因此,CNT寄存器的功能有3个:清零、计数和预置零。 2,讨论,求出其控制命令根据以上分析CNT寄存器以及数字电路第六章的学习,我们可选用74161芯片来实现它的3个功能。同时74161芯片为异步清零,同步置数。CP=2HZ。即:功能控制端的功能表如表2-3所示: 3,获得电路图(1)芯片设计图(如图2-12):(2)仿真设计图(如图2-13): 4,仿真(如图2-14)5,分析仿真结果 (1)RESET=1,T0=T3=0,系统整体清“0”;(2)RESET=0, T0=1,T3=0, 系统整体

11、清“0”;(3)RESET=T0=0,T3=1,当16个脉冲(即8S)后,CNT8=1,且CNT8维持1个脉冲;(4)RESET=T0=0,T3=0,74161寄存器不工作,CNT8始终为0。6,结论(1)RESET和T0只要有一个为1,则系统整体清“0”;(2)T3=1,74161工作,周期为8s;反之,T3=0,74161不工作。(3)通过仿真,该74161能达到所要满足的CNT寄存器的功能。2.3.3 比较器 1,分析根据分析处理器明细表以及数字电路第六章的学习,我们可选用7485芯片来实现Xa,Xb的比较。其(A=B)i=1 , (AB)i=0 。2,比较器的功能(1)、A3A0 接A

12、寄存器的Q3Q0 ;(2)、B3B0 接B寄存器的Q3Q0 ;(3)、输出FAB、FAB、FA=B ; A3A0= B3B0 ,则FA=B =1, FAB=FAB=0 A3A0 B3B0 ,则FAB =1,FA=B =FAB=0 A3A0 B3B0 ,则FAB =1,FA=B =FAB=03,获得电路图(1)芯片设计图(图2-15):(2)仿真设计图(如图2-16): 4,仿真(如图2-17)5,分析仿真结果 (1)RESET=1,TO=AJ=0,T1=T2=0;系统整体清“0”;(2)RESET=T0=0,T1=AJ=1,T2=0,系统给A寄存器置数:X3X0=1001,则A3A0=1001

13、;(3)RESET=T0=0,T2=AJ=1,T1=0,系统给B寄存器置数:X3X0=0101,则B3B0=0101;当给B寄存器置数结束后,立即进行比较:GG=1,EE=LL=0;表明第一个数大于第二个数;(4)RESET=1,系统整体清“0”;(5)RESET=T0=0,T1=AJ=1,T2=0,系统给A寄存器置数:X3X0=0001,则A3A0=0001;(6)RESET=T0=0,T2=AJ=1,T1=0,系统给B寄存器置数:X3X0=1001,则B3B0=1001;当给B寄存器置数结束后,立即进行比较:EE =1,GG=LL=0;表明第一个数小于第二个数;(7)RESET=1,系统整

14、体清“0”;(8)RESET=T0=0,T1=AJ=1,T2=0,系统给A寄存器置数:X3X0=1001,则A3A0=1001;(9)RESET=T0=0,T2=AJ=1,T1=0,系统给B寄存器置数:X3X0=1001,则B3B0=1001;当给B寄存器置数结束后,立即进行比较:GG=1,EE=LL=0;表明第一个数等于第二个数;6,结论(1)数a和数b是并行送入的,分别通过T1和T2控制,但在送数时,AJ=1,否则也不置数;其原理可以见2.3.2A、B寄存器;(2)当送完第二个数,系统立即进行比较。(3)通过仿真,该74161能达到所要满足的CNT寄存器的功能。2.3.4 数据选择器 1,

15、分析 根据题目技术要求选出大数,即从A和B两数中选出大数。可选用二选一数据选择器。由于A和B为四位而二进制数,则选用74157芯片四个二选一数据选择器。2,二选一MUX的地址,控制端和数据端连接从ASM图和处理器明细表可知,输出端输出大数,地址A端连接到FAB。分析:当A=FAB=1时,选择D1数据输出(Y=B,B为大数)。当A=FAB=0时,AB,选择D0数据输出(Y=A,A为大数) A= B,选择D0数据输出(Y=A,选A输出)3, 二选一MUX的使能端的控制 当=1,Y=0时,数据选择器不工作; 当=0,Y输出取决于地址A。因此,从ASM图和处理器明细表可知:= 当T3=0时,=1,Y=

16、0时,数据选择器不工作; 当T3=1时,=0,数据选择器工作。4,获得电路图(1)芯片设计图(如图2-18):(2)仿真设计图(如图2-19):5,仿真(如图2-20)6,分析仿真结果 (1)RESET=1,TO=AJ=0,T1=T2=T3=0;系统整体清“0”;(2)RESET=T0=0,T1=AJ=1,T2=T3=0,系统给A寄存器置数:X3X0=0101,则A3A0=0101;(3)RESET=T0=0,T2=AJ=1,T1=0,系统给B寄存器置数:X3X0=1001,则B3B0=1001;当给B寄存器置数结束后,立即进行比较:EE =1,GG=LL=0;表明第一个数小于第二个数;但是因

17、为T3=0,所以74157不工作,即Y4Y1=0000; (4)RESET=T0=0,T2=AJ=1,T1=0,T3=1;Y4Y1=1001显示的是大数;(5)RESET=1,系统整体清“0”;(6)RESET=T0=0,T1=AJ=1,T2=0,系统给A寄存器置数:X3X0=1001,则A3A0=1001;(7)RESET=T0=0,T2=AJ=1,T1=0,T3=1,系统给B寄存器置数:X3X0=0001,则B3B0=1001;当给B寄存器置数结束后,立即进行比较:GG=1,EE=LL=0;表明第一个数大于第二个数;且Y4Y1=1001;(8)RESET=1,系统整体清“0”;(9)RES

18、ET=T0=0,T1=AJ=1,T2=0,系统给A寄存器置数:X3X0=0001,则A3A0=0001;(10)RESET=T0=0,T2=AJ=1,T1=0,系统给B寄存器置数:X3X0=0001,则B3B0=0001;当给B寄存器置数结束后,立即进行比较:GG=1,EE=LL=0;表明第一个数等于第二个数;且Y4Y1=0001。6,结论(1)当送完第二个数,系统立即进行比较。当T3=1时,74157工作。(2)通过仿真,该74157能达到所要满足的CNT寄存器的功能。2.3.5译码显示电路1,显示管译码器选择7448芯片(8421BCD码译成ag的电位信号),显示选择共阴极数码管,如图2-

19、21:8421BCD码译成ag的电位信号表(如表2-4):2,译码器(1)方案选择由8421BCD码译成ag的电位信号表可以绘制卡诺循环图,即用组合电路设计,得到的电路有与或门等等,但是电路非常复杂,所以使用硬件描述语言,即VHDL语言实现。通过HDL Editor编写7448模版(定义输入输出管脚,实现结构体功能),再链接(Synthesis-check syntax),最后运行(Project-Creat Maacro).(2)程序library IEEE;use IEEE.std_logic_1164.all;entity X74_48 is port ( A3: in STD_LOGI

20、C; A2: in STD_LOGIC; A1: in STD_LOGIC; A0: in STD_LOGIC; a: out STD_LOGIC; b: out STD_LOGIC; c: out STD_LOGIC; d: out STD_LOGIC; e: out STD_LOGIC; f: out STD_LOGIC; g: out STD_LOGIC );end X74_48; architecture X74_48_arch of X74_48 is signal x:std_logic_vector(3 downto 0); signal y:std_logic_vector(6

21、 downto 0); begin x=A3 & A2 & A1 & A0; with x select y=1111110 when 0000, 0110000 when 0001, 1101101 when 0010, 1111001 when 0011, 0110011 when 0100, 1011011 when 0101, 1011111 when 0110, 1110000 when 0111, 1111111 when 1000, 1111011 when 1001, 0000000 when others; a=y(6); b=y(5); c=y(4); d=y(3); e=

22、y(2); f=y(1); gXb图3-6:Xa=Xb图3-7:XaXb3.4.3分析仿真结果1、分析图3-5:(1)RESET=0,AJ=0,此时系统处于没有工作的情况;(2)RESET=1,外部启动信号, T0=1,整体清“0”;(3)RESET=T0=0,AJ=0,X3X1=1011,T1=1,LED1灯亮,T2=T3=0,因为AJ=0,所以一直在循环等待给A寄存器置数;(4)RESET=T0=0,AJ=1,X3X1=1011,T1=0,T2=1,T3=0,表明给A寄存器置完数,立即LED2灯亮,即给B寄存器置数;此时GG=1;(5)RESET=0,AJ=0数值发生变化X3X0=0100

23、,但是T2=1,说明仍在循环给B寄存器置数;(6)RESET=0,T0=0,AJ=1,表明完成了给B寄存器置数;(7)RESET=0,AJ=0,T0=T1=T2=0,T3=1,送完第二个数,立即进行比较:GG=1,EE=LL=0,则显示大数,LED1灯闪亮,LED2灯熄灭;ABCDEFG=1111011,即译码管显示9,CNT8=0;(8)当灯持续闪亮8s之后,CNT8=1,表明系统下一个脉冲会自动清“0”;(9)T0=1,电路自动整体清“0”;(10)RESET=AJ=0,T0=0,T1=1,表明始终在等待外部给A寄存器置数,直至AJ=1。即循环至(3)。2、分析图3-6:(1)RESET=

24、0,AJ=0,此时系统处于没有工作的情况;(2)RESET=1,外部启动信号, T0=1,整体清“0”;(3)RESET=T0=0,AJ=0,X3X1=0101,T1=1,LED1灯亮,T2=T3=0,因为AJ=0,所以一直在循环等待给A寄存器置数;(4)RESET=T0=0,AJ=1,X3X1=0101,T1=0,T2=1,T3=0,表明给A寄存器置完数,立即LED2灯亮,即给B寄存器置数;此时GG=1;(5)RESET=0,AJ=0,X3X0=0101,但是T2=1,说明仍在循环给B寄存器置数;(6)RESET=0,T0=0,AJ=1,表明完成了给B寄存器置数;(7)RESET=0,AJ=

25、0,T0=T1=T2=0,T3=1,送完第二个数,立即进行比较:EE=1,GG=LL=0,则显示大数,LED1灯和LED2灯交替闪亮;ABCDEFG=1011011,即译码管显示5,CNT8=0;(8)当灯持续闪亮8s之后,CNT8=1,表明系统下一个脉冲会自动清“0”;(9)T0=1,电路自动整体清“0”;(10)RESET=AJ=0,T0=0,T1=1,表明始终在等待外部给A寄存器置数,直至AJ=1。即循环至(3)。3、分析图3-7:(1)RESET=0,AJ=0,此时系统处于没有工作的情况;(2)RESET=1,外部启动信号, T0=1,整体清“0”;(3)RESET=T0=0,AJ=0

26、,X3X1=0001,T1=1,LED1灯亮,T2=T3=0,因为AJ=0,所以一直在循环等待给A寄存器置数;(4)RESET=T0=0,AJ=1,X3X1=0001,T1=0,T2=1,T3=0,表明给A寄存器置完数,立即LED2灯亮,即给B寄存器置数;此时GG=1;(5)RESET=0,AJ=0,数值发生变化X3X0=1001,但是T2=1,说明仍在循环给B寄存器置数;(6)RESET=0,T0=0,AJ=1,表明完成了给B寄存器置数;(7)RESET=0,AJ=0,T0=T1=T2=0,T3=1,送完第二个数,立即进行比较:LL=1,GG=EE=0,则显示大数,LED2灯闪亮,LED1灯

27、熄灭;ABCDEFG=1111011,即译码管显示9,CNT8=0;(8)当灯持续闪亮8s之后,CNT8=1,表明系统下一个脉冲会自动清“0”;(9)T0=1,电路自动整体清“0”;(10)RESET=AJ=0,T0=0,T1=1,表明始终在等待外部给A寄存器置数,直至AJ=1。即循环至(3)。3.4.4结论通过仿真,该设计的时序比较器能达到所要满足的功能。且下载烧入芯片,与实物验证符合;3.5 整体结论 当将仿真电路烧入芯片后,实际连线成功后,过程如下:(1) 开RESET键(=1),电路整体清0;(2) 关闭RESET键(=0),此时LED1灯亮,表明要送入第一个数Xa;(3) 将X3-X

28、0送数,打开AJ键,即刻关闭AJ键;(4) 此时LED2灯亮,表明要送入第二个数Xb;(5) 将X3-X0送数,打开AJ键,即刻关闭AJ键;(6) 送完第二个数,电路立即比较,译码管显示大数,对应的灯亮;(7) 持续8s后,电路自动清0,此时LED1灯亮,表明要送入第一个数Xa;(8) 重复过程(3)至(7)。第四章 实验小结4.1 实验小结(1)在设置X74_48芯片时,设置的芯片名称总是与别人的相反,通过多次重试都不行,最后得知:在进入仿真软件,一定要把仿真环境设置为XC9500,95108PC84,否则就会出现类似多种情况。(2)在功能仿真时,有时没有自己要选用的端口,如用芯片连接的电路

29、,通过多次的尝试,左后得知:应该先编译一下,再进行仿真,此时端口都会出现;仿真分为功能仿真和定时仿真(该实验中,我们主要使用的是功能仿真);(3)某次,稍不注意,在图形编辑器中,将仿真波形存盘后,导致之后的仿真波形错误,得知:,在图形编辑器中,千万不可以存盘;(4)刚开始,使用该软件创建的文件名习惯以学号,即数字命名,但是编译过程中总会报错,得知:文件名必须以字母命名,不可以用数字;(5)通过多次的实验演练过程得知:仿真电路连接过程中,不要用到的端要做处理,如74194的输入端:左移位和右移位短接接地或接高电平;(6)通过多次操作实验的过程,得知:每画完一个寄存器,存盘命名,产生网络,加到网络

30、,退出,编译,再次进入,功能仿真;(7)在设置输出大数时,软件内部并没有我们所要选用的芯片,得知:使用硬件描述语言须通过HDL Editor编写,链接,运行;运行成功后,方可使用我们自己编的芯片,如7448;(8)单单对芯片是不可以访问的,故得知:当生成芯片后,可以添加输入输出管脚产生一个完整的处理器部分,此时才可以对芯片进行访问;(9)顶层图图仿真成功后,不可以直接烧入芯片,因为这样根本对实际电路没有影响,故得知:在烧入电路芯片前,应该对每个IPAD和OPAD加管脚号,且这些管脚号与电路上的编号要一一对应,然后连接的电路才可以使用;(10)某次对某电路在进行编译,可是总会报错,且经过多次确认

31、,电路图是正确的,最终在老师的指导下,得知:对某电路在进行编译之前,我们应先看一下目录下的文件个数,将不需要用的文件移除掉,因为有多个文件时,编辑器不知道识别哪一个文件进行编译,所以会报错;4.2 心得体会在学习这门课程之前,我以为自己对数字电路的掌握很好,但是通过这次课程设计,我明白了自己所学习的是微不足道的,很少在实际电路中起到作用,故在了解了实验后,我又复习了一遍模拟电路,数字电路理论,了解了综合型电子电路的设计、装配和调制方法;掌握电子元器件资料和电路资料的检索方法,并且再次学习到了很多,如:在实际电路中,一开始,输入脉冲均设置为2KHZ,由于灯不够闪亮,即闪亮很微弱,推动不够,故我们

32、对灯的输入脉冲重新设置了一个新的脉冲,对其单独置为1HZ,此后,灯的闪亮程度才达到了设计要求;在此之前,我们尝试了加两个反相器来达到该要求,可是实验证明其失败;这告知我们,电路很多时候只有通过不断的改善,尝试,试验,才能知道是否达到我们设计的要求;故由此可以推论即便我们设计的电路是正确的,但是其中肯定有不足之处,我们应大量阅读有关实验的知识,加上充分运用所学的知识,将电路设计得更加合理,精确; 还有就是实验报告的书写,让我体会到了用语言表述出我们的操作,也要对操作熟悉之后,且很多关于写报告的细节,如目录,页数,图形的编号形式,以及表等,这些都是我们必须关注的;故我们在写实验报告时,也得花更多的时间将操作回顾一遍,再整合所有的操作,以便写实验时可以在理解的基础上,将实验报告内容写得更加完美,内容衔接更加恰当。其次,在实验的过程中,我还了解了一些平常不知道的快捷操作,如CTRL+R表反向;图形的截图可以使用Print Screen键+绘图工具完成等等;总之,通过这次课程设计的学习,我深深体会了,课前的预习,课后的思索,自己上网搜索相关知识,以便更加深刻的了解实验,知道其原理,在操作时,才会得心应手,操作熟练;最后,我要感谢我们的卢庆莉老师,在卢老师的帮助下,我们才会很快的掌握该实验原理,最终完成实验。并且希望自己会充分吸取这次的经验,在以后的实验中,做得比现在更好。35

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。