Calibre DRC和LVS验证总结

Calibre DRC和LVS验证总结

《Calibre DRC和LVS验证总结》由会员分享,可在线阅读,更多相关《Calibre DRC和LVS验证总结(14页珍藏版)》请在装配图网上搜索。

1、精品文档,仅供学习与交流,如有侵权请联系网站删除Calibre学习总结第一章 Calibre简述1. 1 Calibre 简介 Calibre 作为Mentor Graphics 公司出品的后端物理验证(Physical Verification)工具,它提供了最为有效的DRC/LVS/ERC 解决方案,特别适合超大规模IC电路的物理验证。它支持平坦化(Flat mode )和层次化(Hierarchical mode)的验证,大大缩短了验证的过程;它高效可靠的性能已经被各大Foundry 认证,作为Tape Out 之前的验证标准。它独有的RVE(Result ViewEnviroment)

2、界面可以把验证错误反标到版图工具中去,而且良好的集成环境便于用户在版图和电路图之间轻松转换,大大提高了改错的效率。xCalibre 具有版图寄生参数抽取的功能。1 2手册在工作站下输入mgcdocs &命令,就可阅读Calibre的所有手册。1 3几个常用的缩写命令1、 SVRF-Standard Verification Rule Format(标准的检查文件)2、 RVE-Results Viewing Environment(显示结果用的环境窗口)3、 SVDB-Standard Verification Database (LVS results)4、 DRC-Design Rule

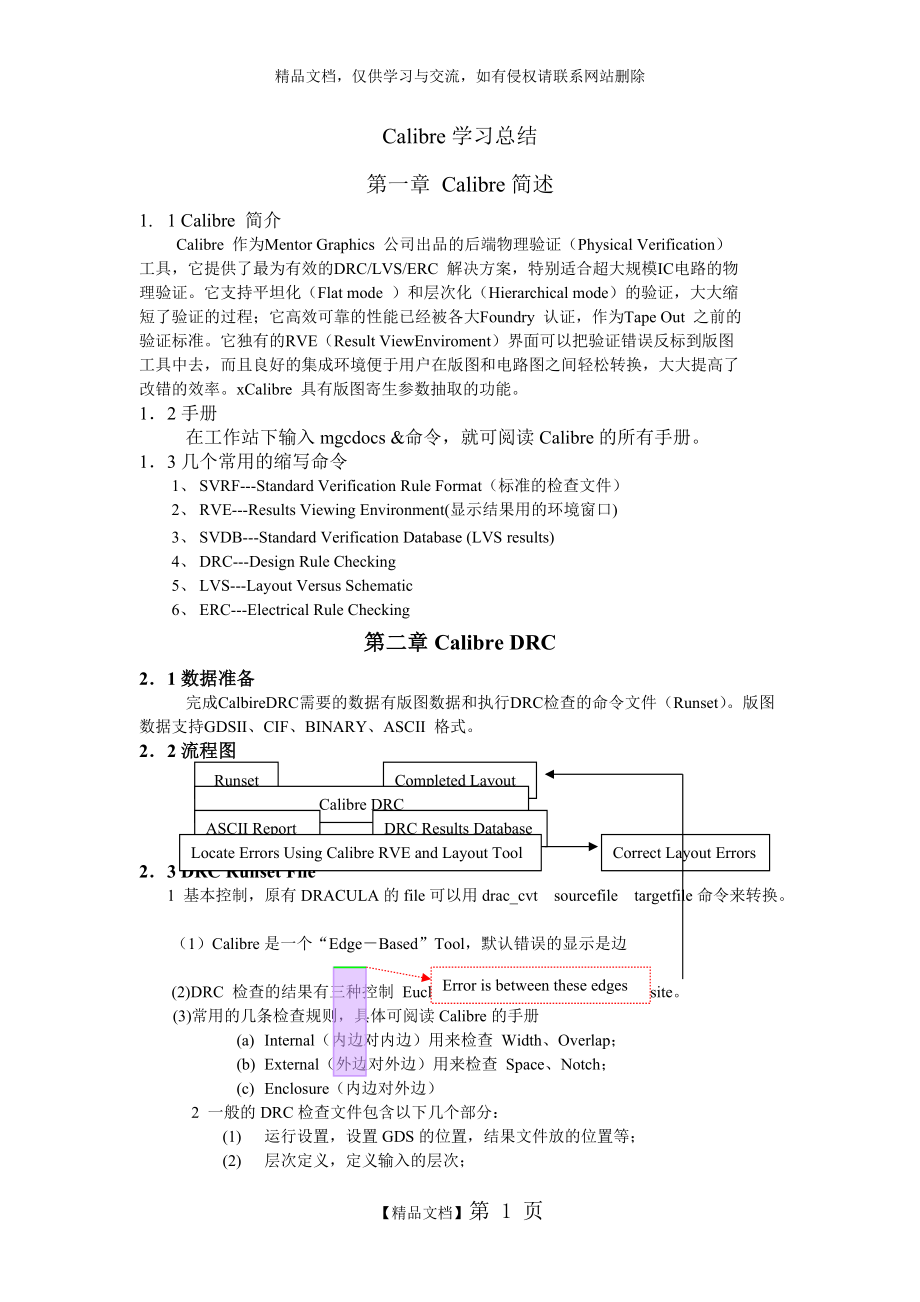

3、Checking5、 LVS-Layout Versus Schematic6、 ERC-Electrical Rule Checking第二章Calibre DRC2 1数据准备 完成CalbireDRC需要的数据有版图数据和执行DRC检查的命令文件(Runset)。版图数据支持GDSII、CIF、BINARY、ASCII 格式。22流程图Completed LayoutRunsetCalibre DRCDRC Results DatabaseASCII ReportCorrect Layout ErrorsLocate Errors Using Calibre RVE and Layout

4、 Tool23 DRC Runset File 1 基本控制,原有DRACULA的file可以用drac_cvt sourcefile targetfile命令来转换。(1)Calibre是一个“EdgeBased”Tool,默认错误的显示是边Error is between these edges(2)DRC 检查的结果有三种控制 Euclidean(default)、Square、Opposite。(3)常用的几条检查规则,具体可阅读Calibre的手册(a) Internal(内边对内边)用来检查 Width、Overlap;(b) External(外边对外边)用来检查 Space、N

5、otch;(c) Enclosure(内边对外边) 2 一般的DRC检查文件包含以下几个部分:(1) 运行设置,设置GDS的位置,结果文件放的位置等;(2) 层次定义,定义输入的层次;(3) 层次运算,产生运算需要的一些中间层次;(4) 规则检查,具体对每条规则的检查;(5) 选择控制,可以只检查某几条规则或者只检查某个单元。 3一个简单的Rule File,“/”后面为注释 LAYOUT PATH “/home/*.” /GDS的路径 LAYOUT PRIMARY “*” /GDS的顶单元名 LAYOUT SYSTEM GDSII /版图数据的格式 DRC MAXIMUM RESULTS 5

6、00 /最大错误输出数目 DRC RESULTS DATABASE “/home/*” /存放DRC错误数据的路径及名称 DRC SUMMARY REPORT “/home/*” HIER /存放DRC简述文件的路径及名称 DRC CELL NAME YES CELL SPACE XFORM /表示底层的错误将直接在底层显示 PRECISION 1000 RESOLUTION 10 /两句合起来表示检查的数据格点为 10/10000.01 FLAG OFFGRID YES /在Summary Report 里显示不在格点上的版图的坐标 FLAG SKEW YES /在Summary Repor

7、t 里显示不是45度线的版图的坐标 FLAG ACUTE YES /在Summary Report 里显示锐角的版图的坐标/输入层次的定义 LAYER nwelli 1 LAYER ndiffi 2 LAYER pdiffi 3/TEXT层及连接性的定义TEXT LAYER 60 ATTACH 60 met1TEXT LAYER 70 ATTACH 70 met2/定义连接CONNECT met1 poly1 BY contCONNECT met1 ndiff BY contCONNECT met1 pdiff BY contCONNECT met2 met1 BY via1CONNECT m

8、et1 allnsub BY contSCONNECT allnsub nwelli/顶层数据的定义,有利于提高检查速度LAYOUT TOP LAYER pad met2 via1 /层次的运算 fpoly = poly1 INTERACT celiso tpoly = poly1 NOT INTERACT celiso pcode = SIZE pcodei BY 0.15 OVERUNDER/一般用来层次运算用的命令大概有:INTERACT 表示有任何重合关系的,/相当于DRACULA的OVERLAP。NOT ,AND,OR,SIZE 同DRACULA。SIZE 后面/加上UNDEROVE

9、R 表示先缩小再放大,OVERUNDER表示先放大再缩小。/wmet1 = WITH WIDTH met1 =10 表示找出宽度大于等于10的铝。/具体的规则检查/FLAG CHECKacute_chk /acute_chk表示这个错误的名称,随便定义 flag acute yes /开头表示注释会在RVE的注释窗口里显示 DRAWN ACUTE /每条检查必须包含一条可以输出错误的命令 /一对花括号表示执行一条规则检查/上面这条规则检查的目的是在版图上直接显示锐角的地方。offgrid_chk flag offgrid yes DRAWN OFFGRID /直接在版图上显示不在格点上的地方s

10、kew_chk flag skew yes DRAWN SKEW/ 直接在版图上显示非45度线的地方/ well checkGROUP nwchk nw_chk? /?是一个通配符,这句语句是将所有以nw_chk开头的错/误定义成一个名称为nwchk的集合。可以通过 /DRC SELECT CHECK nwchk 这个语句来控制DRC检查/只检查这个集合,也可UNSELECT去掉这个集合。nw_chk1 nwell width must =2.5 INT nwelli 2.5 ABUT 90 SINGULAR REGION / N阱的宽度检查,后面的ABUT90 SINGULAR REGION

11、 是secong key words 。 /ABUT=1.4 EXT nwelli 1.4 ABUT=4 EXT nwelli 4 ABUT=0.4 ENC allnsub nwell 0.4 ABUT90 OUTSIDE ALSO SINGULAR REGION/ 阱包nsub不能小于0.4, OUTSIDE ALSO 也是second key words,表示nsub在 / nwell 外也报错。nw_chk5 show bad nwell connect two different net stamp_nwell = STAMP nwell BY allnsub nwell NOT st

12、amp_nwell/STAMP命令来定义nwell 连接性,并且只能有一个连接,当某个nwell的nsub有两/个或以上的不同线名时,这个nwell不会被选成stamp_nwell。没有nsub的阱也不会被/选出来。/关于有源区及多晶硅,铝等层次的检查可参考nwell的设置。/contact checkcont_chk1 min&max contact size 0.50.5 NOT RECTANGLE cont 0.5 BY = =0.5 ORTHOGONAL ONLY/表示contact只能这么大,并且每条边必须都平行与X或Y轴。/密度检查 den_chk1 min met1 densit

13、y is 30% DENSITY met1 Layout , 这里可以设置调用的版图工具。具体配置方法见在线帮助中Calibre 与其他工具的接口。在Cadence的Virtuoso 中集成了Calibre 以后,Virtuoso 的菜单中会多出Calibre 的菜单,如:即可以直接从Virtuoso 中调用图形化的DRC, LVS 和RVE,显得十分方便。点击Start RVE , 选择数据库名称,同样可以得到同图1 一样的界面,这时RVE 已经和版图工具集成在一起,可以在RVE 中点击一些错误坐标,Virtuoso 中立刻会显示错误的位置,如图3:这里点击M1 小于最小面积的错误中的第1

14、个错误点:右边坐标红色下划线的(-1.96 ,3.97 ) , 在版图工具中会立刻高亮显示位置,如图4:因此改错起来十分方便。可以在RVE 菜单View By Check , RVE 左边会显示出Check 每条rule 的结果,见图5:绿色的表示检查该rule 无误。而且利用File 菜单中可以方便地打开DRC 结果报告、DRC Runset 等,如图6:第三章 Calibre LVS31数据准备需要的数据为版图数据、电路图数据和runset 文件。Calibre 把电路图网表的部分叫SOURCE。SOURCE 部分要求的网表格式为标准spice 格式或者Calibre自身的一种类似spic

15、e 的格式。Calibre 有一种把verilog 转为自身类spice 格式的功能,叫v2lvs,下面先介绍v2lvs:v2lvs 能够把verilog 网表和相对应的spice 库、verilog 子库转成Calibre LVS 用到的电路图SOURCE 网表,其功能如图:转换的原理是verilog 网表根据verilog 子库对元件端口的定义,去spice 子库找同样名称和端口的元件,然后进行网表和格式上的替换。因此v2lvs 转类spice 网表时,需要verilog 网表、spice 库、verilog 子库描述(可选),其命令格式如下:v2lvs v verilog_file o

16、spice_like_file -l verilog_lib_file -lsp spice_lib_file-lsr spice_lib_file -s spice_lib_file -s0 groundnet -s1 powernet -sk -i-v 后面接verilog 文件名称;-o 为输出类spice 格式文件;-l 是verilog 子库描述;-lsp接spice 库网表,p 是pin 模式,即不允许有数组类的verilog 端口(比如PA3、PA2、PA1、PA0)出现;-lsr 与-lsp 意义同,不过pin 是range 模式,即可以接受verilog的数组端口;与-lsp

17、,-lsr 不同的是,-s 是只是让转出文件在前面INCLUDE 这些spice子库,而不会读它们;-s0 , -s1 为对verilog 中1b0, 1b1 的电源网络取代;-sk 指允许多组复合电源,不仅仅是一对全局电源VDD,VSS;-i 指输出文件采用spice 通用的pin 格式,没有$引导,便于仿真。常见的例子如下:v2lvs v top_design.hv o top_design.sp s0 VSS s1 VDD sk l pll_risc.v -l cache_core.v l pad.v l std.v -lsr pll_risc.sp lsr cache_try_new.

18、splsp std.sp -lsp pad.sp -s pll_risc.sp s cache_try_new.sp s std.sp s pad.sp根据几个子模块的情况,转出整个芯片的LVS 网表。实际上,verilog 子库并不是都需要的,v2lvs 在转spice 网表的时候,是根据verilog 子库中元件端口和spice 子库中的元件端口名称对应关系来转的。如果在verilog 网表中没有数组端口,则该元件端口名称在spice 子库网表中元件的端口名称中也是唯一的标识,因此不会转错。但是对于数组端口(如PA31:0),如果没有verilog 子库对模块的端口定义,v2lvs 按照缺

19、省的从高位到低位的方式转出端口对应关系,因此会出错。因此对于有数组端口的verilog 网表,一定要求有verilog子库网表。上面的例子可以简化为:v2lvs v top_design.hv o top_design.sp s0 VSS s1 VDD sk -lpll_risc.v l cache_core.v -lsr pll_ric.sp -lsr cache_try_new.sp -lspstd.sp lsp pad.sp -s pll_risc.sp s cache_try_new.sp s std.sp spad.sp32 LVS 流程 从下面的流程中可看出,Calibre LVS

20、都先把版图提取出SPICE格式的网表来,实际上Calibre LVS比对的是两个SPICE网表。Completed LayoutRule FileCompleted Source Calibre LVSLVS Results DatabaseASCII ReportExtracted netlistCorrect Layout ErrorsLocate Errors using Calibre RVE and Layout ToolDetermine Errors from Report33一个简单的LVS Runset文件/ 注释LAYOUT PATH “/home/*” /版图数据的路径及

21、名称LAYOUT PRIMARY “*” /版图的顶单元名LAYOUT SYSTEM GDSII /版图数据的格式SOURCE PATH “/home/*” /逻辑网表的路径及名称SOURCE PRIMARY “*” /顶层逻辑名SOURCE SYSTEM SPICE /逻辑网表的格式LVS REPORT “/home/*” /LVS Report的路径及名称LVS REPORT OPTION S /显示软连接的冲突PRECISION 1000RESOLUTION 10 /格点为0.01UNIT CAPACITANCE FFUNIT RESISTANCE OHMUNIT LENGTH U /定

22、义文件里电容、电阻、长度的单位LVS POWER NAME “?VDD?” “?vdd?” “?VCC?” “?vcc?” /定义电源 ?为通配符LVS GROUND NAME “?GND?” “?gnd?” “?VSS?” “?vss?”/定义地TEXT DEPTH PRIMARY / 定义只认顶层的TEXT,用ALL表示认识所有的TEXTVIRTUAL CONNECT COLON YES/定义允许用名字的虚拟连接LVS ABORT ON SUPPLY ERROR YES /电源地短路就中断LVS,要检查短路才设为NOLVS ISOLATE SHORTS NO /发现电源地短路时改为YES,

23、因为它需要很长时间LVS IGNORE PORTS NO /不忽略PORTSLVS CHECK PORT NAMES YES /比PORTS的名字LVS RECOGNIZE GATES ALL/ 同上面图形界面里Gates的设置LVS ALL CAPACITOR PINS SWAPPABLE YES /允许电容两端互换LVS FILTER UNUSED MOS YES /忽略版图里不用的MOS管,下面有详细控制LVS FILTER UNUSED RESISTORS YES /忽略版图里不用的电阻,下面有详细控制LVS FILTER UNUSEDC CAPACITORS YES /忽略版图里不用

24、的电容,下面有详细控制LVS FILTER UNUSED OPTION AB RC RE RG YC O/定义哪些器件是不用的器件:AB表示去掉G S D三端连一起的MOS管,RC表示去/两端连一起的电阻,RE表示去掉两端连一起的电容,RG表示去掉两端连一起的二极/管,YC表示去掉三端连一起的三极管,O是过滤的重复设置,一般都加上。LVS REDUCE PARALLEL BIPOLAR YES /将并联的三极管当成一个LVS REDUCE PARALLEL MOS YES /将并联的MOS管当成一个LVS REDUCE PARALLEL DIODES YES /将并联的二极管当成一个LVS R

25、EDUCE PARALLEL CAPACITORS YES /将并联的电容当成一个LVS REDUCE PARALLEL RESISTORS YES /将并联的电阻当成一个LVS REDUCE SERIES RESISTORS YES /将串联的电阻当成一个LVS REDUCE SERIES CAPACITORS YES /将串联的电容当成一个/输入层次定义LAYER nwelli 1LAYER ndiffi 2LAYER pdiffi 3bulk = EXTENT /定义大衬底,EXTENT表示数据的最外框TEXT LAYER 60 ATTACH 60 met1PORT LAYER TEXT

26、 60TEXT LAYER 70 ATTACH 70 met2PORT LAYER TEXT 70 /定义TEXT的连接LAYOUT TOP LAYER padi met3i met2i via2i via1i / 将这些数据当成顶层/层次运算,同DRCndiffx = rlocosi AND nimpi/定义连接,同DRCCONNECT met2 met1 BY via1/器件定义DEVICE MN(N) ngate tpoly tnsd tnsd bulk 0.5 /定义NMOS管,拐角因子为0.5TRACE PROPERTY MN(N) L L 0.1 /比对沟道长度 允许10%的误差T

27、RACE PROPERTY MN(N) W W 0.1/比对沟道宽度 允许10%的误差DEVICE MP(P) tpgate tpoly tpsd tpsd tnwell 0.5 /定义PMOS管,拐角因子为0.5TRACE PROPERTY MP(P) L L 0.1 /比对沟道长度 允许10%的误差TRACE PROPERTY MP(P) W W 0.1 /比对沟道宽度 允许10%的误差DEVICE R(RW) bnwell tnsd tnsd 800 /定义电阻,方块阻值为800OHMTRACE PROPERTY R(RW) R R 0.3 /比对电阻值,允许30的误差DEVICE C(

28、CL) pccap cpo2 tpoly 0.72 0 /定义电容,每平方电容值0.72FF,0表示不计 /算周长效应的电容TRACE PROPERTY C(CL) C C 0.3 /比对电容值,允许30的误差DEVICE Q(PL) TRImk coll base emit /定义三极管DEVICE D(DN) ndiomk bulk tndio / 定义二极管TRACE PROPERTY D(DN) A A 0.3 /比对二极管的面积,允许30的误差/ERC CHECK 部分LVS SOFTCHK tnwell CONTACTLVS SOFTCHK bulk CONTACTERC PATH

29、CHK GROUND& !POWERERC PATHCHK POWER& !GROUNDERC PATHCHK !POWER&!GROUNDERC PATHCHK !LABELEDpsub_to_power NET psub “?VDD?” “?vdd?” “?VCC?” “?vcc?”nsub_to_ground NET nsub “?VSS?” “?vss?” “?GND?” “?gnd?”34 Runset文件里器件的定义器件定义的一般格式 DEVICE element_name (model_name) device_layer pin_layer property_spectific

30、ationExample: Property SpecificationBulk pin layerDrain pin layerSource pin layerGate pin layerDEV MP(P) GATE POLY(G) SRC(S) DRN(D) NWELL(B) 0.5Device layerModel_nameElement_nameElement nameDefinitionPin namesDefault Properties for TracingParameters forProperty SpecificationMNMPMDMEMOSTransistorG(ga

31、te) 1st pin layerS(source) 2nd pin layerD(drain) 3rd pin layerB(bulk) 4th pin layer is optionalWidthLengthEffective_width_factor(weffect)DDiodePOS(+pin) 1st pin layerNEG(-pin)2nd pin layerSUB(substrate)3rd pin layer is optionalArea PerimeterCCapacitorPOS 1st pin layerNEG 2nd pin layerSUB 3rd pin lay

32、er is optionalCapacitanceArea_capPerim_capRResistorPOS 1st pin layerNEG 2nd pin layerSUB 3rd pin layer is optionalResistanceresistivityQBipolarTransistorC(coll) 1st pin layerB(base) 2nd pin layerE(emit) 3rd pin layerSUB 4th pin layer is optionalNONE35用commond line 来运行Calibre LVS检查(1)先必须有一个完整的规则检查文件,

33、必须包含运行设置、层次定义、层次运算、器件定义等几部分。(2)建一个批处理命令比如叫run_lvs,内容为! /bin/csh frm r /home/*/svdbcalibre lvs hier spice /home/*/svdb/topcell.sp hcell hcell_file rule_file |tee lvs.log/假如没有hcell_filecalibre lvs hier spice /home/*/svdb/topcell.sp auto rule_file |tee lvs.log(3)前面rm的目的是每次清空LVS Database目录,命令中topcell 为版

34、图的顶层单元名。(5) 然后每次运行这个批处理命令就可以了,在Unix命令行下输入 ./run_lvs命令就可。运行完后可以到存放结果文件的目录里看Report File,还可以在版图里用RVE调LVS Database进行Debug(6) hcell_file的格式如下/ 是注释。/Layout cell Name Source cell Name ABC DEF ABC GHI UVW XYZ RST XYZ可见单元名可以1 VS N 或者 N VS 1 ,但是不要出现 M VS N 的情况。36 查看结果文件及改错(1)打开LVS结果文件,下面是个实例:OVERALL COMPARISO

35、N RESULTS INCORRECT Error: Different numbers of nets.Error: Different numbers of instances.Error: Connectivity errors.Error: Instances of different types or subtypes were matched.Error: Property errors.Warning: Unbalanced smashed mosfets were matched.Warning: Ambiguity points were found and resolved

36、 arbitrarily.* CELL SUMMARY *Result Layout SourceINCORRECT TOPCELL TOPCELL可见总的比较结果是不正确,错误有5 种: 不同网络、不同元件个数、连接错误、不同元件类型、属性错误,CELL SUMMARY 里面有Layout 和Source 的TOPCELL 不匹配。然后直接翻页到文件的后面,看到INFORMATION AND WARNINGS 栏:INFORMATION AND WARNINGS这里列出了匹配的统计情况(同dracula lvspr.lvs 的最后),可以看见SOURCE 和LAYOUT 匹配了多少,各有多少

37、没有匹配,错在哪种单元上面等,这里可以看出共有10 个layout 单元和16 个source 单元没有匹配。下面是管子等删减的情况统计:o Statistics:310940 layout mos transistors were reduced to 94596. 24286 connecting nets weredeleted.171921 mos transistors were deleted by parallel reduction.16 mos transistors and 16 connecting nets were deleted by series reductio

38、n.44407 mos transistors and 24270 connecting nets were deleted by split-gatereduction.106383 source mos transistors were reduced to 28181. 22460 connecting nets weredeleted.36983 mos transistors were deleted by parallel reduction.16 mos transistors and 16 connecting nets were deleted by series reduc

39、tion.41203 mos transistors and 22444 connecting nets were deleted by split-gatereduction.20 series/parallel layout resistors were reduced to 6. 8 connecting nets weredeleted.141 unused layout mos transistors were deleted.141 unused source mos transistors were deleted.2 unused layout resistors were d

40、eleted.47 nets were matched arbitrarily.下面是顶层端口对应情况,这个很重要:Initial Correspondence Points:Ports: vdd VDD33 SAVDD VSS VSSD SAVSS EB_RDVAL EB_WDRDY EB_RBERR EB_WBERR SI_NMISI_INT5 SI_INT4 SI_INT3 SI_INT2 SI_INT1 SI_INT0 SI_ENDIANSI_COLDRESET EB_ARDY SI_RESET EJ_DINTSUP EJ_DINT CACHE_CE TRST TMS TCK TDIS

41、I_ERL SI_EXL SI_RP SI_CLKOUT SI_SLEEP SI_TIMERINT EB_AVALID EXT_CLKEXT_CLKEN EB_INSTR EB_WRITE EB_BURST EB_BFIRST EB_BLAST EJ_DEBUGMEB_BE3 EB_BE2 EB_BE1 EB_BE0 FREF PLL_TEST SI_PLLCLK如果Ports 部分没有出现顶层模块的所有端口, 则肯定会导致整个比较的失败,因此如果端口方面信息错误的话, 应该去查一下版图抽取的时候是否出了问题,可以去看TOPCELL.sp 和TOPCELL.rep.ext。注意: Ports

42、报告的数目和LVS ReportMAXIMUM number 的设置数据有关,最好使number 大于顶层的端口数目。下面是具体详细的连接信息。如果发现端口基本正确,可以直接到文件的前面看详细的Error 信息。CELL SUMMARY 下面是LVS PARAMETERS 部分,即回放LVS 比较的所有选项设置:看TOPCELL.rep 的方法是:先看OVERALL COMPARISON RESULTS,看总体比较是否正确,如果不对,看错误的类型;然后去文件后面看INFORMATION AND WARNINGS , 看具体元器件匹配的情况, 尤其是下面的Initial Corresponden

43、ce Points Ports 中顶层端口匹配的情况,如果端口没有匹配好,去查版图抽取的情况;如果出现很多大量的管子不匹配,请检查电源网络是否有开路,短路现象,同时可以设置LVS Recongnize gates 和LVS Reduce split gates 为yes 再试一次(即允许pin 交换和删减复杂门);最后可以回到文件开头看INITIAL NUMBERS OF OBJECTS 和NUMBERS OF OBJECTS AFTER TRANSFORMATION , 以及具体的INCORRECT NETS , INCORRECT INSTANCES,PROPERTY ERRORS 信息,在版图和电路图上找到相对应的地方进行检查。注意:对于短路现象,则Layout 中的网络数目必然少于Source 中的,并且出现Layout 中几个网络对应与Source 中的一个网络的信息;对于开路,Layout 中的网络数目必然大于Sour

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

相关资源

更多 1999年06月大学英语六级(CET-6)真题试卷(含答案)

1999年06月大学英语六级(CET-6)真题试卷(含答案)

2010-2011学年八年级生物第一学期第二次阶段测试 苏教版

2010-2011学年八年级生物第一学期第二次阶段测试 苏教版

七年级英语上册 Unit 1 My name’s Gina Self Check习题 (新版)人教新目标版

七年级英语上册 Unit 1 My name’s Gina Self Check习题 (新版)人教新目标版

八年级道德与法治上册 第一单元 做人之本 1.1 自尊自爱 第二框《知耻才能自尊自爱》课件 粤教版

八年级道德与法治上册 第一单元 做人之本 1.1 自尊自爱 第二框《知耻才能自尊自爱》课件 粤教版

万科深圳区域公司三年经营计划21P(共21页)

万科深圳区域公司三年经营计划21P(共21页)

四年级语文上册 6.2 出塞课件2 长版

四年级语文上册 6.2 出塞课件2 长版

政治第十六单元 认识社会与价值选择 第40课时 寻觅社会的真谛 新人教版必修4

政治第十六单元 认识社会与价值选择 第40课时 寻觅社会的真谛 新人教版必修4

中考复习阶段性学业水平检测(九)(DOC)

中考复习阶段性学业水平检测(九)(DOC)

第6章企业对东的伦理义务

第6章企业对东的伦理义务

世界海洋油气勘探开发技术及装备的现状与展望-国际船舶网

世界海洋油气勘探开发技术及装备的现状与展望-国际船舶网