车载数控音频转发器本科毕业设计

车载数控音频转发器本科毕业设计

《车载数控音频转发器本科毕业设计》由会员分享,可在线阅读,更多相关《车载数控音频转发器本科毕业设计(49页珍藏版)》请在装配图网上搜索。

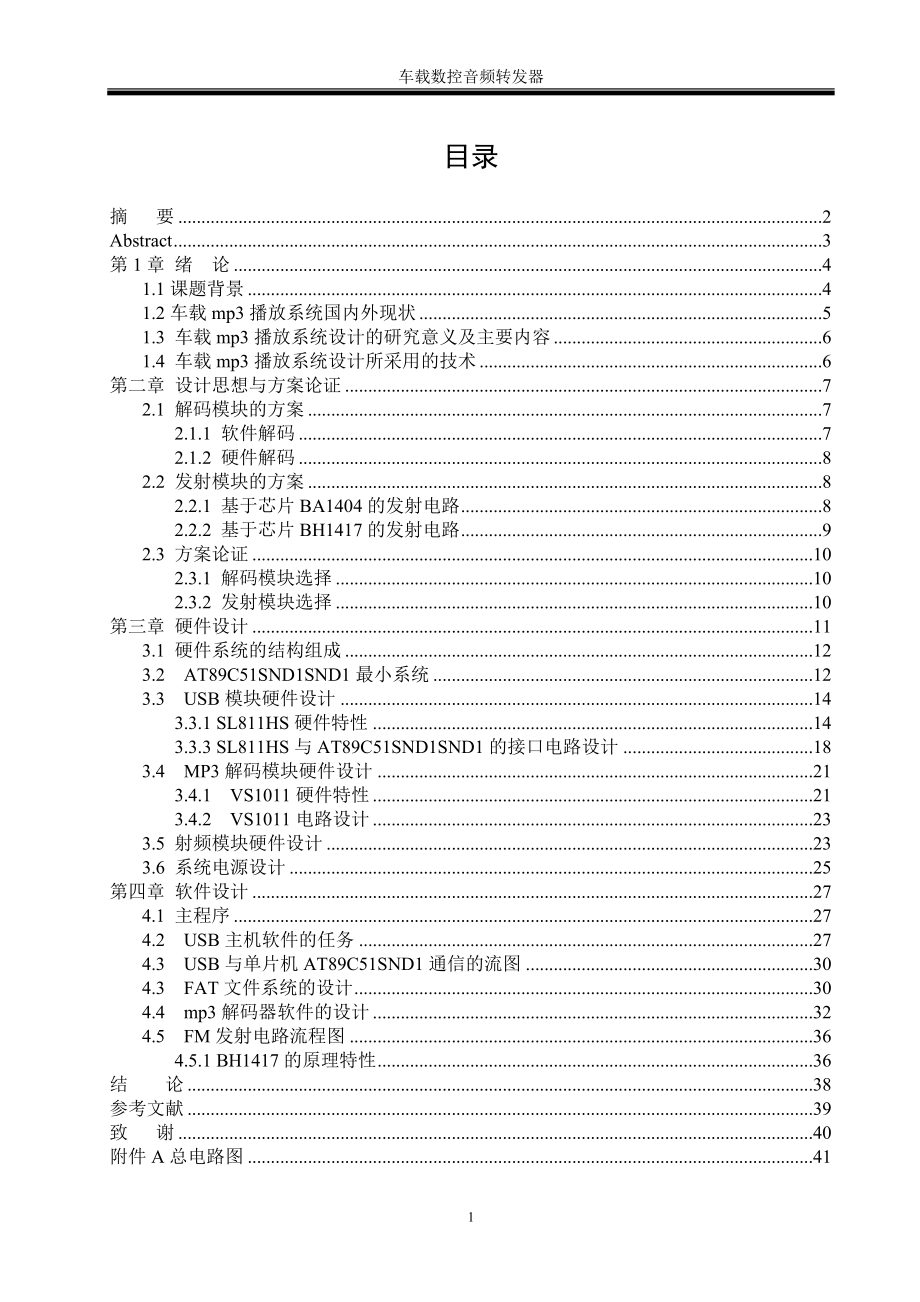

1、车载数控音频转发器目录摘 要2Abstract3第1章 绪 论41.1课题背景41.2车载mp3播放系统国内外现状51.3 车载mp3播放系统设计的研究意义及主要内容61.4 车载mp3播放系统设计所采用的技术6第二章 设计思想与方案论证72.1 解码模块的方案72.1.1 软件解码72.1.2 硬件解码82.2 发射模块的方案82.2.1 基于芯片BA1404的发射电路82.2.2 基于芯片BH1417的发射电路92.3 方案论证102.3.1 解码模块选择102.3.2 发射模块选择10第三章 硬件设计113.1 硬件系统的结构组成123.2 AT89C51SND1SND1最小系统123.

2、3 USB模块硬件设计143.3.1 SL811HS硬件特性143.3.3 SL811HS与AT89C51SND1SND1的接口电路设计183.4 MP3解码模块硬件设计213.4.1 VS1011硬件特性213.4.2 VS1011电路设计233.5 射频模块硬件设计233.6 系统电源设计25第四章 软件设计274.1 主程序274.2 USB主机软件的任务274.3 USB与单片机AT89C51SND1通信的流图304.3 FAT文件系统的设计304.4 mp3解码器软件的设计324.5 FM发射电路流程图364.5.1 BH1417的原理特性36结 论38参考文献39致 谢40附件A总

3、电路图41附件B主程序42摘 要 随着数字信息技术以及网络技术的高速发展,汽车的自动化、智能化和网络化也被相应地提上了口程。而车载播放系统作为汽车的一个不可分割的部分也必然面临着新的技术革新。本文根据设计要求以及目前车载播放器的特点,提出了一种车载MP3播放系统的设案。 本论文基于微控制器系统的软硬件设计与调试,以及系统集成调试成功的基础上,完成了车载MP3的系统设计。通过控制驱动芯片SL811HST,按照USB1.1协议,AT89C51SND1的固件程序完成了对U盘的枚举,FAT文件的管理,MP3文件的识别,对MP3音频流进行解码变成音频信号,再进行数、模转换 。 系统主要包括4大模块:控制

4、模块,数字音频处理模块,发射模块,接收模块。整个系统围绕带有解码器的AT89C 51进行设计。数字音频处理模块采用了嵌入式的USB控制器SL811 HS和AT89C51SND1控制器。发射模块采用BH1417。接收模块采用的CXA1019S来玩成。关键词 USB主机;FAT文件系统;MP3解码;单片机AT89C51SND1 AbstractWith the rapid development of digital information technology and network technology, automation, intelligent and network of the c

5、ar were brought forward in the mouth. The car player system as an inseparable part of the car will also face the technical innovation. According to the design request and the characteristic of car player, put forward a kind of car MP3 player system set case.In this paper, the hardware and software d

6、esign and debugging microcontroller based system, as well as the basis of system integration and debugging success, completed the system design of vehicle MP3. The control chip SL811HST, according to USB1.1 protocol, AT89C51SND1 firmware program complete enumeration of U disk, FAT file management, i

7、dentification of MP3 files, into audio signal of MP3 audio stream, then the number, mode conversion.The system consists of 3 modules: control module, digital audio processing module, transmitter module, receiver module. The whole system is designed around 51 with a AT89C decoder. Digital audio proce

8、ssing module using the embedded USB controller HS and AT89C51SND1 controller SL811. Transmitter module using BH1417. The receiving module uses CXA1019S to play into the. keyword USB host; FAT file system; MP3 decoding; single chip microcomputer AT89C51SND1第1章 绪 论1.1课题背景在当前数字信息技术和网络技术高速发展的时代,嵌入式系统己经广

9、泛地渗透到科学研究、工程设计、军事技术、各类产业和商业文化艺术以及人们的口常生活等方方面面中。随着国内外各种嵌入式产品的进一步开发和推广,嵌入式技术越来越和人们的生活紧密结合。目前,嵌入式技术己经成为通信和消费类产品的共同发展方。嵌入式系统几乎包括了生活中的所有电器设备,如掌上PDA、移动计算设备、数字电视机顶盒、多媒体、汽车、电梯、冰箱、自动取款机、手机等等。与此同时,近几年来,随着我国汽车工业的迅速发展,汽车电子产业也快速地成长起来,成为汽车市场发展的重要动力。目前的汽车电子产品主要包括安全系统、网络系统和信息娱乐系统三大类,其中以信息娱乐系统涉及的技术最为复杂,功能也最为丰富,能够直接面

10、对用户,为他们带来视听享受和资讯便利,这个也是汽车技术革命最重要的内容。车载音乐播放系统作为汽车的一个不可分割的部分也必然面临着新的技术革命,将网上的数字音乐直接与汽车音响连在一起己经成为车载音响发展的必然趋势。本文所研究的内容,就是设计一种车载音乐播放系统,能通过USB接口将大容量存储设备中的MP3等格式的文件读取并解码进过D/A转换,最后利用车载调频接收机播放出来。1.2车载mp3播放系统国内外现状 在我国,国产车的音响配置一般较低,普通汽车一般只装配收音机、卡带机,汽车音响音质可想而知。高品质的汽车音响固然很好,但是其高昂的价格却也令不少人望而却步,这是高性能汽车音响难以普及的重要原因。

11、不少国内汽车生产厂家,为了适应市场变化的需求,在设计方面也做了许多改进:从先前的收音机变化为带磁带的收音机,又变化成单碟CD收音机和多碟CD,磁带收音机,以至发展到CD, VCD, DVD,多碟CD,磁带收音机为一体的车载娱乐系统。现有的各种车载播放系统大致特点如下 磁带播放器历史最长,不过车载磁带音响会由于传动机械而出现绞带现象,音质不好,在中高端汽车上己基本淘汰了,但由于其低成本的原因在低端车载音响系统中还有使用。 车载CD播放系统较磁带播放系统己经在音质方面有了很大的提高,但是该类播放系统只能读取CD格式、MP3格式的CD光盘,不能随时更新内容,因而使用起来还是有些不方便。 DVD是采用

12、MPEG2标准压缩的全数字影音光碟,它有大容量、高品质、高画质的特点,但是高昂的价格阻碍这种产品在汽车市场上广泛应用。 在国外,美国Visteon公司生产的基于硬盘机的MACH MP3播放系统,采用PC机控制器做播放器,用硬盘做数字音乐存储器。好处是一次可以存放1000多首MP3音乐。缺点是体积大,系统复杂,灵活性差,价格高。韩国DUAL公司推出的MP3播放机转换器。该公司设计的磁带式MP3播放器外形做得和磁带完全一样,其结构也和磁带非常的相似,有和磁带相同的马达传送轮,并且是可以转动的,而且还有一个磁头,如果将它放到磁带随身听里,它的磁头可以直接接触到磁带随身听的磁头。该播放器的优点是传输速

13、度快,但该产品的缺点在于:将数字化网络音乐通过卡式磁带机的磁头读取之后,在数模转换过程中信号损失大,音效下降很多,抗震性也不好。1.3 车载mp3播放系统设计的研究意义及主要内容本系统作为车载多媒体的一个课题,充分利用了微控制器的内部资源,主要负责MP3文件播放和收音机播放的任务。专门的车载数字音频产品,也大量出现,如CD, VCD, DVD等设备。但是,它们仍然具有很大的局限性。例如,CD, VCD, DVD都是通过光盘来存储信息,它们的存储介质是光存储器,保存非常不方便,选择内容有很大的局限性,抗震性特别差。另外,VCD和DVD的激光探测头易劳损,有机械寿命。基于以上车载多媒体的众多不足指

14、出。在使用了国外技术成熟的高性能、高集成度、低成本的双CPU基础之上,设计出了车载MP3系统。在国内,车载MP3是一个新事 具有以下独特的优越性。(一)存储介质好,使用U盘。存储介质为高密度、非易失性的读/写闪存存储器。存储容量大;(二)MP3节目源;内容完全自己选择;(三)抗震性好;寿命长; 技术难点:(一)合理地选择元器件,硬件的设计;(二)保证音质效果;电子防震功能,抗震性好(三)掉电存储功能,现场保护功能,物,处于开发阶段,但其前景肯定是美好的。(四)程序的编写、调试;(五)系统的功能实现。1.4 车载mp3播放系统设计所采用的技术根据上述技术要求,结合实际情况,对车载MP3的系统设计

15、采取如下所述的研究方法和技术路线。CPU是智能仪器仪表系统的灵魂。智能仪器仪表系统的整体性能在很大程度上取决于CPU的先进性和灵活性。就车载MP3的系统设计而言,整个系统以片机为核心来开发,系统的3个大模块:控制模块,发射模块,调频接收模块都是通过单片机控制完成的。因为随着半导体、单片机技术的发展,陆续出现了不少增强型的CPU,高档的单片机层出不穷,特别是随着微电子技术和超大规模集成电路技术的发展,单片微型计算机以其速度快、体积小、性价比高、功能强、可靠性高等独有的特点,在各个领域(如工业控制、家电产品、汽车电子、汽车多媒体、通信、智能仪器仪表)得到了广泛的应用,相关技术也越来越成熟,片内集成

16、了高精度ADC和DAC,片内大容量闪速/电擦除程序存储器,看门狗定时器(WDT ),电源监视器(PSM), UART, I2C、和SPI串行I/O接口。这些单片机的性能不仅在上述方面大大增加,在处理速度上也有了极大提高,有的还支持浮点数处理,功耗相对于用传统方法设计的系统也大大降低。当前,用在控制方面的单片机技术无论是在硬件上还是软件上都有许多成熟的经验可以借鉴,使得单片机控制系统的开发周期不断缩短,开发出的系统也更加可靠。相应的,与单片机配套的外围设备的性能也有了长足的进步。基于上述原因,车载MP3的系统设计采用单片机控制器。USB控制器芯片完成对U盘的检测,MP3文件的识别。MP3文件的解

17、码,音频信号的输出。围绕一个单片机扩展相应的外围电路,完成了从数据传输和数据转换到各个控制电路的软硬件设计。然后再结合项目的整体要求,编制与硬件电路相对应的软件程序。第二章 设计思想与方案论证本设计牵涉到车载MP3的解码模块和立体声调频发射模块,接收模块,该设计的关键之处主要在于芯片的选择以及电路的搭配。2.1 解码模块的方案2.1.1 软件解码软件解码就是通过相应的程序来解码,最终解码工作交给CPU完成。基于程序系统的MP3解码流程图如图2.1所示。尺度因子解码哈夫曼信息解码同步及差错检查哈夫曼解码逆量化重排序立体声解码混淆缩减混淆缩减频率反转频率反转IMDCTIMDCT合成多相滤波合成多相

18、滤波右声道PCM左声道PCM图2.1 MP3软件解码流程比特流2.1.2 硬件解码就是在某个芯片上有一套专门的算法对文件进行解码,不占用CPU太多资源。这种解码方式只能解固定的文件类型,但是它的效率比软件解码的效率高很多。在硬件解码中,不同的芯片集成的解码功能也不尽相同,解码芯片的选择也同样关乎该设计: 飞利浦公司生产的解码双芯片PNX0101ET,该芯片音质好、功能强而且稳定,是高端机的首选,有MP3编码功能。但是其低音量感较足、中音表现出色、而高音则一般,而且成本较高。 韩国产的TCC730解码芯片从功能、性能、音质各方面来看都不错,低音感充足、各频段表现比较平衡、而且音场更为宽阔。但是需

19、要外接ROM,外围元件比较多,应用比较复杂。 VS1011产自于芬兰VSLI公司,是DSP核的单芯片音乐解码芯片,集成解码、DA转换和放大功能。2.2 发射模块的方案2.2.1 基于芯片BA1404的发射电路BA1404是日本ROHM公司出品的一款立体声调频发射专用芯片,它弥补了过去用分立元件来设计调频电路的不足,而且具有立体声调制的功能。基于BA1404的发射电路框图如图2.2所示。直流平衡LC振荡电路Li音频旁电路RiOUT混频网络BA1404图2 .2 BA1404放射电路框该发射电路简单清晰,但是它的高频振荡是电容三点式振荡器,频率稳定性差,容易跑频,无PLL锁相环稳频,有频率漂移而且

20、BA1404所需的38KHz的专用晶振较少。2.2.2 基于芯片BH1417的发射电路BH1417是一个最简单而又实用的集成电路,其电路框图如图2.3所示。它集锁相环电路、立体声编码电路、发送电路,外围加上几个器件就可以组成一台高频定多频点的调频立体声发送器。而且它设置了预加重电路、限幅电路及低通滤波器,可明显地改善音质,其总谐波失真达到了0.3%,立体声分离度为40dB,RF输出电平为100 dB。基于BH1417的FM发射电路框图如图2.3。 低通滤波预加重BH1417导频信号调整限幅电路低通滤波预加重滤波器端口键控晶振放大VCO射频输出锁频信号合成信号图2.3 基于BH1417的FM发射

21、电路框图该电路将预加重电路、限幅电路、低通滤波电路一体化,使音频信号的质量得到保证,采用了锁相环锁频与调频发射电路一体化,发射的频率非常稳定,而且可通过键控部分进行频率设定,使用非常方便。2.3 方案论证2.3.1 解码模块选择软件解码占用太多的CPU资源,解码效率较低。硬件解码则相反,解码效率高,容易实现。所以选用硬件解码,解码芯片采用VS1011较为合适。VS1011是DSP核的单芯片音乐解码芯片,集成解码、DA转换和放大功能。2.3.2 发射模块选择BA1404的高频振荡是电容三点式振荡器,频率稳定性差,容易跑频,但组成的发射电路清晰,BA1404所需的38KHz的专业晶振较少。采用低电

22、压、低功耗设计,两声道分离度高。BH1417将预加重电路、限幅电路、低通滤波电路(LPF)一体化,使音频信号的质量比分立元件的电路(如BA1404, NJM2035等)有很大改进。采用锁相环锁频,并与调频发射电路一体化,使得发射的频率非常稳定。采用了4位拔码开关进行频率设定,可设定14个频点,使用非常方便。比较上述两种方案,采用BH1417为主的立体声FM射频模块的优越性显而易见,故本设计选用BH1417为解码芯片方案。第三章 硬件设计3.1 硬件系统的结构组成单片机本系统采用单片机AT89C51SND1, USB硬件模块、MP3硬件解码模块,这个车载播放系统。使用单片机AT89C51SND1

23、控制USB主控制器来实现USB主机部分,读取USB存储设备内部的音乐文件发送到MP3解码芯片。解码后得到的模拟信号通过立体声发射芯片发射出去。利用调频接收机设备就可以接收信号,实现播放。硬件的总体设计方案如图3.1。USB硬件模块Mp3解码模块发射模块图3.1 系统总体框图3.2 AT89C51SND1SND1最小系统图3.2 AT89C51SND1SND1的功能结构图基于8位C51 MCU核(最大时钟频率20MHz) 。内置2304字节RAM。64K字节FLASH程序空I句:FLASH:AT$9C51 SND1 。4K字节引导闪存(AT89C51SND1 SND 1):在系统编程:通过USB

24、 ,UART和其他存储卡。USB 1.1控制器:”Full speed”,数据传输。内置锁相环:提供MP3,音频时钟;USB时钟。兼容Mufti-Media Card (MMC)卡接口。兼容Atmel Data Flash SPI接口。兼容IDE/ATAPI(硬盘)接口。通道10位AD转换器,8KHz(8位真有效值):电池电压监视;软件控制的录音。超过44个可用的通用I/O口:4位可中断的键盘口,可组成4xn矩阵键盘;软件编程的Smart-media接口。两个标准的16位的定时/记数器。硬件看门狗。带有波特率发生器的标准通用异步串口。主从I2C控制器。主从SPI控制器。电源管理模块:上位复位;

25、软件可编程MCU时钟;空闲、掉电模式。工作范围:在250C,3V士10%,典型操作时消耗电流25mA;工作温度范围-40oC+85oC。AT89C51SND1SND1的功能结构图如图3.2所示。AT89C51SND1 SNDI芯片内具有2KBRAM,64KBFlash程序存储器,支持通过USB接口在线下载固件,因此其最小系统设计是很关键的。以下AT89C51SND1 SND1最小系统设计图3.3,一下面就以步骤来说明其设计过程。第1步系统电源连接将微控制器芯片AT89C51SND1 SNDI的电源信号引脚AVDD、VDD、PVDD和UVDD接至3.3V,而将VSS,AVSS,PVSS和UVSS

26、接至GND,为了在芯片的电源入口处去耦,增加抗干扰能力,在电源和地之间接电容。第2步时钟电路在AT89C51SND1 SND1芯片资料中有对时钟信号的描述,并给出了晶振连接的典型电路。设计AT89CS1SND1的晶体振荡器为11.0592MHz第3步PLL滤波电路根据芯片资料,给出了PLL滤波连接电路。第4步复位电路复位电路如图所示。第5步USB接口部分电路USB接口电路中,除了根据USB1.1协议的要求,要在D+, D-上串联27电阻,并在D+上接一个1.5K的上拉电阻。图3.3 AT89C51SND1SND1最小系统电路图3.3 USB模块硬件设计3.3.1 SL811HS硬件特性Cypr

27、ess公司的SL811HS芯片是一款嵌入式的USB主机/设备控制器,支持USB1.1的全速和低速设备,提供USB主机的硬件接口及总线管理的物理机制,带有在片的SIE和USB发送器以及在片的根集线器Hubo SL811HS在该嵌入式USB主机系统中起到了USB主机控制器的作用。SL811HS芯片的内部结构如图3.4所示。SL811HS实现了USB主机结构中的第一个层次,即USB总线接口层的功能。其主/从控制器正是USB主机结构中的USB主机控制器部分。这里多了个“从”是因为SL811HS也能够作为USB设备的控制器。SIE是用来实现数据并、串转换的任务。处理器接口提供了数据、地址和控制信号线,因

28、而使得SL811HS能够和一般的单片机、DSP等控制器进行通信,并受到CPU的控制。中断控制器通过检测各种USB总线的状态变化,以中断信号的方式报告给外部的核心CPU。图3.4 SL811HS 内部结构图RAM一方面提供了存储数据的缓冲区,另一方面又定义了各种寄存器用于控制SL811HS,并对USB的各种状态进行检测。其实,数据缓冲区也是以寄存器的形式提供给外接CPU的。时钟发生器模块需要外接晶振来为整个SL811HS提供时钟。集成的根Hub提供USB设备的连接点。基于这些功能模块,SL811HS的主要特点如下:1.可作为USB主机或者是设备的接口控制器;2.支持USB1.1协议,提供全速和低

29、速2种USB总线速度方式;3.片上集成了SIE、单端口根Hub, USB收发器和256字节的SRAM ;4. 3.3V工作电压,接口兼容SV电平;5. 硬件自动产生帧起始包SOF和CRCS/16校验。在48引脚封装的芯片上,与系统设计相关的引脚共有28个,其余20个是NC,下面对28个有效引脚作归类说明:1.电源供给引脚,共有6个引脚,分别是1个USB地线引脚USBGnd,2个地线引脚GND, 2个3.3V电源输入引脚VDD, 1个USB收发器模块3.3V电源输入引脚VDD1。2. CPU接口引脚,共有12个引脚,分别是8个数据信号引脚DO-D7,1个写有效信号nWR, 1个读有效信号nRD,

30、1个片选信号nCS,1个地址指针信号A0。3.时钟模块引脚,共有3个引脚,分别是1个时钟输入引脚CLK/X 1, 1个输出引脚X2, 1个时钟模式选择引脚CM。4. USB数据引脚,共有2个引脚,为连接USB数据信号D+的Data+和连接USB数据信号D-的Data- 。5.工作模式引脚,共有1个引脚,即用于选择SL811HS工作在主机或者设备状态的M/S 。6.中断请求引脚,共有1个引脚,即高电平有效的工NTRQo SL811HS用这个引脚来向外部核心CPU请求中断处理。7.系统复位引脚,共有1个引脚,即nRST。8. DMA方式引脚,共有2个引脚,均用在SL811HS作为USB设备控制器的

31、时候。一个是nDACK,用于确定是否采用外接DMA控制器;另一个是nDRQ,用于向外接的 DMA控制器发送请求信号。主机模式下该脚要上拉。表3.1 SL811HS的寄存器表CPU对SL811HS的状态进行检测和控制等的操作都是基于寄存器实现的,因此从硬件的角度来看,系统软件的编程就是对其中一系列寄存器和缓冲区的读/写访问。SL811HS片内带有256字节的RAM,其片内寻址范围为0x00-OxFF。通过接口,CPU可以对这些内容进行访问。其中低地址的16个字节是SL811HS定义的寄存器,而其余的240字节则是存储缓冲区。寄存器分布如表3.1所示。需要说明的是,其中USB-A HOST和USB

32、-B HOST是两套完全并行的寄存器,也就是说它们的功能和结构是完全相同的。比如,EPOXferLen和EP 1 XferLen的功能和使用方法就是完全一样的。之所以这样安排是为了实现“乒乓”的数据处理机制。这种机制,两套寄存器完全可以进行交替的操作,即其中一套正在被配置的时候,另一套就可以进行数据的传输。这样互相交替作用,就可以提高系统处理数据的效率,特别是在控制多个设备的时候。3.3.2 接口芯片SL811HS的外围电路设计在本系统中,采用了嵌入式的USB主从控制器SL811 HS的主动模式,即其引脚M/S为低电平。给SL811HS芯片连接12MHz的晶体振荡器。使用了它的全速模式,即为1

33、2Mbps。它的数据端口(DO至D7)和AT89C51SND1SND1的端口(P0.0至P0.7)提供了一个8位双向数据通道。SL811 HS芯片的D+, D-两根差分式数据信号线与USB插座的D+、D-引脚相连。SL811HS的INTRQ引脚高电平有效,而AT89C51SND1SND1的INTR0引脚低电平有效,在它们之间连接了一个与非门。图3.5 SL811 HS为主动模式的硬件稳定时间配置为USB设备供电,在检测USB设备之前,要为硬件的稳定延长时间为25豪秒为SL811 HS的外围电路设计。SL811HS主动模式的硬件配置设置引脚M/S为低,为主动模式。SL811 HS的晶体振荡器的硬

34、件配置如下:引脚CM接到地,使用的48MHz;引脚CM接到电源,使用的12MHz。与USB HST1插座的连接引脚D+和D-开关下拉电阻为15K与地相连,它们的上拉电阻1.5K悬空即不连接。另外,要为USB连接器的引脚1接上电源。SL811 HS的引脚D+和D-与USB_ HST1的D+和D-之间依次通过两个27欧姆的电阻相连接。SL811 HS主动模式的硬件稳定时间配置为USB设备供电,在检测USB设备之前,要为硬件的稳定延长时间为25豪秒。图3.5 SL811HS的外围电路3.3.3 SL811HS与AT89C51SND1SND1的接口电路设计由于USB接口芯片SL811 HS与单片机AT

35、89C51SND1 SND1的接口电路设计如图3.6所示。所有USB接口芯片与单片机的连接方式基本类似。SL811 HS的数据端口(DO至D7)和AT89C51SND1SND1的端口(P0.0至P0.7 )提供了一个8位双向数据通道。读写信号(nWR和nRD)、片选信号(nCS)、地址/数据选择信号(A0)及其他一些信号。SL811HS的INTRQ引脚高电平有效,而AT89C51SND1的INT0引脚低电平有效,在它们之间连接了一个与非门。因此它们的数据指针为SL811 DATA PORT和地址指针为SL811H_ ADDR_PORT;对SL811 _ADDR_ PORT的操作即为对SL811

36、HS的寄存器操作,对SL811H_ DATA的操作作即为对SL811HS的数据口操作。 图3.6 SL811HS与AT89C51SND1的接口电路 #define SL811_ADDR_PORT 0x0ff00#define SL811_DATA_PORT 0x0ff01unsigned char xdata SL811H _ADDR_at_SL811_ADDR_PORT;unsigned char xdata SL811H_DATA_at_SL811_DATA_PORT;图3.7为SL811HS控制器的读时序图,SL811 HS读出数据的过程是:在nCS上加有效的低电平;在nWR上加有效的低

37、电平;使nRD为高电平;A0上加有效的低电平,写入地址;在芯片的D0D7上加入要写的单元的地址;持续一段时间(10ns);在nCS上加有效的低电平;在nWR上加有效的高电平;使nRD为低电平;A0上加有效的高电平;读出数据;故:相应地址的数据便送到D0D7供读取。图3.7 SL811HS控制器的读时序图图3.8为SL811HS控制器的写时序图。SL811HS写数据的过程是:在nCS上加有效的低电平;在nWR上加有效的低电平;使nRD为高电平;A00上加有效的低电平,写入地址;在芯片的D0D7上加入要写的单元的地址;持续一段时间;在nCS上加有效的低电平;在nWR上加有效的低电平;A0上加有效的

38、高电平;写出数据;故:相应地址的数据便送到D0D7供读取。图3.8 SL811HS控制器的写时序图3.4 MP3解码模块硬件设计本系统采用VS1011硬件解码器实现mp3文件的解码过程,使用硬件解码器实现起来相对比较简单一些,就解码速度而言也比软件解码来得快。3.4.1 VS1011硬件特性VS1011是一个单片的MP3音频解码器,芯片内部含有高性能、低功耗的DSP内核VS DSP4,内有SK的指令RAM和0.5 K的数据RAM。VS1011b内部有一个串行控制和数据输入接口、4个GPIO接口、高性能可变采样率的DAC和一个耳机放大器,如图3.9所示。图3.9 VS1011芯片内部结构图VS1

39、011b通过这个串行输入口接收传送过来的数据流,可以看成是系统的一个设备。输入进来的数据流被解码、通过数字音量控制以后就传输到这个高性能的DAC。通过串行控制线对整个解码过程进行控制,除了最基本的解码,用户还可以通过使用内部RAM来增加一些应用功能。芯片的基本性能参数:1.支持mp3 ,wav音乐文件格式;2.采用12-13MHz或者24-26MHz的时钟;3.可以解码320kbit/s的mp3文件,使用12.0MHz外部时钟(内部倍频器工作的情况下);4.超低功耗、工业级的温度使用范围;5.内置立体声数模转换器;6.立体声耳机功率放大;7.数字电路、模拟电路电压分开;8.串行数据和控制接口;

40、9.5.5kB的片内RAM,可以作为用户的代码和数据存储;10.通过VSKIT可以添加一些自己的功能(软件);11.4位通用I/O口。芯片的应用设计首先了解各引脚的功能及使用注意事项,该芯片共有48个引脚其中有15个脚不连接接(NC),分类如下。1.复位脚:XRESET(低有效);2.片选:XCS(低有效);3.数字电源、地:DGND0,DVDD0,DGND1,DVDD1,DGND2,DGND3, DGND4,DVDD2,TEST(测试用,接数字电源);4.模拟电源、地:AGND0,AVDD0,AGND1, AGND2,AGND3,AVDD1,AVDD2;5.复用引脚:GPIO/DCLK,GP

41、IO/SDATA,XDCS/BSYNC;6.通用I/O:GPIO0,GPIO1;7.与MCU接口:SCLK,SI,SO;8.数据请求输入脚:DREQ;9.音频输出:RIGHT,LEFT;10.晶振:XTALO,XTAL1;其它:GBUF(缓冲地),RCAP(参考滤波电容)芯片内部有16各寄存器,例如模式控制、芯片状态、低音增强等等,用于控制芯片的具体参数。芯片与MCU的接口有两个:SC工(串行命令接口)、SDI(串行数据接口),SCI和SDI各有有一组引脚。但是在VS1011中设置好内部的相关寄存器的相关位以后(SM_SD工NEW=I,SM_SDISHARE=1),它们可以共用一组引脚。XDC

42、S这个引脚就可以不用,SD工和SCI的区分仅仅在于XCS电平的变化,在XCS为高电平的时候为SD工口工作,低电平时为SCI口工作。DREQ引脚为高电平时表示可以输入更多的数据(一般为32个字节),为低电平时表示暂时不要输入数据。3.4.2 VS1011电路设计设置好相应的寄存器以后,就可以按照以下的方式控制解码器的工作了。根据预先选定好的模式,选用相应的引脚。电路图如图3.10所示。芯片使用2.7V的电源,SCI和SD工共用一组接口,通过XCS电平的高低来区分开。需要注意的是,由于9,10,33,34脚在所选用的芯片模式中没有用到,所以要接100K的下来电阻。图3.10 VS1011解码电路图

43、3.5 射频模块硬件设计射频模块的任务就是将解码后的模拟信号以一定的频率发射出去,实现信号在一定范围内的无线传输。该部分的设计采用使用专业级锁相立体声发射芯片ROHM-BH1417,BH1417是一种无线音频传输集成电路,它可以将计算机声卡、游戏机、CD、 MP3、调音台等立体声音频信号进行立体声调制发射传输,配合普通的调频立体声接收机就可实现无线调频立体声传送。适合用于车载MP3的开发生产。图3.11 射频模块电路图这个集成电路是由提高信噪比(s/n)的预加重电路、防止信号过调的限幅电路、控制输入信号频率的低通滤波电路(LPF)、产生立体声复合信号的立体声调制电路、调频发射的锁相环电路(PL

44、L)组成。具有以下特点:1.将预加重电路、限幅电路、低通滤波电路一体化,使音频信号的质量比分立元件的电路由了很大的改进;2.导频方式的立体声调制电路;3.采用了锁相环锁频与调频发射电路一体化,发射的频率非常稳定;4.采用了4位的拨码开关进行频率设定,使用非常方便。通过它来将立体声音频信号进行立体声调制发射传输,配合普通的调频立体声接收机通过汽车音响来输出音乐。该部分设计中,BH1417由硬件来控制发射频频率的,只要控制相应的4个端口就可以调整发射频率了,发射频率分为7个道:87.7Mhz88.9MHz供选择(200Khz为递增单位)。采用开关控制,简易方便,确保在任何地方都能选到一个避开干扰的

45、频道,使用比较简单,如图3.11所示。3.6 系统电源设计电源为系统提供能量,是系统稳定工作的基础。设计电源必须考虑下列因素;输出的电压、电流和功率;输入的电压、电流;电磁兼容和电磁干扰;体积限制;成本和功耗限制。各个器件需要的电源如下:1. AT89C51SND1SND1需要:数字3.3V、模拟3.3V2. SL811HST需要:3.3V3. USB接口需要:5V4. VS1011需要:模拟2.85V、数字2.85V5. BH1417需要:5V所以本系统的设计需要提供以下几组电源:5V,3.3V,2.85V的电源,又由于汽车上的电源是12V,所以可将系统的电源设计分为5V前级电源和由5V转变

46、为具体的末电源。所以系统选用如下电源芯片为系统提供合适的电源。1 .LM2575由于系统在5V上消耗的电流来看,电源系统的前级电路适合采用开关电源,因为可以减少系统的发热量、效率比较高、有比模拟电源更小的体积。但是输出电压波形较大。LM2575是一个开关电源专用模块,具有固定输出电压和可调输出电压两类,芯片最大稳定输出电流可达1A,具有宽输入范围、高效率、温度和电流保护等等。综合考虑选用采用固定输出开关电源芯片LM2575实现该电源的设计。应用设计时,注意以下几点:根据输出电压的档次、最大输入电压、最大负载电流等参数选择电感,可参照相应的电感曲线图来查找所需采用的电感值。其输入电容应大于47u

47、F,并要求尽量靠近电路。输出电容的电容量为100uF470uF,对于本文5V电压输出,应使用耐压值为16V的电容。2. SPX1117系列SPX117系列是一个低功耗正向电压调节器,其可以用在一些高效率、小封装的低功耗设计中。该系列有很低的静态电流在满负载的情况下其低压差仅为1.1V。当输出电流减少时静态电流随负载变化,并提高效率。该系列中有输出电压固定和电压可调两类,本文设计中采用输出电压固定的电压调节器SPX1117M3-2.85、SPX1117M3-3.3来实现电源末级设计。这几种芯片都具有过流及温度保护,一个10uF的输出电容可有效地保证其稳定性。多个同规格的小电容的并联,作用是高频滤

48、波。容的高频性能很差。通常电容越大,其谐振频率越低设计方法。系统电源电路如图所示。因为等电容值的单个大电。所以这部分采用以下的设计方法。系统电源电路如图3.12所示。图3.12 系统电源设计第四章 软件设计4.1 主程序车载mp3播放系统的软件设计包括,嵌入式USB主机软件设计、mp3解码器软件设计、发射模块设计和接收模块设计。主流程图如图4.1所示。开始检测SL811HS状态是否检测到U盘N拔出U盘读取U盘信息Mp3解码初始化程序发射装置广播接收结束图4.1 主程序流图4.2 USB主机软件的任务首先我们把握一下主机软件的主要任务,当一个USB设备接入到主机上之后,主机就根据默认通道对该设备

49、进行枚举(设备地址为0,端点号为0),包括获得该设备的一系列描述符。例如,主机需要获取设备的端点描述符,确认该设备提供了哪些端点,确认端点号和该端点的最大包的尺寸等等。对于USB闪存盘等来说,就是要提供给主机批量输出Bulk Out端点和Bulk In端点的端点号,以及相应的最大包尺寸。然后,主机在后来的批量传输中才能正确地进行一系列操作。要主机识别一个USB设备必须经过枚举的过程,和管理必要的设备状态变化,总线的枚举过程如下:1.设备连接,USB设备接入USB总线;2.设备上电,USB设备可以使用USB总线供电,主机可使用总线枚举来识别也可以使用外部电源供电;3.主机检测到设备,发出复位。设

50、备连接到总线后,主机通过检测设备在总线上的上拉电阻检测到有新设备连接,并确定该设备是全速设备还是低速设备,然后向该端口发送一个复位信号;4.设备默认状态,设备要从总线上接收到一个复位信号后,才可以对总线的处理操作做出响应。设备接收到复位信号后,就使用默认地址(00H)对其进行寻址;5.地址分配,当主机接收到有设备对默认地址(00H)相对应的时候,就对设备分配一个空闲的地址,以后设备就只对该地址进行响应;6.读取USB设备描述符,主机读取USB设备描述符,确认USB设备的属性;7.设备配置,主机依照读取的USB设备描述符来进行配置,如果设备所需的USB资源得以满足,就发送配置命令给USB设备,表

51、示配置完毕;8.挂起,为了节省电源,当总线保持空闲状态超过3ms以后,设备驱动程序就会进入挂起状态。在挂起状态时,设备的消耗电流不超过500mA当被挂起时,USB设备保留了包括其地址和配置信息在内的所有内部状寄存器。完成以上8个步骤后,USB设备即可使用。在枚举的过程中,设备不一定要求进入挂起状态,基本的USB主机软件流程如图4.2所示。设备初始化是否发生了中断USB中断处理:1.发送设备命令;2.接收设备状态信息;3.配置设备;4.分配地址;5.供给电源查询USB外设是否有数据发送?发送接收数据命令,允许外设发送数据查询设备USB总线活动情况是否需要挂起设备挂起是否是否是否图4.2 USB主

52、机的软件流程4.3 USB与单片机AT89C51SND1通信的流图选获取SL811的片选地址,此时A0为低电平。当A0为高电平是,进行数据操作。先进行写操作,在进行读操作。流图如图4.3所示。开始初始化读、写操作选取SL811HST的片选地址,A0为低电平开始A0是否为1?N 图4.3 流程图4.3 FAT文件系统的设计该部分需要对FAT表的定位、搜索、读/写等操作,UFI命令与外设的磁盘建立联系。UFI命令的实现是基础,整个文件系统通过定地址读取数据、UFIWrite()对特定地址写入数据等等。根据如UFIRead()对特Flash的特性,将Flash的一个Page(512)定义为一个扇区,

53、将两个Block , 64个扇区(512 * 64=32KB)定义为一个簇。主要设计的中间函数编写如下:EnumMassDevU;通过读取。获取磁盘的0扇区的512字节的DBR数据,DBR区所存储的重要的参数。FirstSectorofCluster() ;根据簇号计算对应该簇的第一个扇区号,函数具体实现如下。 INT32 FirstSectorofCluster(unsigned in clusterNUM) INT32 temp; temp=clusterNUM-2; temp=temp*DeviceInfo.BPB-SecPerClus; temp=temp+ DeviceInfo.BP

54、B-SecPerClus; return temp; DeviceInfo.BPB SecPerClus , DeviceInfo.BPB SecPerClus等都是由EnumMassDev()函数从设备中获得的。 UINT ThisFatSecNum(unsigned int clusterNUM)/*根据簇号找到对应FAT表扇区号*/DINT temp;temp=clusterNum*2;temp=temp/DeviceInfo.BPB_ BytesPerSec;temp=temp+Devicelnfo.FatStartSector;return temp; SeekEmptyCluste

55、r()查询空簇所在的位置。从文件分配表的起始扇区开始读取一个扇区的内容,然后判断,内容为0的两个字节对应的即为空簇。 GetNextClusterNum()获取文件下一簇簇C75,实现的方法是读取文件分配表中当前簇号所在的扇区内容,然后根据簇号的扇区偏移量得到文件分配表中该簇号所对应的两个字节存放的就是存储文件后续内容的下一簇的簇号。 DeleteClusterLink()删除簇链,具体函数略。 GetClusterNumFromSectorNum()根据扇区号获得对应簇号,具体函数略。 LinkClusterList()写文件时,一个簇被写满的时候,寻找下一个空簇并与当前簇建立链接,具体函数

56、略。 CheckFileName()根据文件系统命名的要求(8个字节的主文件名和3个字符的扩展名)对所要建立的文件名进行测试,具体函数略。 LocateDir()定位目录所在的扇区和内容,具体函数略。 LocateFile()定位文件所在的扇区,具体函数略。图4.4 文件系统的实现层次建立好上述中间函数,通过这些函数,用户就可以在嵌入式系统中对U盘进行文件操作。API函数:作为提供给用户的编程接口,系统提供了ReadFile(), DelFile()等一系列API函数。这些函数利用UFI子类命令和中间函数,按照FAT文件系统的规范来管理U盘上的数据,调用这API函数,可以实现对文件的管理。这样

57、就可以在USB主机体系中建立起一个外设磁盘的空间结构,建立FAT表·FDT表,并实现查找文件、写文件、读文件等一系列功能。FAT文件系统的设计层次如图4.4所示。4.4 mp3解码器软件的设计开始消息邮箱1有数据?任务挂起否DRWQ为1?是否设置相应寄存器是传送audio文件DREQ为1?否是 图4.5 解码控制流图VS1011的使用非常简单,不需要外接DAC转换,芯片内部集成了几乎所有的MP3的电路,非常方便设计。程序编写主要就是对应硬件的设计设置好寄存器,根据读、写这两个仅有的命令读写特定地址的数据。程序流程图如4.5所示。1.系统启动;系统上电时动作:系统通电,下拉电阻100K

58、参与激活xRESET;启动后等待1 0ms,设AT89C51SND1的GPIO口为信号输出并置为1VS1011即将启动;在DREQ激活后,就可以对VS1011输送命令和数据。卸除供电时动作:xRESET脚被解除应用至少100ms后,方能做此步;WriteSPI(SPI_STATUS,ReadSPI(SPI_STATUS)|(1<<SS_APDOWN2),通过以上伪C语言的操作,实现SS APDOWN2功能,(关于SS APDOWN2,此为状态寄存器SCI STATUS中第3位,关乎模拟驱动器电源卸载效果,由系统固件控制。为防止卸电时瞬态冲击,设此位为1,之后等待几毫秒才可重启操作)

59、;等待10ms或更多时间;激活xRESET;实现VS1011的卸电功能。2.暂时不管xRESET;3.等待DREQ上升为1;4.写寄存器SCI_MODE的参数,包括正确设置SM_SDINEW和SM_SDI-SHARED位;5.若时钟速率不是24.576MHz,应设置SCI_CLOCKF;6.若使用倍频时钟,试图通过改变SCI CLOCKF直接操作,应将适当的采样速率写入SCI AUDATA寄存器,等待至少11000个时钟后才可以操作高速的SPI通讯;7.设置音量寄存器SCI VOL;8.若希望加强低音,设置寄存器SCI BASS;9.若采用RAM级的用户代码,装载这些数据,通过激活SCI_WR

60、AM,SCI_WRAMADDR,SCI_AIADDR来实现功能;10.开始传送音乐文件,在DREQ为高电平时才能传输数据给解码器;11.音乐完成播放,要随音乐文件后通过SD工再传送2048个零;12.若曾使用用户代码,通过置零SCI_AIADDR关闭它;13.转回第3步。芯片的读写时序是底层程序设计的关键,下面就VS1011的命令和数据的操作时序进行使用分析。串行命令接口操作:串行命令接口读和写靠一个8位的操作码来区分,00000011表示读,00000010表示写。在发送读写命令后,要延时5ms在进行后续操作。图4.6 命令接口读VS1011的内部寄存器的读操作:首先XCS拉低,SI口先输入

61、读操作码(00000011),然后就是8位的寄存器地址。地址输入进去以后就忽略SI的任何数据,对应地址的寄存器内的16位数据就可以从SO口读出了。数据读出后应该将XCS拉高,读时序图如图4.6所示。VS1011的内部寄存器的写操作:首先XCS拉低,SI口先输入读操作码(00000010),然后就是8位的寄存器地址。地址输入进去以后接着传输16位的数据,数据写入后应该将XCS拉高,读时序如图4.7所示。图4.7 命令接口写注意;连续两个命令接口写操作之间要XCS拉高然后再拉低继续第二个命令接口写操作。串行数据接口操作:连续两个串行数据操作,XCS不需要做任何变化。在XCS的上升沿,数据接口的数据被同步,每个时序图如图4.8所示。字节并不需要单独的同步操作。图4.8 SDI操作VS1011的数据流程:首先根据数据接口输入进来的数据,MP3或WAV文件被解码。然后传输到低音增强器中(如果SCI_BASS为1,如果是0的话就绕过这部分)。低音增强后的数据根据SCI_AIADDR是否为0,决定是否需要经过可选的用户应用程序操作。经过这部分以后,信号通过音量控制单元已有就

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。