数电实验:实验一码制转换

数电实验:实验一码制转换

《数电实验:实验一码制转换》由会员分享,可在线阅读,更多相关《数电实验:实验一码制转换(29页珍藏版)》请在装配图网上搜索。

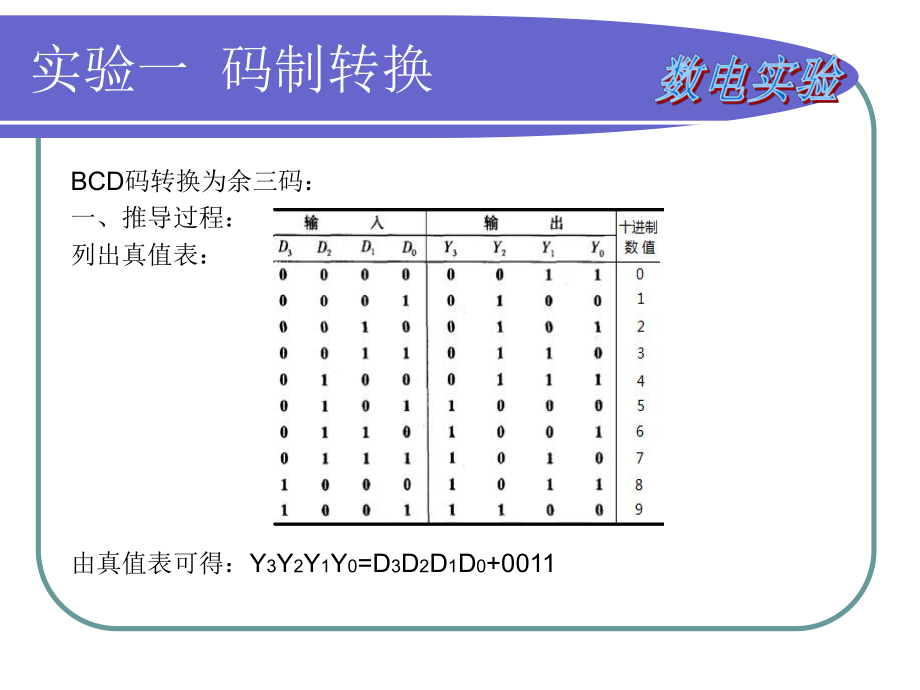

1、实验一 码制转换BCD码转换为余三码:一、推导过程:列出真值表:由真值表可得:Y3Y2Y1Y0=D3D2D1D0+0011实验一 码制转换实验电路原理图:实验一 码制转换输入编译下载仿真二、用CPLD实现设计的实验电路 4大步实验一 码制转换创建电路原理图保存文件创建工程一、输入:选择器件实验一 码制转换1、开发软件QuartusII的操作1)用图形输入法输入实验电路原理图:点击FileNew或直接点击工具栏New按钮,打开New对话框,Device Design Files选项卡中Block Diagram/Schematic File,点”OK”进入原理图编辑界面。实验一 码制转换在原理图

2、空白处双击鼠标左键或右键菜单InsertSymbol或工具栏的”Symbol Tool”快捷按钮打开Symbol对话框,直接在Name框中输入器件的名称,如果不清楚器件的名称,可点击Name框右边的浏览钮,选择库里的器件。点OK,将器件放置到合位置,要旋转器件时,在器件上单击鼠标右键,Rotate菜单中选角度。实验一 码制转换依次输入实验电路所有元件,设定输入输出端口(Input)、(Output),注意端口不能重名。各元件间的连线:可以将鼠标移到要连线元件端口,此时鼠标变成小十字,按鼠标左键拖动到另一要连线元件端口,释放鼠标左键,就完成连线。完成实验电路的输入检查无误后点击File-Save

3、或Save快捷按钮打开文件保存对话框,输入文件名称(注意:不要用默认的block1和元件库里已有的元件名称命名原理图文件)勾选“Creat new porject based on this file”点“保存”,弹出是否建立新工程项目的对话框中选择“是”,进入new porject wizard.实验一 码制转换new porject wizard 头两页都点击”Next”跳过去,进入第三页器件设定“Famaly”框中选“MAXII”在在“Available devices”框选择“EPM240T100C5 3.3V”不能选错器件,否则不能下载。new porject wizard后两页分别

4、点“Next”和”Finish”完成工程项目的设定和文件保存。实验一 码制转换2)编译综合:保存文件,点Processing 菜单中Start Compilation或直接点 Start Compilation快捷按 钮,就自动进行完全编译,编译过程中出现警告不影响电路功能的正常实现。如出现错误提示,则需返回检查原理图文件,修正后重新编译。实验一 码制转换3)仿真创建仿真文件设定仿真波形选择仿真模式指定仿真文件运行仿真验证结果调出信号名称实验一 码制转换3)仿真先建立一个仿真文件,在菜单File中选择New,Other Files选项卡中选择Vector Waveform File,点击OK按

5、钮打开仿真波形文件界面。在仿真信号名称显示区中双击鼠标,打开节点输入界面,点击Node Finder,打开Node Finder对话框。实验一 码制转换在Node Finder对话框,Filter选“Pins:All”,点击list,管脚名称就出现在对话框中,点击Copy all To Select Nodes list,再点OK,管脚(信号名称)就出现在波形文件中。实验一 码制转换编辑输入变量波形:先根据电路状态的多少选择仿真时间长度(End Time)和栅格大小(Grid Size),本例BCD码有10种状态,如果Grid Size设为1mS,每格对应一格状态,则End Time不得小于1

6、0格的时间即10mS。Edit菜单打开End Time和Grid Size对话框进行设置。输入变量的设定:可根据真值表的顺序,用左侧工具栏Forcing Hight/Low输入每个时刻的D0、D1、D2、D3状态,这种方法相当繁琐,对于变量多的系统不适用。实验一 码制转换可以用Count Value作为输入变量。D3、D2、D1、D0作为四位二进制变量的前十个状态,D0为最低位,在仿真的10mS中,每个状态各持续1mS。先点击D0对应的管脚 ,再点 打开Count Value对话框,Counting选项卡按照默认选项,Timing选项卡中,“Count every”选1mS(Grad Size

7、 一个单元时间)。得到的D0变量如下图,10mS转换10次。实验一 码制转换设定D1:也是使用Count Value作为输入变量。Timing选项卡中,“Count every”选2mS,每种状态占两格。设定D2:Timing选项卡中,“Count every”选4mS;每种状态占4格.设定D3:Timing选项卡中,“Count every”选8mS;每种状态占8格。D3、D2、D1、D0就是从00001001连续递增的10个BCD码实验一 码制转换选择仿真方式:选择功能仿真,在Processing 菜单中选Simulator Tool,打开仿真选择卡Simulator Mode 选择Fun

8、ctional,然后点击Generate Functional Simulation Netlist按钮。选定波形文件后点击Start按钮开始仿真。1.选仿真模式2.点击按钮不能漏3.指定仿真文件4.开始仿真必须勾选这一项,否则波形文件无法刷新实验一 码制转换打开波形文件查看仿真结果:认真观察图中10个时刻的状态,D3D2D1D0由0000递增到1001,Y3Y2Y1Y0由0011递增至1100,根据波形图列出真值表。可以看到:每个时刻D3、D2、D1、D0和Y3、Y2、Y1、Y0的关系符合题意,设计正确。实验一 码制转换 4)下载:分配管脚编译工程(使管脚分配生效)运行PROGRAMMER烧

9、写芯片(记得打开实验箱电源)实验一 码制转换 4)下载:分配管脚:即把设计的电路输入输出端口分配到CPLD指定的I/O口,设定步骤如下Assignments菜单中选择Pins,打开PIN PLANNER对话框,在相应端口Location栏双击打开可选择管脚编号的下拉框进行选择。(注意:时序逻辑电路的触发脉冲输入端口只能从12、14、62、64中选择);由于实验板接线孔分布较为紧凑,分配管脚时注意相邻节点不要因为太靠近而在接线时发生短路故障。再次对工程项目进行编译,使管脚分配生效,但凡修改原理图或改变管脚,完成后都要重新编译,使改动生效。实验一 码制转换 接通逻辑实验箱电源。在QuartusII

10、的Tool菜单中选择Programmer或直接点击快捷按钮,打开编程器界面,系统会自动打开编译产生的pof文件,勾选Program/Configure,点Start按钮,进度条变到100,下载完成。有时CPLD芯片由于稳定性问题,点Start出现错误提示,不能下载,可先断开实验板电源,过10秒钟左右重新下载,如果问题还是无法解决,请及时告知实验教师。实验一 码制转换原理图输入文件保存及创建工程器件选择建立仿真文件QuartusII图形输入法实现电路操作小结编译工程设定仿真波形运行仿真验证结果分配管脚编译工程下载实验一 码制转换实验一 码制转换三、静态逻辑功能测试下载完成后,找到各个分配的管脚对

11、应的接线孔,D3、D2、D1、D0分别连接4个电平开关,Y3、Y2、Y1、Y0分别连接4组逻辑指示灯,将测试结果记录在真值表中。实验一 码制转换选择4位逻辑开关产生BCD码:4位逻辑开关从左到右分别与4位输入端D3、D2、D1、D0连接,逻辑开关往上拨输出逻辑“1”,往下拨输出逻辑“0”输出的余三码用逻辑指示灯测量,输出为逻辑“1”时,指示灯点亮,为“0“时灯灭,接指示灯时注意高低位顺序实验一 码制转换四、动态逻辑功能测试:用BCD计数器74160作为信号源提供D3、D2、D1、D0四位输入变量,74160对CP端输入的脉冲信号进行计数,其输出信号QD、QC、QB、QA逐次加1,从0000递增

12、到1001再归零,不断循环。在QuartusII中打开原先建立的原理图文件,调出74160,按下图连接好并编译,注意:分配管脚时,计数器的时钟信号输入端(CP端)只能在CPLD的4个全局时钟输入端(12、14、62、64)中选择。其余管脚可任选。重新编译、下载,进行动态逻辑功能测试。实验一 码制转换将实验项目下载到实验板,CP输入端接实验箱中的3.3V脉冲源”Fout”,信号源频率选择开关分别拨到“1”“0”,这时信号源输出脉冲频率为1KHz用逻辑分析仪测量波形:点击虚拟仪器快捷方式,打开虚拟仪器界面虚拟仪器07通道分别连接8个输入输出变量。计数器时钟信号输入D0输出D1输出D2输出D3输出Y

13、0输出Y1输出Y2输出Y3输出实验一 码制转换打开虚拟仪器界面,点“GO”,虚拟仪器界面动态显示波形,再点一次“GO”波形稳定显示。如果接线时各信号没按照顺序连接,可用鼠标右键拖拽,上下移动各路波形至适合观察的位置。鼠标左键可以左右拖拽在水平方向同时移动各路波形。点击GO,波形出现后再点击一次GO,波形稳定扫描速率50KSa实验一 码制转换观察、记录实验波形图:首先必须明确每个被测信号所对应的波形,对应错误,结果分析完全错误。设定记录的起点,初学者可以借助光标功能,利用光标找出D3D2D1D0为0000的时刻作为记录起点,见图上蓝色光标所在位置。此位置作起点,往右的10个连续的状态分别是D3D2D1D0:00001001的状态,每个时刻,D3D2D1D0和Y3Y2Y1Y0的逻辑状态与真值表时唯一对应的关系,同学可移动光标线进行读数,熟练后应直接从波形图中读出每个时刻各路信号的逻辑状态。蓝色光标对应的测量值

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。