浅析VLSI互联系统时延分析和时延优化方法

浅析VLSI互联系统时延分析和时延优化方法

《浅析VLSI互联系统时延分析和时延优化方法》由会员分享,可在线阅读,更多相关《浅析VLSI互联系统时延分析和时延优化方法(5页珍藏版)》请在装配图网上搜索。

1、浅析VLSI互连系统时延分析和时延优化方法摘要:首先介绍了 VLSI互连系统的时延的定义,然后简单地说明了目前所采用 的几种时延的计算方法和延时模型,最后分为改变布线结构,改进驱动器电路以 及减少RC常量三部分介绍了目前VLSI互连系统时延的优化方法。关键字:时延Elmore延时法RC模型 时延优化Delay Analysis of VLSI interconnect systems and delay optimizationAbstract : Firstly we introduced the definition of delay in VLSI interconnection sys

2、tem, and a brief description of several of the curre ntly used met hod of calcula ting delay and delay models. And finally describes the current VLSI interconnect system latency optimization methods : change the wiring structure, improved driver circuits, reduce the RC constants.Key words: time dela

3、y , Elmore delay method ,RC Models ,time delay optimization1引言在早期的电子工业中,对大多数的 电路系统而言,互连线尺寸远小于信 号波长,在这种情况下,由于逻辑门 和晶体管所引起的信号延迟远远大于 互连线所引起的延迟,所以,互连线 通常只被看作是简单的金属导体,它 仅具有电连通的意义,这时,整个电 路系统的性能主要取决于电路的逻辑 设计,只需利用传统的电路模拟工具 就可在时域内有效地对这一类电路系 统分析与模拟。但是近些年来,随着 半导体材料科学与信息产业的迅猛发 展,大规模集成电路的系统规模越来 越大,工作速度越来越高,特征尺寸 日

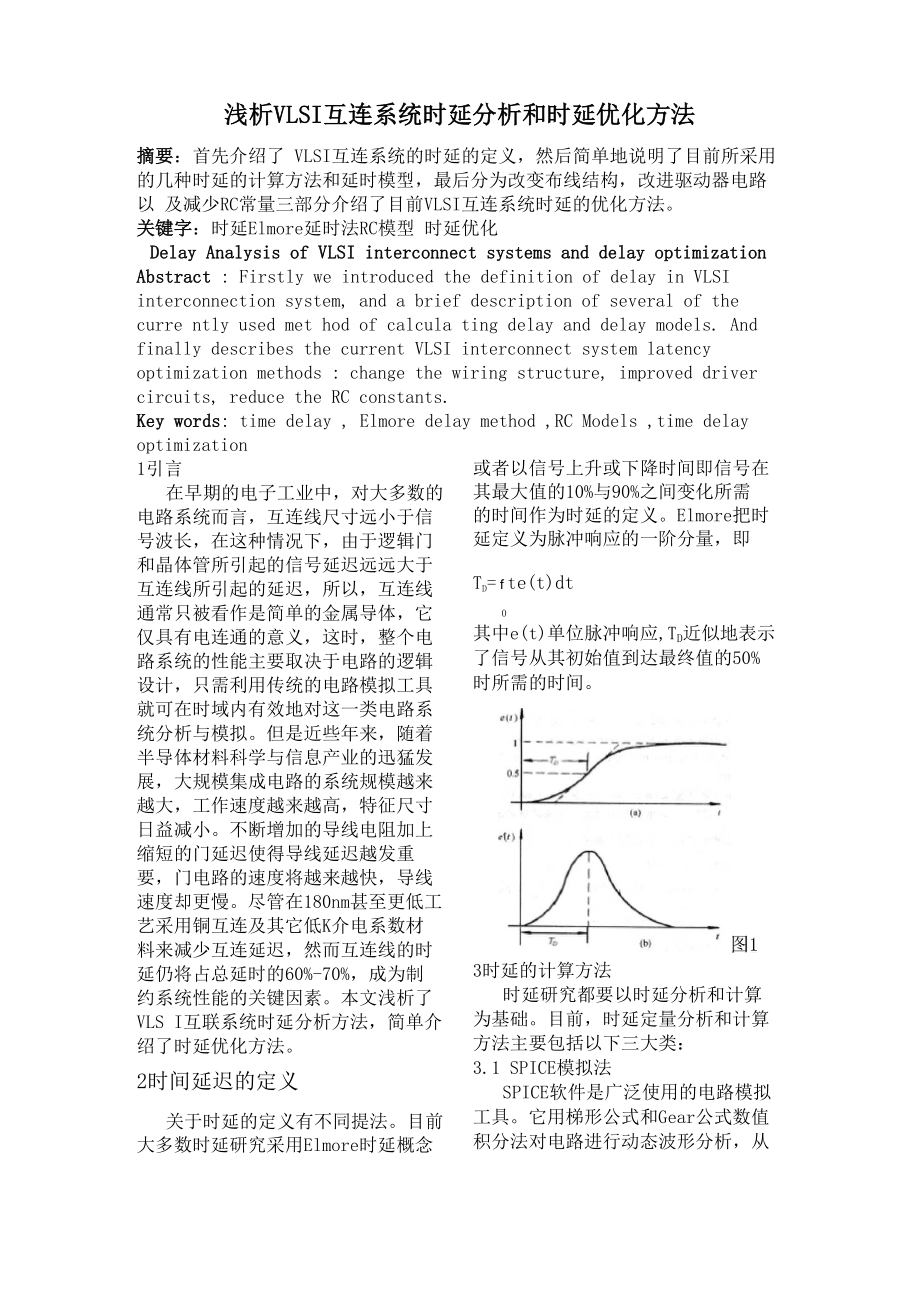

4、益减小。不断增加的导线电阻加上 缩短的门延迟使得导线延迟越发重 要,门电路的速度将越来越快,导线 速度却更慢。尽管在180nm甚至更低工 艺采用铜互连及其它低K介电系数材 料来减少互连延迟,然而互连线的时 延仍将占总延时的60%-70%,成为制 约系统性能的关键因素。本文浅析了 VLS I互联系统时延分析方法,简单介 绍了时延优化方法。2时间延迟的定义关于时延的定义有不同提法。目前 大多数时延研究采用Elmore时延概念 或者以信号上升或下降时间即信号在 其最大值的10%与90%之间变化所需 的时间作为时延的定义。Elmore把时 延定义为脉冲响应的一阶分量,即Td= f te(t)dt0其中

5、e(t)单位脉冲响应,TD近似地表示 了信号从其初始值到达最终值的50% 时所需的时间。3时延的计算方法时延研究都要以时延分析和计算 为基础。目前,时延定量分析和计算 方法主要包括以下三大类:3.1 SPICE模拟法SPICE软件是广泛使用的电路模拟 工具。它用梯形公式和Gear公式数值 积分法对电路进行动态波形分析,从而计算出时延。这种方法的计算精度 较高,但速度慢,因而对大规模电路 的时延分析,需花费过量的计算资源, 不能适应VLSI的要求。3.2分量匹配法(MMM)分量匹配法分析时延的基本思路 是用一个简单的多项式逼近电路的脉 冲响应。设电路的脉冲响应为 H (s)1 + a s + a

6、 s + a S3 + . + a smL型口型Td=RCTd=1/2RCR/2R/2RT型Td=1/2RC3.4互连线的RC模型3.4.1集总RC模型 设用n型等效电路模型,此时Td可写为 T 二 R C + X r (c /2 + C )D00e eet 6 path(V0,V)其中,R0表示源点的输出电阻(Vo是源 点,vi是漏点),re和ce分别表示边(连 线)e的电阻和电容,Ce表示之树Te中 的节点电容之和(这里Te是边e之后的 之树),CO表示整棵树的总电容, pat h( Vo,Vi)表示连接Vo和Vi的所有 边的集合。假设re和ce与边e的长度成 正比,则上式第一项表示时延与

7、RC树 的连线总长度成线性关系,而工求和 项表示时延与源点到漏点的距离成二 次平方关系。因此可得出下列结论:(1) 当Ro较大时,第一项起主要作用, 布线应按连线长度最小为原则;(2)当 Ro相对较小时,求和项占主导地位, 布线应使Vi和Vo的距离最近,并且希 望path(Vo,Vi)中无分支。R1AAA/VW3.4.2分布RC模型如图所示为分布RC的简化模型,通过 微分方程工V(x,t)二 RC V(x,t)6x2Qt对偏微分方程进行求解,进行数学简 化处理后,可以得到传输线终端电压 在阶跃输入激励下的时域表达式。再 进一步计算便可以得到延时函数表达 式。以上所有计算时延的方法各有优 劣。我

8、们的结论是:(1)精确度与计算 速度通常是矛盾的,需折衷考虑和合 理选择;(2)时延计算应具体考虑所用 模型,只要连线的和c的值相对较小 或工作频率不很高,用集总参数模型 也是足够准确的;(3)现有时延计算方 法存在的一个共同问题是主要用于分 析验证,而无法直接提供如何改善时 延的信息,从而很难在版图设计中用 来指导布局和布线。4时延的优化方法互连时延已经成为决定互连性能的 关键因素,因此非常有必须采用一定 技术手段优化时延。为了改善互连系统的 延时,我们采用以下几种方法。第一种方法是采用多层互连线,使上 层的互连线较宽和较厚。采用多层互 连线可以部分解决因互连线尺寸缩小 和芯片尺寸增大引起的

9、延时增加,这 是因为局部互连线可以采用尺寸较小 的第一层(最下层)金属互连线。而长 距离的互连线可以采用较宽较厚的上 层金属互连线,从而使传播延时缩短。 同时通过通孔可以把不同层的金属互 连线连接起来,这样信号进行长距离 传送时不再需要通过多晶或扩散层进 行跨接。由于现代工艺的芯片的大部 分面积为互连线所占据,采用多层金 属互连线可以减小芯片尺寸,而且互 连线的平均长度是与互连线的层数成 反比的,所以多层互连线可以进一步 改善延时。第二种方法是改进驱动电 路。假设一条总电容和总电阻分别为 Rint和Cint的分布参数互连线由输出电 阻为Ro的一个信号源驱动,互连线终端 的负载电容为CL,如图所

10、示当输入为单位阶跃时,如果延时定义 为阶跃响应由其终值的10%增加到 90%所需要的时间,那么该互连线的 总延时为:T90%=1.0Rin tCin t+2.3(R0 CL+R0Cint+RintCL) 当不考虑负载电容Cl时:总延时为T90%=1.0R0Cint+2.3R0Cint 由于互连线的电阻和电容都随连线长 度线性地增长,因此上式所表示的互 连线总延时将随互连线长度的平方增 加。可以证明,如果整个互连线长度 被分隔成许多小段,并在相邻两段之 间插入一个驱动器,那么互连线的总 延时与互连长度之间的关系可以变成 线形关系而不是平方关系。所以通过 改进驱动器电路,例如通过尺寸逐级 增大的级

11、连驱动器使最后一级具备足 够的驱动能力的互连线,或者在长互 连线中插入驱动器把长互连线分隔成 许多较小的子段,都可以使互连线的 延时减小。改进驱动器电路的方法主 要有:(1) 采用最小尺寸反相器作复接驱动 器驱动互连线。(2) 采用最优尺寸反相器作复接驱动 器驱动互连线。(3) 采用级连反相器驱动互连线。 另外,随着电路几何尺寸的缩小,电 路的延迟也因金属互连线电阻的增加 和互连的电容效应而增长,RC常量迅 速成为控制运行速度和相关功耗的主 导因素。RC常数是金属的电阻系数和 金属间介质结构电容的函数。减小RC 常量的方法包括:1)采用具有较低电阻率和较高抗电 迁徙性能的金属。例如铜代替Al

12、;因为互连延迟与互 连长度L的平方根成正比,所以减 小互连长度可带来显著效果。另 夕卜,宽度P要尽可能的大。绝大多 数的集成电路金属化设计,部分或 全部采用电阻系数为2.66的铝合 金。目前,一个发展最快的趋势是 用铜代替。铜有较低的电阻1.67。2)用低介电常数的绝缘材料提供电 隔离。用低介电常数的绝缘材料提供电隔 离是近期发展起来的改善延迟的新 方法。对于绝缘层来说,仅仅从它 淀积或生长的电性能来考虑是不够 的。它受采用条件的影响,随结构 完美程度,缺陷浓度,多孔容量, 断层,化学合成物,电子捕获能力 等而变化,这些导致了很大的隐含 特性。绝缘层特别易受这些影响。 应力,混合或吸收杂质是能

13、影响绝 缘层性质的其它一些因素。此夕, 它们还易老化,吸水,氧化和低温 固化。而低K材料具备下面的特点: 低介电常数(更适宜各向异性)。低 吸水性,好的化学和热稳定性,高 玻璃转化温度,良好的间隙填充和 平坦化能力低薄膜应力,好的电性 能(低介电损耗,对热载流子退化的 正效应,低漏电流,低功耗)等等。 由上所述可知,采用低K材料能够改 善电路性能,是减小延时的另一个 办法。但只有铜互连与低K介质材料 结合起来,才能明显发挥它的优越 性。随着集成电路的发展,互连线 长度和布线层数急剧增加,而导致 延迟时间增大。铜互连和低介电常 数材料能极大地减小金属互连布线 层数。3)插入式中继工艺和可变间隙设

14、计。 由上面的改进方法可知,采用铜和 低k介质材料对互连的改善的确有 很大影响,但目前我们可以利用的 材料因为材料性能及加工工艺诸方 面的影响,对互连的改善都有一定 的限制和困难度,所以从设计上采 用一些新的方法是非常必要的。目 前比较成熟的工艺是插入式中继工 艺和可变间隙设计。目前随集成电 路的发展,全局互连的长度不断增 加,再加之互连向深亚微米级发展, 长的互连势必引起种种如寄生效应 及串扰等的问题。因为互连延迟与 互连长度L的平方根成正比,所以减 小互连长度带来的效果显著。因此 在长互连线上插入缓冲器是一个减 小延迟的很好的考虑方法。因为缓 冲器能恢复电位,阻止了时钟线上 电容的累加效应

15、,从而减低RC值, 减小延时。既可以提高信号传送的 速度,还可以提高抗噪声干扰能力。 当然,加入缓冲器后,由于缓冲器 本身也有延时,也会增加时钟线的 延时,但总的来讲,它对时钟线的 延时减小起着重要的作用一般来说 传输线长度超过6mm时,加入缓冲器 就变得很重要了。但加入的数目是 有一定优化的。所谓的可变间隙路 由设计是指在同一金属层允许不同 线宽出现,可变间隙路由设计在垂 直间距不增加的情况下,延时能够 减小很多。但是最大间隙是最小间 隙的两倍时,延时的改善达到极限。5 小结随着集成电路的发展,用一些模拟 软件模拟的延迟时间从数值和精度方 面越来越不能满足电路性能的需求, 一些传统的互连线模

16、型,由于各种复 杂效应的出现,也越来越不适应延迟 时间的精确计算,这是当今集成电路 发展的重要阻碍之一,因此,需要研 究新的互连模型来计算延迟时间,为电路设计提供比较精确的性能指标。时日益成为制约系统性能的关键因如今集成电路规模越来越大,互连延素,必须寻找更多的措施来优化延时。参考文献:1 孔昕,吴武臣,侯立刚等.VLSI互联线的延时优化研究J.微电子学与计 算机,2010, 27(4): 66.2 赵文庆.超大规模集成电路互连线讨延分析方法)J.浙江工业大学学报, 1997, 25(3).3 钱利波,朱樟明.基于65nmCMOS工艺的互连串扰及延时优化技术DD. 西安:西安电子科技大学硕士论

17、文,2010.4 李长辉,毛军发.深亚微米工艺互连线时延串扰分析及优化设计上海:上海 交通大学硕士论文,20045 陈春鸿,唐璞山.集成电路的连线时延及其在版图设计中的估算J.半导 体学报,1997, 18(7): 531.6 David A Hodges, HoraceG Jackson, Resve A Saleh. Analysis and design of digital integrated circuit- In deep submicron technology M . 3r d ed. Beijing : Publishing House of Electronics Ind

18、ustry , 2005.123m1 + b s + b s2 + b s3 + + asm123m并令H(s) = m 一 m s + ms2 ms3 + .0123这里,m (n=0, 1, 2,)称为n阶分 n量。选择合适的阶数,就可以用一个 简单的多项式近似H(s)。H(s)的前三个分量可计算为m = D, m = D(b 一 a ),0 1 1 1m = D(a 一 a b 一 b 一 b * 1 2)22 11 2 1一般说来,阶数取得太大,精度较高, 但计算复杂化。3.3 Elmore延时法Elmore延迟法相当于一阶分量匹配 法,其延迟时间为Td二m1/m0。当实际 波形非单调变化时,这种方法就不准 确了,这是其局限性。但计算简单是 它的优势,特别是针对具有RC树结构 的线网.其时延可用观察法计算出:T = X r cDnk nk其中,k是树的节点,rnk是输出节点n 与节点k共享的公共路径的电阻,Ck是 节点k上的电容。rnk和吐的具体计算与 所用电路模型有关,下面分几种模型 来进一步地分析。用Elmore延时法有 三种最基本的模型结构,分别是L型, 口型和T型。这几种模型延时计算过程 如下:图2

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。