AltiumDesigner高级覆铜布线规则

AltiumDesigner高级覆铜布线规则

《AltiumDesigner高级覆铜布线规则》由会员分享,可在线阅读,更多相关《AltiumDesigner高级覆铜布线规则(12页珍藏版)》请在装配图网上搜索。

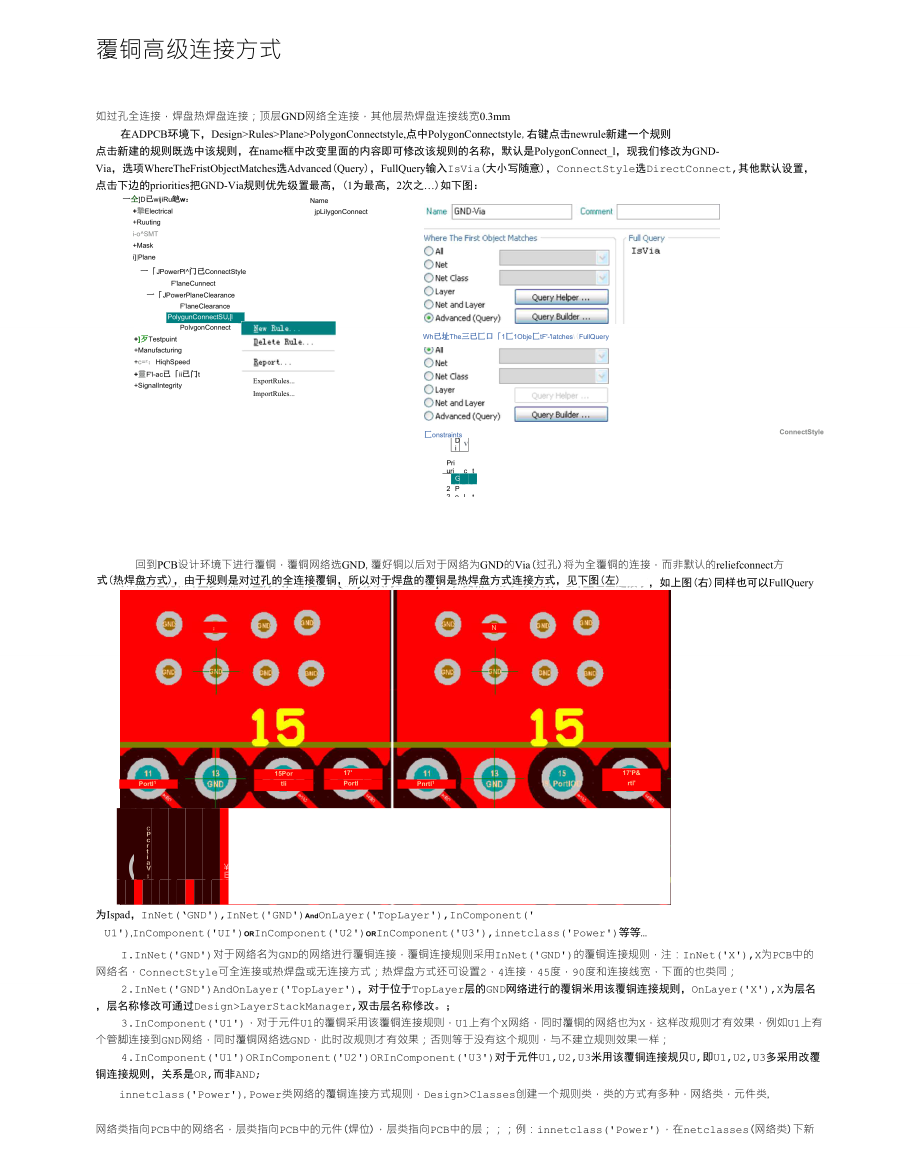

1、SEED1覆铜高级连接方式如过孔全连接,焊盘热焊盘连接;顶层GND网络全连接,其他层热焊盘连接线宽0.3mm在ADPCB环境下,DesignRulesPlanePolygonConnectstyle,点中PolygonConnectstyle,右键点击newrule新建一个规则点击新建的规则既选中该规则,在name框中改变里面的内容即可修改该规则的名称,默认是PolygonConnect_l,现我们修改为GND-Via,选项WhereTheFristObjectMatches选Advanced(Query),FullQuery输入IsVia(大小写随意),ConnectStyle选Direct

2、Connect,其他默认设置,点击下边的priorities把GND-Via规则优先级置最高,(1为最高,2次之)如下图:一仝D已wijiRu皑w:+摯Electrical+Ruutingi-oSMT+Maski|Plane一JPowerPl门已ConnectStyleFlaneCunnect一JPowerPlaneClearanceFlaneClearancePolygunConnectSUrlPolvgonConnect+歹Testpuint+Manufacturing+c=z:HiqhSpeed+靈Fl-ac已ii已门t+SignalIntegrityNamejpLilygonConne

3、ctExportRules.ImportRules.Wh已址The三已匚口1匚1Obje匚tF-latches(FullQuery匚onstraintsSEED#SEED#ConnectStyleDi已匚tCun门已匚:tVPriuritvEnabledfJameScopeAttributesGND-ViaIsVia-AllStyle-DirectConnect122PolHgunCunnectAll-AllStyle-ReliefConnectWidth=10milAngle=90#Entrie回到PCB设计环境下进行覆铜,覆铜网络选GND,覆好铜以后对于网络为GND的Via(过孔)将为全覆

4、铜的连接,而非默认的reliefconnect方式(热焊盘方式),由于规则是对过孔的全连接覆铜,所以对于焊盘的覆铜是热焊盘方式连接方式,见下图(左):NINPortl1Pnrtl117P&rtl15Portli.z(cPcrtiaV;cccE17Portl如果想过孔和焊盘多用热焊盘方式,那在FullQuery修改为IsViaorIspad,更新下刚才的覆铜,地焊盘也全连接了,如上图(右)同样也可以FullQuery为Ispad,InNet(GND),InNet(GND)AndOnLayer(TopLayer),InComponent(U1),InComponent(UI)ORInCompone

5、nt(U2)ORInComponent(U3),innetclass(Power)等等I.InNet(GND)对于网络名为GND的网络进行覆铜连接,覆铜连接规则采用InNet(GND)的覆铜连接规则,注:InNet(X),X为PCB中的网络名,ConnectStyle可全连接或热焊盘或无连接方式;热焊盘方式还可设置2,4连接,45度,90度和连接线宽,下面的也类同;2.InNet(GND)AndOnLayer(TopLayer),对于位于TopLayer层的GND网络进行的覆铜米用该覆铜连接规则,OnLayer(X),X为层名,层名称修改可通过DesignLayerStackManager,双

6、击层名称修改。;3.InComponent(U1),对于元件U1的覆铜采用该覆铜连接规则,U1上有个X网络,同时覆铜的网络也为X,这样改规则才有效果,例如U1上有个管脚连接到GND网络,同时覆铜网络选GND,此时改规则才有效果;否则等于没有这个规则,与不建立规则效果一样;4.InComponent(U1)ORInComponent(U2)ORInComponent(U3)对于元件U1,U2,U3米用该覆铜连接规贝U,即U1,U2,U3多采用改覆铜连接规则,关系是OR,而非AND;innetclass(Power),Power类网络的覆铜连接方式规则,DesignClasses创建一个规则类,类

7、的方式有多种,网络类,元件类,网络类指向PCB中的网络名,层类指向PCB中的元件(焊位),层类指向PCB中的层;例:innetclass(Power),在netclasses(网络类)下新建一个规则(newrule),同样是右键增加,并改名为Power,选中这个网络类规,添加左边的的网络到右边去,比如添加GND,VCCINT,VCC3.3,VCC1.2,VCCA,GNDA等这样在多个多个网络的不同覆铜就不用分另U建立GND,VCCINT,VCC3.3,VCC1.2,VCCA,GNDA的覆铜连接规则,自需要建立一个网络类覆铜连接规则即可,在覆铜的时候覆铜网络连接到相应的网络即可;注意:所有上面的

8、规则多要设置相应的优先级和新建规则,新建规则的优先级设为高,默认规则的优先级最低,其他优先级看实际排列。所有选项选WhereTheFristObjectMatches选Advanced(Query),FullQuery输入相应的数据命令,对于相对简单的类似只是网络和层的覆铜连接InNet(GND)AndOnLayer(TopLayer)顶层地网络的覆铜连接方式,可选择TheFristObjectMatches-NetandLayer,在里面的下拉框中选择相应的Net和Layer后。FullQuery框软件会执行填充数据,完成后ApplyOK回到PCB中(FullQuery框中语法错误,软件会提

9、示错误,而填入一个不存在的层或网络名则不会),再在PCB进行覆铜选择相应的覆铜网络即可,覆铜间距默认是lOmil,如需特殊间距则需修改间距规则;SEED2高级间距规则比如覆铜间距16mil,其他安全间距8mil,过孔到过孔间距100mil,焊盘到焊盘间距100mil,焊盘到过孔间距100mil,顶层地覆铜0.8mm,顶层VCC3.3与VCC1.8覆铜间距0.5mm等AltiumDesigner的间距规则默认为一个10mil间距,没有区分焊盘到焊盘,过孔到过孔,走线到覆铜等的间距,想要高级规则,必须自己新建。在PCB设计环境下DesignRulesElectricalClearance,同样右键

10、新建一个间距规则并重命名为Poly,WhereTheFirstObjectMatches选Adcanced(Query),FullQuery输入inpolygon,Constraints把默认的10mil修改为20mil,优先级Poly比默认的的Clearance的10mil高,这2个间距规则共同构成覆铜间距为20mil,其他间距例如走线到走线,走线到焊盘过孔间距为10mil的规则,如下图:一23DesignRules-挈Electrical匚I已aranciNarneFolyComm已门t計Clear;百習Short-CirJL罰Short白督Un-RoutJ丄沪UnRcJ摯Un-Conm+

11、!FloutingDeleRule.Report.ExportRules.ImportRules.WhereTheFirstObjectMatchesConstraintsditRulePrioritiesPriurityEnabl已dNam已ScopeAttributesPolyinpulyqun-.AllClearanc已=20mil|2味ClearanceAll-AllClearance=10milRuleTnpe:匚I已aranceFullQueryinpolygonSEED3SEED#下2图是过孔覆铜全连接viaconnect,默认安全间距clearance8mil,覆铜间距16mi

12、l规则的覆铜,inpolygon是所有的覆铜,如果想要其他覆铜间距,则需要在新建覆铜规则,比如VCC3.3覆铜0.5mm,VCC1.8覆铜间距0.6mm,其他覆铜0.4mm;优先级16mil的最低;覆一片铜到VCC3.3网络同时起名该覆铜为VCC3.3-ALL;覆一片铜到VCC1.8网络同时起名该覆铜为VCC1.8-ALL;同样要兴建间距规则,见下面第3-6张图:SEED#SEED#一3DesignRules-計Electrical-摯ClearanceNameCommentPoly摯Clearance一已门F;ul已富:-摯Electrical-挈Clearance君Poly君Clearan

13、ce-挈Short-Circuit摯ShortCircuit-計Un-FloutedNet护UnRoutedNet护IJn-ConnectedFin+/SFlnuting+J-&SMT+Mask白Plane-IFd甲冋Plane匚门门已匚tStyI已FlaneConnect一IPowerPlaneClearanceFlaneCI已日吕门匚e一Polygon匚匚i门门已匚tStylef-Jameviaconnecl:CummentWhereTheFirstObjectMatchesFullQueryisviavidCuririecl:WhereTheSecondCbje匚t阴日t匚卜庁AllJN

14、etJNetClass(J)Layer(J)NetandLayer/Advanced(Query)FullQueryAllWhereTheFirstObjectMatchesCunstraintsFullQueryAllFullQueryinpolygonQueryBuilderPulHgonConnect+乡Testpuint+Mdnufdcturing+c=dHighSp已已H+Placement+lllji.-SignalIntegrityConstraints:ConnectStyleDi已匚tConnectjv|DifferentNetsUnhrSEED#SEED4已signRule

15、s-护Electrical-摯Cle-dranceNameVCC1.0-ALLCommentUniqueIDTVSKOSVCC1.0-ALL摯VCC3.3-ALL摯OtherPoly摯Clearance-挈Short-Circuit摯ShortCircuit-摯Un-RoutedNet摯UnFloutedNet針Un-ConnectedPinWhereTheFirstObjectMatchesFullQueryIiil-Jan已匚IP丄爭g:ni:1VCC18-ALL1:iDifferentNetsUnhrMinimumClearanceO.E;mmHdh已r已TheSecundObjectM

16、atchesConstraintsFullQueryAll-+3DesignRules-摯Electrical-摯ClearanceNameVCC3.3-ALLCommentUniqueIDGDOTGJISEED#WhereTheFirstObjectMatchesFullQueryInNaitiedPolygon(1VCC3.3-ALL1)ConstraintsFullQueryAllVCC3.3-ALL計OtherPoly計Clearance-摯Short-Circuit警ShortCircuit-計Un-RoutedNet縈UnRoutedNet計Un-ConnectedPin+卫Flo

17、uting+I-SMT+Mask-PlaneDifferentNetsOnlyMinimumClearance0.5mmSEED#SEED5一31DesignRules-挈Electrical-护ClearanceJ*VCC1.8-ALL君VCC3.3-ALL5*OtherPoly計Clearance-挈Short-Circuit护ShortCircuit-鬻Un-RoutedNet护UnRoutedNet护Un-ConnectedFin+Flnuting+J-&SMT+MaskNameUtherFuhr1L_CommentFullQueryinpijlygonDifferentNetsUnl

18、yCunstr-aintsWhereTheFirstObj已匚tMatchesOMOr-JetFullQueryAll一2DesignRules-挈Electrical-挈ClearanceJ*VCC1.8-ALLf*VCC3.3-ALL录OtherPolyClearance-/Short-Circuit計ShortCircuit-摯Un-RoutedNet护UnRoutedNet計Un-ConnectedPin+Routing+汕T+Mask-PlaneDifferentNetsOnlyMinimumClearance0.254mmConstraintsSEED#Narnevia-to-vi

19、aJComment:WhereTh已FirstObjectr-latch已呂FullQueryHXhEr已The5已匚ijiclObj已匚tMatch已FullQueryConstraintsDifferentNetsOnlyMinimumClearance2.54mm下图是过孔到过孔的间距规贝I,WhereTheFirstObjectMatches,WhereTheSecondObjectMatches的FullQuery,只有这2个参数一个是isvia,另一个是ispad即可;如果一个是ispad另一个是isvia,那就是过孔到焊盘的间距;如果一个是ispad另一个是ispad,那就是焊盘

20、到焊盘的间距;随后填入具体的间距即可,WhereTheSecondObjectMatches默认是ALL,修改他就是第一个和第二个间距规则,IsVia和ALL就是Via到其他的间距规则,IsVia和IsVia就是过孔到过孔的间距规则;一3DesignRules-摯Electrical-摯Clearancevid-to-vid挈holef*L1-GND_ALLJ*L4-GND_ALL君L3Jrack_.WANAf*Poly-L45*Poly-L3挈Pol-r-L1护Clearance-摯Short-Circuit挈ShortCircuit-挈Un-FluutedNet鬻LlnFlnutedNet

21、挈Un-ConnectedPin+Floutingi-fcSMT+Mask-Plane一PowerPlaneConnectStyleFl日门已Cun门已匚t一Fuw已PlaneClearanc已PlaneClearance-Pulvgon匚门门已匚tSUrIe|Polygon_Relief_BOTTOMPolygon_Relief_T0PPolygon_ReliefPolygurLCunnect+初幻Testpoint+Manufacturing+KHighSpeed过孔到过孔间距没有到2.54mm的在线DRC检查出来绿色显示;注:设置小间距管脚间距:一些FPGA芯片等很多焊盘间距多达到了0.

22、2mm,默认的lOmil(0.254mm)间距显然是冲突的,上述问题可以通过HasFootprint(PQ208)或IsPadandInComponent(UI);(IsPadandInComponent(JP4)or(IsPadandInComponent(JP3)HasFootprint(PQ208),封装为PQ208的兀件;sPadandInComponent(U1),元件U1的管脚间的间距;上面2个规则只是管脚间距,丛上面拉出来的线的间距是其他的规则值,当然不能太大;比如上面的PQ208焊盘0.3mm。焊盘间距0.2mm,布线0.2mm,那拉出来的线间距就是0.4mm。如果把布线间距设

23、为0.5mm,1mm,要么绿色,要么拉不出来;(IsPadandInComponent(JP4)or(IsPadandInComponent(JP3),元件JP3,JP4的间距规则;见下面3张图:SEED6SEED7一3DesignRules-摯Electrical-摯Clearance护ClearanL:e_F,Lihr|gon挈Clearance_FPGA挈Clearance+挈Short-Circuit-摯Un-RoutedNet挈IJnRuutedfJet挈Un-ConnectedPin+FloutingS-fcSMT+Mask-Plane一PowerPlaneConnectStyle

24、FlaneConnect一IPuA已PlaneClearanc已FlaneClearance一JPolygunConnectStylePolHgunCunnect+Testpoint+Manufacturing+wHighSpeed+Placement+SignalI门t已grityNarneClear.ance_FF,G.ACommentWhereTh已SecondObjectMatchesCcmstraintsUniqueID|GYTVFullQueryIsPadandInCuinpunent(1U11:iFullQueryAllSEED#SEED#ConstraintsDifferent

25、NetsOnly一3DesignRules-摯Electrical-摯Clearance鬻CledrdnL:e_FQ2LlE!挈Clear.3nce_F,Lihrgun护Clearance_FPGA計Clearance+摯Short-Circuit-摯Un-FluutedNet鬻LlnFlnutedNet摯Un-ConnectedPin+Flouting由SMT+Mask白JPlane一IPowerPlaneConnectStyleFl日门已Cun门已匚t一JFuw已PlaneClearanc已PlaneClearance-Pulvgon匚门门已匚tSUrIePolygunCunnect+VT

26、estpoint+Manufacturing+KHighSpeed+Placement+SignalIntegritySEED#SEED#一工5D已-摯Electrical-挈Clearance护Clearance摯8milNameClearanceCummentUniqueIDHFXAKJTMDifferentNetsOnlyMinimumClearance5mil(IsPadandInCuinpunent(1JP41)ori:IsPaclandInCutciponent.(1JP31)ori:IsPaclandInCuinpun已门匸i:丨u21:i:ior(IsPaclandInCuin

27、puiint.(1ip51)ori:IsPaclandInCuinpunent.(1ip21:i:iFullQu已叩WhereTheSecondObjectMatches0711FullQu已ryAllSEED#下图是一个定位孔间距为3mm的间距规则:常用一个内孔=外孔的焊盘做定位孔。该孔不连接到任何网络(不进行电气连接),只拧螺丝用我们在PCB上4个脚上放4个定位孔,不连接到任何网络,焊盘名称起为HOLE,内孔=外孔大小;free-hole含义free不连接到任何网络,Hole焊盘名称;可以是free-0,free-1,free-2等等;SEED8SEED#-DesignRules-摯Ele

28、ctrical-計Cleararice护via-to-viarNamephul已匚I已日石门匚已CummentUniiphul已匚I已日石门匚已WhereTheFirstObjectMatchesFullQueryHasPad(1至匸已p-HOLE1:iFullQueryAllSEED#0够Oo匚二IR2ConstraintsDifferentNetsUnlyMinimumClearance1nrimilF图为一个在toplayer层覆铜名为5VANA的间距规则,当然toplayer可以换成其他层,5VANA可以换成其他覆铜的名称;SEED#SEED#-2DesignRules-挈Electr

29、ical-計Clearance君top_.WANAI*VCC1.8-ALLf*VCC3.3-ALL护OtherPoly护Clearance-鬻Short-Circuit护ShortCircuit-护Un-RoutedNet計UnRoutedNet挈Un-ConnectedFin+Flouting+&SMT+Mask白|Plane一PowerPlaneConnectStyleFlaneCun门已匚t一JPowerPlaneClearancePlane匚I已引日门匚吕-PolygunConnectStyleviaconnectPLilygunCLinnect+莎T已stpoint+Manufact

30、uring+1二三:HighSpeed+Placement+SignalIntegrityNametop_5,lv,AN11CummentUniqueID|lDConstraintsWhereTheFirstObjectMatchesWhereThe5已匸ondObje匚tF-lat匚h已呂FullQu已ryOnLayeri:1toplayer1:iA1FDIiil-LztiriedP1ygoni:15VAIJA1:iSEED#F图为DM到DP网络间距为20mil的间距规则:SEED9-2lDesignRules-护Electrical-摯Clearance摯DP-DMf*Smil-挈Shor

31、t-Circuit摯ShortCircuit-Un-RoutedNet計UnRoutedNet縈Un-ConnectedPin+左Routing+I-SMT+Mask-Plane- PowerPlaneConnectStylePlaneConnect- PowerPlaneClearancePlaneClearance- PolygonConnectStylePolygonConnect+*Testpoint+Manufacturing+琵HighSpeed+Placement+SignalIntegrityNameDP-DMCommentWhereTheFirstObjectMatchesI

32、Ij-NetCjNetClassOLayerJNetandLayerDM(_.)Advan匚已H(Query)WhereTheSeccindObjectMatchesConstraintsFullQueryIiil-Jet.i:1DM1:iFullQueryIiil-J已匸i:1Dp1:iDifferentNetsUnivMinimumClearance20milSEED#SEED#ConstraintsDifferentNets:0nlyMinimumClearance1BmilF图为MSCLK1网络到其他间距为16mil的间距规则一3DesignRules-摯Electrical-挈Cle

33、aranceJ*DP-DM挈netclass挈8mil-挈Short-Circuit挈ShortCircuit-护Un-RoutedNet护UnRoutedNet摯Un-ConnectedFin+Flouting卄&SMT+MaskEJ-tIPlane一JPowerPlaneCcm门已匚tStyleFlaneCunnect一JPowerPlaneClearanceFlaneCI已日日门匚已一PulygunConnectStyleFolygonCunnect+莎Testpuint+Manufacturing+c=:HighSpeed+Flac已I已门t+SignalI门t已gritySEED#S

34、EED#SEED#SEED10高级线宽规则设置GND网络30mil,VCC网络线宽20mil,布线时按TAB,TrackWidthMode选RulePreferred;)WalkaroundCunflicting匸Ibj已匚tOHugAndPushCunflictingObject0Cumpl已t已RoutingWidthConstraintsInteractiveRoutingUpticmsIIRestrictTo90/45FloutingConflictF;已sulutiun(*)NonePushConflictingObjectO.AutomaticallyTerminateFlouti

35、ng0.AutomaticallvRemoveLuupsTraceWidthiscurrentlyconstrainedbytheruleWGNDtoaminimumuf1Umilandamaximumof1UUmil.IIHugExistingTracesly/alkaroundModeViasUrleiscurr已门tlyconstrai门已Hbytheul已FluutingVias1.TheminimumandmaximumholesizesareUmiland14mil.TheminimumandmaximumdiametersareUmiland24mil.SmartConnecti

36、onPadExits0AllowDiagunalInteractiveRoutingWidth/ViaSizeSuurceskckWithModeRulePreferred_-ViaSizeModeRulePreferred一3DesignRules+挈Electrical-Flouting-WidthNameW_VCCCommentwVCCWGND0%Width- FloutingTupulugyRuutingTupulogv- wRoutingPriorityhRoutingPriority- FloutingLasers:龙FloutingLayers一FloutingCur门已氏:龙R

37、uutingCurners:- RoutingViaStyle卫FluutingVias+Fanout匚untrul- .DifferentialPairsFluuting/SDiffFairsFloutinga-fcSMT+Mask白;|Plane一PowerPlaneConnectSUjeFlaneCun门已匚tPniAiprPlanalaarnriLaWhereTheFirstObjectMatchesConstraintsIICharacteristicImpeda回LasersinlaverstackoMinWidth10milFullQueryInNet(VCC)Attribute

38、sonLayerLayerStackReferenceMinWidthPreferredSizeMa:-:WidthName10mil20mil10OrnilTopLayer10mil20mil1LiOmilBottomLayerI.01SEED#SEED11-13DesignFlules+摯Electrical-Flouting-SWidthW_VCCV/GNDWidth-龙FloutingTopolugyZiFlLiutingTopLilLigy-FluutingFrioritvwRoutingPriority-/SFlnutingLayersFloutingLaHers-Flouting

39、CornersZiFlouting匚匚i广归:::-RoutingViaStyle.rtFloutingVias:+龙Fanout匚Lintrol-龙DifferentialPairsFluuting.rtDiffFairsFlouting+J-&SMT+Mask白|Plane一IPowerPlane匚口门门已匚tStylePI日门已Cun门已匚t一IP厂山!=!PlansriftarannF:Fluuting-WidthW_VCC|-;WGND鼬/i朮h- ZSFloutingTLipLilugvFloutingTopologv-RoutingPriority.rfFloutingPriLi

40、ritH-FloutingLayersFloutingLayers一ZSFlouting匚ornersrfFloutingCor门已巨:-RoutingViaStyle.rfFloutingVidS+FanoutControl- DifferentialPairsRouting.rfDiffFdirsRouting-SMTMaskfflPlane- JFd甲冋Plane匚门门已匚tStyI已|FlaneConnect一IFuw已Fldfi已匚I已dranc已WhereTheFirstObjectMatchesFullQueryIICharacteristicImped0Layersinlaye

41、rstacklUmillUmil1UUmilTopLayer1UUmilButtumLayerNameV/GNDI.01LayerStackReferenceNameJNetClassLayerONetandLayerOAdvanced(Query)Constraints.attributescm1_日|已MinWidthr-jdiiit:vvluiriWhereTheFirstObjectMatches0000(NetNetClassCunstraintsQueryBuild已ruuiiiiiiuni.LayerNetandLayerPreferredWidth8milMinWidthElm

42、ilMaxWidth30milFullQueryAllIICharacteri0Layersin!.Attributes:onLayerMinWidthPreferredSizeMaxWidthLaverStackFlefereName8milSmilSmil8mil3UmilTopLay已30milBottomLayerSEED#SEED#EditRulePrioritiesRuleType:WidthPriorityEnabledNameScopeAttributeswyccInNet(VCC)PrefWidth=10milMinWidth=1OmilMaxWidth=100mil2*WGNDInNet(GND)PrefWidth=10milMinWidth=10milMaxWidth=100mil3WidthAllPrefWidth=SmilMinV/idth=8milxlaxWidth=30milDecreasePriorityCloseSEED#SEED#另外还可以添加类来设置线宽规则,适合大批量线宽处理;SEED12

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。