数字电子技术基础A门电路资料PPT课件

数字电子技术基础A门电路资料PPT课件

《数字电子技术基础A门电路资料PPT课件》由会员分享,可在线阅读,更多相关《数字电子技术基础A门电路资料PPT课件(84页珍藏版)》请在装配图网上搜索。

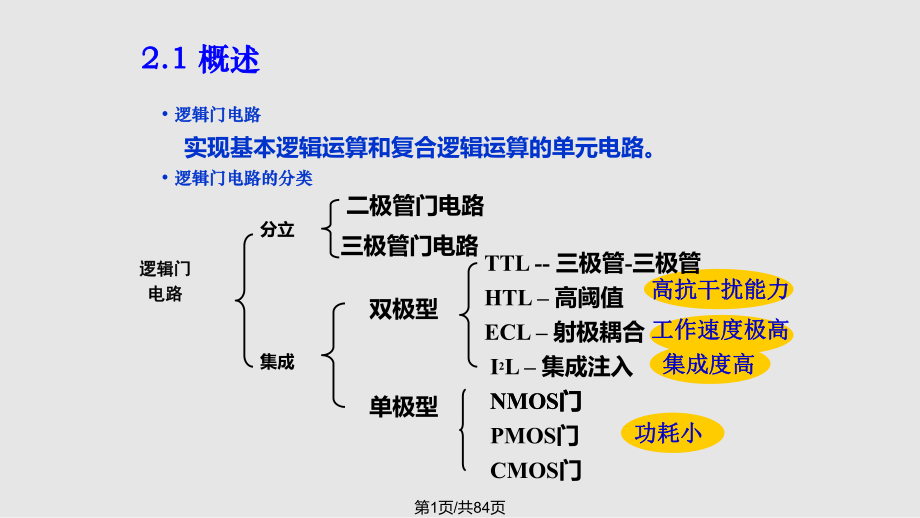

1、实现基本逻辑运算和复合逻辑运算的单元电路。 逻辑门电路逻辑门电路 逻辑门电路的分类逻辑门电路的分类二极管门电路三极管门电路双极型PMOS门CMOS门逻辑门逻辑门 电路电路分立NMOS门TTL - 三极管-三极管HTL 高阈值ECL 射极耦合I2L 集成注入集成单极型高抗干扰能力高抗干扰能力工作速度极高工作速度极高集成度高集成度高功耗小功耗小NMOS门2.1 2.1 概述概述第1页/共84页 高、低电平产生的原理高、低电平产生的原理 +5V R vo S vI 当当S闭合,闭合,vO= 0V当当S断开,断开,vO= +5VVccIvovS1S2输输入入信信号号输输出出信信号号图3.1.3 互补开

2、关电路图3.1.3 互补开关电路第2页/共84页一、二极管导通条件及导通时的特点一、二极管导通条件及导通时的特点二极管二极管D D的符号的符号设二极管的外加正向电压为设二极管的外加正向电压为V VF F,正向导通时的管压降为,正向导通时的管压降为V VD D导通条件:导通条件:VF0.7V(Si)/0.2V(Ge)导通时特点:导通时特点:VD0.7V(Si)/0.2V(Ge)相当于开关闭合后有个0.7/0.2V的恒压降2.2 2.2 半导体二极管、三极管的开关特性半导体二极管、三极管的开关特性二极管的开关特性二极管的开关特性第3页/共84页二、二极管截止条件及截止时的特点二、二极管截止条件及截

3、止时的特点截止条件:截止条件:截止时特点:截止时特点:电流ID接近于0,相当于开关断开加正向电压时VF0.5V(Si)/0.1V(Ge)或加反向电压第4页/共84页理想的开关应具有两个工作状态:理想的开关应具有两个工作状态:-要求阻抗越小越好,相当于短路(导通)要求阻抗越小越好,相当于短路(导通)-要求阻抗越大越好,相当于开路(截止)要求阻抗越大越好,相当于开路(截止) 在数字电路中,二极管和三极管工作在开关状态,即,不在数字电路中,二极管和三极管工作在开关状态,即,不是饱和导通,就是反向截止,好象一个开关一样。是饱和导通,就是反向截止,好象一个开关一样。 当脉冲信号的频率很高时,开关状态的变

4、化速度很快,每当脉冲信号的频率很高时,开关状态的变化速度很快,每秒可达秒可达百万次百万次,这就要求器件的开关转换速度要在微秒甚至纳,这就要求器件的开关转换速度要在微秒甚至纳秒内完成。秒内完成。 因此有必要研究一下二极管导通截止之间的转换过程。因此有必要研究一下二极管导通截止之间的转换过程。 接通状态接通状态断开状态断开状态第5页/共84页1.1.关断特性关断特性:二极管从正向导通到反向截止有一个反向恢复:二极管从正向导通到反向截止有一个反向恢复过程过程vitVF-VRIF-IRt1tstt0.1IRit在在O Ot t1 1期间,期间,vi i VF F,二二极管极管D导通,电路中有电流流过:

5、导通,电路中有电流流过:RLviiD三、二极管的开关特性三、二极管的开关特性第6页/共84页当当t t t t1 1 时,时,vi i 突变到突变到 VR R ,理想时,二极管应立即截止,电理想时,二极管应立即截止,电路中只有很小的反向电流路中只有很小的反向电流 。但实但实际并非如此,见右图:际并非如此,见右图:通常将二极管从导通转为截止通常将二极管从导通转为截止所需的时间称为所需的时间称为反向恢复时间反向恢复时间: tre= ts+tt =ns级级 vitVF-VRIF-IRt1tstt0.1IRit存储时间存储时间渡越时间渡越时间RLviiD第7页/共84页 P 区区 N 区区 势垒区势垒

6、区 + - P 区的电子区的电子浓度分布浓度分布 N 区的空穴区的空穴浓度分布浓度分布 产生反向恢复过程的产生反向恢复过程的原因是原因是电荷存储效应电荷存储效应所引所引起的。反向恢复时间就是起的。反向恢复时间就是存储电荷消失所需要的时存储电荷消失所需要的时间间,一般在纳秒数量级。,一般在纳秒数量级。第8页/共84页2. 2. 开通特性:主要体现在二极管的开通时间开通特性:主要体现在二极管的开通时间开通时间开通时间-二极管从截止转为正向导通所需要的时间二极管从截止转为正向导通所需要的时间 该时间与该时间与反向恢复时间反向恢复时间相比很小,对开关速度影响小,相比很小,对开关速度影响小, 可以忽略不

7、计。可以忽略不计。第9页/共84页一、三极管处于三种工作区的条件一、三极管处于三种工作区的条件截止区:截止区:B、E加正向电压时VF0.5V(Si)/0.1V(Ge)或加反向电压放大区:放大区:发射结正偏、集电结反偏饱和区:饱和区:发射结正偏、集电结正偏临界饱和:临界饱和:UBC=0IB=IC=0 IC=IBUCE=0.10.3V典型值UCE=0.3V三极管的开关特性三极管的开关特性第10页/共84页三极管工作在饱和状态的电流条件为:I IB B I IBS BS CCCCCBECCE0.7V-U-U-RVRVRVRVICCCCCCCS CCCCSBSRVII 第11页/共84页二、二、三极管

8、的动态特性三极管的动态特性(1 1)延迟时间t td d 从输入信号v vi i正跳变的 瞬间开始,到集电极电流i iC C上升到0.10.1I ICSCS所需的时间 (2 2)上升时间t tr r集电极电流从0.10.1I ICSCS上升到0.90.9I ICSCS所需的时间。(3 3)存储时间t ts s从输入信号v vi i下跳变的瞬间开始,到集电极电流i iC C下降到0.90.9I ICSCS所需的时间。(4 4)下降时间t tf f集电极电流从0.90.9I ICSCS下降到0.10.1I ICSCS所需的时间。 第12页/共84页二极管与门电路二极管与门电路非门电路非门电路 三极

9、管反相器三极管反相器二极管或门电路二极管或门电路复合逻辑门电路复合逻辑门电路第13页/共84页二极管与门电路二极管与门电路 B & L=ABC A C 二极管与门电路二极管与门电路与逻辑符号及表达式与逻辑符号及表达式 VCC+(5V) R 3kW L D1 D2 D3 A B C 第14页/共84页VCC+(5V) R 3kW L D1 D2 D3 A B C 0.7V 三个输入端中,只要有一个为三个输入端中,只要有一个为0V, 其余为其余为+5V时:时:输入与输出电压关系输入与输出电压关系0V5V5V 输 入输 出VAVBVCVL0V0V0V0V0V+5 V0V+5 V0V0V+5 V+5

10、V+5 V0V0 V+5 V0V+5 V+5 V+5 V0V0.7V压差大的管子导通第15页/共84页VCC+(5V) R 3kW L D1 D2 D3 A B C 5 V 只有当A、B、C三个输入端均为高电平+5V时:5V5V5V 输 入输 出ABCL00000010010001101000101011001111 真真 值值 表表第16页/共84页 二极管或门电路二极管或门电路 R 3kW D1 D2 D3 A B C L 二极管或门电路或逻辑符号及表达式 B L=ABC A C 11第17页/共84页输入端A、B、C都为0V R 3kW D1 D2 D3 A B C L 0 V或逻辑真值

11、表输 入输 出ABCL00000011010101111001101111011111输 入输 出ABCL000000110101011110011011110111110V0V0V第18页/共84页输入端中只要有一个为+5V R 3kW D1 D2 D3 A B C L 4.3 V或逻辑真值表输 入输 出ABCL00000011010101111001101111011111输 入输 出ABCL000000110101011110011011110111110V5V5V第19页/共84页二极管与门和或门电路的缺点:(1 1)电平偏移:在多个门串接使用时,会出现低电平偏离标准数值的情况。(2

12、2)负载能力差0V5V+V+VL5VDDDD3k(+5V)RCC211CCR2(+5V)0.7V1.4V3k只用于只用于IC内部电路内部电路第20页/共84页 VC C Rc L T Rb A 三极管 反相电路 A 1 L=A 非逻辑符号及表达式非门电路非门电路 三极管反相器三极管反相器第21页/共84页当输入为当输入为逻辑逻辑0 0时时: : VC C Rc L T Rb A 0 vcc1输入A输出L01非逻辑真值表 第22页/共84页当输入为当输入为逻辑逻辑1 1时时: : VC C Rc L T Rb A 1 0输入A输出L0110非逻辑真值表 第23页/共84页 VC C Rc L T

13、 D4 D5 R2 复合门电路复合门电路 VCC+(5V) R 3kW D1 D2 D3 A B C B & L=ABC A C 1、DTL与非门电路第24页/共84页 VC C Rc L T D4 D5 R2 B 1 L=ABC A C 2、DTL或非门电路 R 3kW D1 D2 D3 A B C 第25页/共84页2.4 TTL2.4 TTL集成门电路 集成逻辑门电路是把门电路的所有元器件及连接导线制作在一块半导集成逻辑门电路是把门电路的所有元器件及连接导线制作在一块半导体硅片上,构成集成逻辑门。体硅片上,构成集成逻辑门。 若这种电路的输入级和输出级都采用半导体三极管,则称为三极管若这种

14、电路的输入级和输出级都采用半导体三极管,则称为三极管三三极管集成逻辑门电路(极管集成逻辑门电路(Transistor Transistor Logic),即),即TTL门电路。门电路。集成电路的特点:体积小,重量轻,功耗小,价格低,可靠性等。集成电路的特点:体积小,重量轻,功耗小,价格低,可靠性等。第26页/共84页分类门/片元器件/片SSI (Small Scale Integrated circuit) 11210100MSI (Medium Scale Integrated circuit)1399100999LSI ( Large Scale Integrated circuit)10

15、09999100099999VLSI (Very Large Scale Integrated circuit)10000100000 集成电路根据一块芯片上所集成的门数多少或元件多少可分为小、中、大和集成电路根据一块芯片上所集成的门数多少或元件多少可分为小、中、大和超大规模集成电路。超大规模集成电路。逻辑门和触发器是目前常用的逻辑门和触发器是目前常用的SSI译码器、译码器、 数据选择器、数据选择器、 加法器、加法器、 计数器、计数器、 移位寄存器等组移位寄存器等组件是常用的件是常用的MSI。常见的常见的LSI、 VLSI有只读存储器、有只读存储器、 随机存取存储器、随机存取存储器、 微处理微

16、处理器、高速乘法累加器、器、高速乘法累加器、 通用和专用数字信号处理器等。通用和专用数字信号处理器等。 第27页/共84页 集成逻辑门集成逻辑门是最基本的数字集成电路,是组成数字逻辑的基础。是最基本的数字集成电路,是组成数字逻辑的基础。 常用的集成门电路,大多采用双列直插式封装(常用的集成门电路,大多采用双列直插式封装(Dual-In-line Package ,缩写成缩写成DIP)。)。集成门电路外形图集成门电路外形图第28页/共84页槽口槽口1 2 3 3 4 6 714 13 12 11 10 9 8管脚编号管脚编号 集成芯片表面有一个缺口(引脚编号的参考标志),如果将芯片插在实验集成芯

17、片表面有一个缺口(引脚编号的参考标志),如果将芯片插在实验板上且缺口朝左边,则引脚的排列规律为:左下管脚为板上且缺口朝左边,则引脚的排列规律为:左下管脚为1引脚,其余以逆时针引脚,其余以逆时针方向从小到大顺序排列。方向从小到大顺序排列。一般引脚数为:一般引脚数为:14、16、20等。等。第29页/共84页槽口槽口1 2 3 3 4 6 714 13 12 11 10 9 8管脚编号管脚编号 绝大多数情况下,电源从芯片左上角的引脚接入,地接右下引脚。绝大多数情况下,电源从芯片左上角的引脚接入,地接右下引脚。 一块芯片中可集成若干个(一块芯片中可集成若干个(1、2、4、6等)同样功能但又各自独立的

18、门电等)同样功能但又各自独立的门电路,每个门电路则具有若干个(路,每个门电路则具有若干个(1、2、3等)输入端。等)输入端。输入端数有时称为扇入(输入端数有时称为扇入(Fan-in)数。)数。第30页/共84页(a) 7404(六反相器六反相器) (b) 7400(四四2输入与非门输入与非门) 第31页/共84页与非门的工作原理与非门的工作原理D4kR2R11.6k1kR3130R4ABC+VCC+5VuOuIT4T1T2T3Y一、组一、组成成输入级:输入级:T T1 1,R,R1 1中间级:中间级:T T2 2,R,R2 2,R,R3 3输出级:输出级:T T3 3,T,T4 4,R,R4

19、4,D,D输入级输入级中间级中间级输出级输出级是保护二极管,为防止输入电压过低而设置第32页/共84页多发射极三极管多发射极三极管T1T1作用作用: :实现实现“与与”的功能的功能ABCbc+VCCABCbcABCT1bc第33页/共84页 输入级由多发射极输入级由多发射极三极管三极管T1和基极电组和基极电组R1组成,它实现了输入变组成,它实现了输入变量量A、B、的与运算。的与运算。(1) 输入级输入级第34页/共84页 中间级(中间级(倒相级倒相级)是放大级,由是放大级,由T2、R2和和R3组成,组成,T2的集电极的集电极C2和发射极和发射极E2可以分提供可以分提供两个相位相反的电压信两个相

20、位相反的电压信号,号,以满足输出级的需以满足输出级的需要。要。 (2) 中间级中间级第35页/共84页 输出级由输出级由T3、T4、D和和R4组成,其中其中组成,其中其中D、T3作为由作为由T4组成的反组成的反相器的有源负载。相器的有源负载。 T3与与T4组成推拉式输出结构组成推拉式输出结构,具有较强的负载能力,具有较强的负载能力。(3) 输出级输出级第36页/共84页二、工作原理二、工作原理D4kR2R11.6k1kR3130R4ABC+VCC+5VuOuIT4T1T2T3Y(1)(1)当输入端当输入端ABCABC中中至少至少有有 一个为低电平一个为低电平0.3V0.3V时时低电平(0.3V

21、)深饱和T1深度饱和,则0.3V1VuIT1T2T3T4uO高电平(3.6V)截止截止导通mA1RuVi11BCC1B / )(0i1C 0I1BS 11BBSiIV10Uu1CES1CE. V40uuu1CEI2B. T4截止,T3导通D3BE23BCCOuuRiVu V63707005. 3.6V3.6V第37页/共84页二、工作原理二、工作原理D4kR2R11.6k1kR3130R4ABC+VCC+5VuOuIT4T1T2T3Y(2)(2)当输入端当输入端ABCABC都为都为高电高电 平平3.6V3.6V时时高电平(3.6V)倒置3.6V2.1VuIT1T2T3T4uOmA7250RuV

22、i11BCC1B./ )( V1uuu4BE2CES2C 4.3V3.6V3.6V1.4V假设T1发射结度正向导通,则T1发射结反偏,集电结正偏,工作在倒置状态,即集电极和发射极颠倒使用,此时电流放大系数i在0.02左右mA740iii1Bi1B2B. 假设T2饱和导通,则1VV34uuu1BEI1B. 4BE2BE1BC1Buuuu V12707070. 第38页/共84页二、工作原理二、工作原理D4kR2R11.6k1kR3130R4ABC+VCC+5VuOuIT4T1T2T3Y(2)(2)当输入端当输入端ABCABC都为都为高电高电 平平3.6V3.6V时时高电平(3.6V)倒置3.6V

23、2.1VuIT1T2T3T4uO低电平(0.3V)饱和饱和截止4.3V3.6V3.6V1.4V1VmA52RuVI22CCC2CS./ )( 2052II22CS2BS/./ 22BBSiI故T2饱和的假设成立且T3和D截止对于T4的情况mA24352740Iii2CS2B2E. mA70RUi34BE3R./ mA542iii3R2E4B. 由于T3和D截止,故0I0I4BS4CS ,44BBSiI故T4深度饱和,输出为低电平mA1250. 第39页/共84页(2)(2)当输入端当输入端ABCABC都为都为高电平高电平3.6V3.6V时时(1)(1)当输入端当输入端ABCABC中中至至少少有

24、一个为低电平有一个为低电平0.3V0.3V时时输出为高电平输出为高电平3.6V3.6V输出为低电平输出为低电平0.3V0.3V综上:综上:故输入输出满足关系:故输入输出满足关系:ABCF 该电路为该电路为TTLTTL与非门电路与非门电路第40页/共84页(1)(1)当采用多发射极三极管加快了存储电荷的消散过程。当采用多发射极三极管加快了存储电荷的消散过程。TTLTTL与非门提高工作速度的原理与非门提高工作速度的原理( () )采用了推拉式输出级,输出阻抗比较小,可迅速给负采用了推拉式输出级,输出阻抗比较小,可迅速给负载电容充放电。载电容充放电。+VV+VV123123D123123D(+5V)

25、CCc4o截止T3T4导通导通R充电CLc4CC(+5V)o导通3T4T截止截止R放电CL(a)(b)自学自学第41页/共84页2PHLPLHpdttt与非门传输延迟时间与非门传输延迟时间t tpdpd导通延迟时间tPHL从输入波形上升沿的中点到输出波形下降沿的中点所经历的时间。截止延迟时间tPLH从输入波形下降沿的中点到输出波形上升沿的中点所经历的时间。与非门的传输延迟时间tpd是tPHL和tPLH的平均值。即 一般TTL与非门传输延迟时间tpd的值为几纳秒十几个纳秒。第42页/共84页与非门的电压传输特性及抗干扰能力与非门的电压传输特性及抗干扰能力1电压传输特性曲线:Vo=f(Vi)第43

26、页/共84页特性曲线分为AB、BC、CD、DE四段:AB段:VI0.6VVB11.3VT2、T4截止,而T3、D导通输出电压为高电平3.6V,基本不变BC段:VI0.61.3VT2已经开始导通,但VB21.3V,故T4截止,T2处于放大状态,R2上的电流随着VI的而线性,即R2上的压降随着VI的而线性,因此输出VO将随着VI的而线性CD段:1.3VVI1.4V ,T4已经导通并迅速饱和, T3迅速截止,故VO迅速 ,称CD段为转折段DE段:1.4VVI ,此时T2 、T4都饱和导通,故输出VO0.3V不变第44页/共84页(1 1)输出高电平电压输出高电平电压V VOHOH在正逻辑体制中代表逻

27、辑“1 1”的输出电压。VOH的典型值为3.63.6V,产品规定输出高电压的最小值VOH(min)=2.4=2.4V。(2 2)输出低电平电压输出低电平电压V VOLOL在正逻辑体制中代表逻辑“0 0”的输出电压。VOL的典型值为0.30.3V,产品规定输出低电压的最大值VOL(max)=0.4=0.4V。2 2几个重要参数第45页/共84页(3 3)关门电平电压关门电平电压V VOFFOFF是指输出电压为VOH(min)时对应的输入电压。即输入低电压的最大值。在产品手册中常称为输入低电平电压输入低电平电压,用VIL(max)表示。产品规定VIL(max)=0.8=0.8V。(4 4)开门电平

28、电压开门电平电压V VONON是指输出电压为VOL(max)时对应的输入电压。即输入高电压的最小值。在产品手册中常称为输入高电平电压输入高电平电压,用VIH(min)表示。产品规定VIH(min)=2=2V。第46页/共84页(5 5)阈值电压阈值电压V Vthth电压传输特性的过渡区所对应的输入电压,即决定电路截止和导通的分界线,也是决定输出高、低电压的分界线。 近似地:Vth(VOFF+ +VON)/2 即ViVth,与非门关门,输出高电平; ViVth,与非门开门,输出低电平。 Vth又常被形象化地称为门槛电压门槛电压。Vth的值为1.31.3V1.1.V。第47页/共84页低电平噪声容

29、限 VNLVOFF- -VOL(max)0.80.8V-0.4-0.4V0.40.4V高电平噪声容限 VNHVOH(min)- -VON2.42.4V-2.0-2.0V0.40.4VTTL门电路的输出高低电平不是一个值,而是一个范围。同样,它的输入高低电平也有一个范围,即它的输入信号允许一定的容差,称为噪声容限噪声容限。3 3抗干扰能力第48页/共84页与非门的输入输出特性和带负载能力与非门的输入输出特性和带负载能力1输入特性:iI=f(Vi)ii3.6ViVIIS1.4VIIH(1)(1)当输入低电平时,当输入低电平时,VI=0.3V时,T2截止,iI从T1流出,为负值。ISIIi 1BI

30、1I1BECCRVVV mA0751. (称作输入短路电流)13150.70.34 101mACCBEIILVvvIR 当VI0时,iI最大,此时第49页/共84页与非门的输入输出特性和带负载能力与非门的输入输出特性和带负载能力1输入特性:iI=f(Vi)ii3.6ViVIIS1.4VIIH( () )当输入高电平,当输入高电平,VI3.6V时,T2和T4饱和导通,T1的基极电位被箝位在2.1V,此时T1处于倒置状态,晶体管放大倍数约为0.0211BCCi1BiIRVVIi 0.014514.5mAuAIHI (称作输入端漏电流)第50页/共84页2输入端负载特性:是指输入端外接电阻RI时,其

31、压降VI和RI之间的关系(1)(1)当当RI较小时:VIVT=1.4V 时时, ,相当输入低电平相当输入低电平,所以输出为高电平。所以输出为高电平。(2)(2)当当RI增大时:RI VI =VT 时,输入变高,时,输入变高,输出变低电平。此时输出变低电平。此时VI1.4V。II11BECCIRRRVVV IIRR434 .RI/kVI/V1.4V第51页/共84页开门电阻开门电阻R RONON: :RON一般为2 k /2.5 k保证与非门输出为低电平,允许输入电阻RI的最小值。当RI RON时,相当输入高电平关门电阻关门电阻R ROFFOFF: :ROFF一般为0.7 k /0.8 k保证与

32、非门输出为高电平,允许输入电阻RI的最大值。当RI ROFF时,相当输入低电平注:注:当当R RONON R RI I R ROFFOFF时,不符合正常工作状态,一般不允许时,不符合正常工作状态,一般不允许第52页/共84页由输入端负载特性可知由输入端负载特性可知“与非门与非门”多余输入端的多余输入端的处理方法有以下几种处理方法有以下几种(目的是置(目的是置“1”1”):):(1 1)接高电平)接高电平V VCCCC(2 2)和其他引脚接在一起)和其他引脚接在一起(3 3)外接一大于)外接一大于R RONON的电阻的电阻(4 4)引脚悬空)引脚悬空第53页/共84页输出低电平说明:输出为低,灌

33、电流负载。ILFT3T4RLVCCIL0VOL20mA0.4V T4饱和,Rce4很小,故IL上升时,VOL上升很慢,基本呈线性关系。当VOL VOLMAX0.4V后,低电平输出逻辑关系被破坏,故IL灌受限制,不能过大。把允许灌入输出端的电流定义为输出低电平电流IOL,产品规定IOL=16mA。3TTL的输出特性:输出电压和负载电流之间的关系第54页/共84页输出高电平+5VFR4R5T3T4T5RLIL说明:输出为高, ,拉电流负载。I IL L较小时,T,T3 3处于饱和边缘,T T4 4放大,二者构成的复合管具有一定的放大作用,输出电阻很小,故V VO O基本保持不变。当I IL L5m

34、A5mA后, ,T3T3进入饱和区, V VCE3CE3V VCES3CES3保持不变,V VO O随I IL L上升而下降。IL0VO3.6V2.4V20mA5mAIR4当V VOHOHV VOHMINOHMIN2.4V2.4V后, ,高电平输出逻辑关系被破坏, ,故I IL L拉 受限制,不能过大。把允许拉出输出端的电流定义为输出高电平电流IOH。7474系列最大为 IOHIOH(maxmax)0.4mA0.4mA第55页/共84页4. 4. 扇出系数 扇出系数:“1”“0”灌电流负载拉电流负载 扇出系数就扇出系数就是一个门电路驱动同类型门电路的个数。也就是表示门电是一个门电路驱动同类型门

35、电路的个数。也就是表示门电路的带负载能力。路的带负载能力。“0”“1”第56页/共84页负载门驱动门0 VCC(5V) Rb1 4kW T1 IIL T4 T3 Rc4 130W D 当负载门的个数增加时,当负载门的个数增加时,总的灌电流总的灌电流I IILIL将增加将增加, ,引起输出引起输出低电平低电平V VOLOL的升高。的升高。 灌电流“1”“0”IILIOL(负载门)(负载门)驱动门驱动门ILOLOLIIN)( 第57页/共84页 当负载门的个数增多时,必将当负载门的个数增多时,必将引起输出高电平的降低。引起输出高电平的降低。 拉电流负载门驱动门1 VCC(5V) Rb1 4kW T

36、1 IIH T4 T3 Rc4 130W D “0”“1”IIHIOH一般,TTL的扇出系数扇出系数=10,高的可达高的可达30-50(负载门)(负载门)驱动门驱动门IHOHOHIIN)( 第58页/共84页例 查得基本的TTL与非门7410的参数如下: IOL16mA,IIL1.6mA,IOH0.4mA,IIH0.04mA.试计算其带同类门时的扇出系数。10mA6 . 1mA16 (2)高电平输出时的扇出数10mA04. 0mA4 . 0若NOHNOH,则取较小的作为电路的扇出数。扇出系数计算举例解: (1)低电平输出时的扇出数(负载门)(负载门)驱动门驱动门ILOLOLIIN)( (负载门

37、)(负载门)驱动门驱动门IHOHOHIIN)( 自学自学第59页/共84页2.5 2.5 其他其他TTLTTL集成门电路集成门电路在工程实践中,有时需要将几个门的输出端并联使用,以实现与逻辑,称为线与。但是普通的TTL门电路不能进行线与。门门一、引入目的一、引入目的专门生产了可以进行线与的门电路集电极开路门,也称作OC门(Open Collector Gate)。F10输出高电平时输出电阻小输出低电平时输出电阻小低阻通路电流大,烧坏三极管输出非0非1,破坏逻辑关系普通的TTL门输出电平不可调负载能力不强,尤其是高电平输出第60页/共84页二、电路与符号二、电路与符号4kR2R11.6k1kR3

38、ABC+VCC+5VuOuIT4T1T2YD130R4T3ABC&F+VCC2RLOC门电路图国标符号集电极开路正常使用时,一般需外接上拉负载电阻第61页/共84页三、三、OCOC门的应用门的应用(1) (1) 实现线与实现线与321YYYY GHIDEFABC GHIDEFABC OC门线与图输出级连接图等效逻辑电路图实现实现与或非与或非运算运算第62页/共84页(2) (2) 用作驱动器用作驱动器在OC门的上拉负载电阻RL处用指示灯、继电器等替代,则可作为驱动器使用。+VCC&270+5V右图所示为一OC门驱动发光二极管的电路。可以看出,当OC门输入有一为低电平时,发光二极管灭;当三个输入

39、均为高电平时,输出为低电平,发光二极管亮。u用来驱动继电器用来驱动继电器第63页/共84页(2) (2) 用作驱动器用作驱动器u用来驱动脉冲变压器用来驱动脉冲变压器u用来驱动电容负载,构成锯齿波发生器用来驱动电容负载,构成锯齿波发生器 脉冲变压器与普通变压器的工作脉冲变压器与普通变压器的工作原理相同,只是脉冲变压器可工作原理相同,只是脉冲变压器可工作在更高的频率上。在更高的频率上。第64页/共84页(3) (3) 用作电平转换用作电平转换当改变OC门上拉负载电阻上的电源VCC2为10V时,输入输出端逻辑0对应的低电平保持0.3V不变,而逻辑1对应的高电平由输入端的3.6V变为输出端的10V,高

40、电平对应电压有所转移。通过此电平转换的功能可以调节输出高电平使其满足下一级电路对高电平的要求。+VCC2&RL+10V+VCC+5V输入端:逻辑1 3.6V逻辑0 0.3V输出端:逻辑1 10V逻辑0 0.3V第65页/共84页(4) (4) 实现多路信号在总线上的分时传输实现多路信号在总线上的分时传输第66页/共84页(4) (4) 上拉电阻的计算(确定)上拉电阻的计算(确定)图中:n 上级OC门的个数 p 负载OC门输入端的个数 m 负载OC门的个数 IOHIOHIIHIIHIIHIRLu当OC门的输出为高电平时(含义): IOH OC门的截止漏电流 若负载RL的阻值变大,会使得输出高电平

41、电位降低,若RL无限制增大,可能使输出高电平降低到VOH(min)以下,破坏了正常的逻辑关系,因此,应有: (min)OHLRLCCVRIV IHOHRLpInII IHOHOHCCLpInIVVR (min)自学自学第67页/共84页IOLIISIISIRLu当OC门的输出为低电平时: 若负载RL的阻值变小,会使得输出低电平电位抬高,若RL无限制减小,可能使输出低电平抬高到VOL(max)以上,破坏了正常的逻辑关系,因此,应有: 考虑最不利的情况,假设只有一个OC门(Y1)处于导通状态,其他截止 (max)OLLRLCCVRIV ISOLRLmIII ISOLOLCCLmIIVVR (max

42、)注意:m为负载门的个数,非负载门输入端个数 则: 自学自学第68页/共84页综上,可知上拉负载电阻应满足关系:IHOHOHCCLISOLOLCCpInIVVRmIIVV (min)(max)例:下图电路中各参数已列写出,求上拉电阻大小IOH =200A; IOL=16mAIIS =1mA; IIH=40AVCC =5V; VOH(min)=3V; VOL(max)=0.4VRL(max)=(VCC-VOH)/(2IOH+9IIH)=(5-3)/(20.2+90.04)=2.63(k)RL(min)=(VCC-VOL)/(IOL-3IIS)=(5-0.4)/(16-31)=0.35(k)可以取

43、RL=1k自学自学第69页/共84页门(三态门)门(三态门) 通常数字逻辑是二值的,即仅0,1值,其所对应电路的输出电平是高、低两种状态。在实际电路中,还有一种输出既非高电平又非低电平的状态,被称之为第三状态。于是数字电路的输出就有:0、1和Z(高阻)的三种状态。这种电路称三态逻辑电路或称三态门电路,有时也记作TSL门(Three State Logic gate)。第70页/共84页一、电路结构一、电路结构称为控制端、使能端第71页/共84页(1)(1)当当E E“0”0” “0”导通1V1V截止截止截止高阻电路输出为:电路输出为:Y=Z(Y=Z(高阻态高阻态或悬浮状态,或悬浮状态,也叫禁止

44、状也叫禁止状态态 ) )二、工作原理二、工作原理 在禁止状态下,三态门与负载之间无信号联系,对负载在禁止状态下,三态门与负载之间无信号联系,对负载不产生任何逻辑功能,所以禁止状态不是逻辑状态。不产生任何逻辑功能,所以禁止状态不是逻辑状态。由于三极管由于三极管T3和和T4同时截止,同时截止,输出端相当于输出端相当于悬空或开路。悬空或开路。第72页/共84页(2)(2)当当E E“1”1”“1”截止电路具备逻辑功电路具备逻辑功能:能:ABY 红色二极管截红色二极管截止,相当于开止,相当于开路,不起任何路,不起任何作用。作用。这种状态是三态门的工作状态,也叫这种状态是三态门的工作状态,也叫选通状态选

45、通状态。这时三态门和普这时三态门和普通与非门一样,通与非门一样,完成与非功能。完成与非功能。第73页/共84页三、符号及功能表三、符号及功能表输输出出 高高阻阻1E0EABY 功能表功能表使能端高电平起作用&ENABEY输输出出高高阻阻0E 1E ABY 功能表功能表使能端低电平起作用&ENABEY第74页/共84页第75页/共84页四、三态门的应用四、三态门的应用(1) (1) 总线连接总线连接 分时控制各个门的CS端,就可以让各个门的输出信号分别进入总线。 注意:同一时刻,只允许一个门进入总线。其他门必须保持为高阻状态422BBA 01044BAF 第76页/共84页(2) (2) 实现数

46、据的双向传输实现数据的双向传输右图所示电路为两个三态门组右图所示电路为两个三态门组成的电路,门成的电路,门1 1为低电平使能,为低电平使能,门门2 2为高电平使能。为高电平使能。E=0E=0时,门时,门1 1导通,门导通,门2 2禁止,禁止,数据流向是数据流向是ABABE=1E=1时,门时,门1 1禁止,门,门2 2导通,数据流向是数据流向是BABA第77页/共84页TTL反相器、反相器、 TTL或非门、或非门、TTL与门、与门、TTL或门、或门、TTL与与或非门、或非门、TTL异或门异或门自学自学第78页/共84页各种各种TTL门的性能比较门的性能比较TTL门主要有门主要有74系列,它是国际

47、上通用的标准电路。系列,它是国际上通用的标准电路。TTL门的品种可分为以下几类:门的品种可分为以下几类:标准系列(标准系列(74系列)系列)高速型(高速型(74H系列、系列、74F)低功耗型(低功耗型(74L系列)系列)肖特基(肖特基(Schottky)型()型(74S系列)系列)低功耗肖特基型(低功耗肖特基型(74LS系列)系列)改进低功耗肖特基型(改进低功耗肖特基型(74ALS系列)系列)改进肖特基型(改进肖特基型(74AS系列)系列)第79页/共84页类型类型性能性能PD/mWTpd/nsM/pJ74 74H 74L 74S 74LS 74AS 74ALS 10 22 1 19 2 22

48、 1 10 6 33 3 9.5 1.5 4 100 132 33 57 19 33 4TTL电路的各系列性能比较电路的各系列性能比较 功耗时延积功耗时延积M是衡量一个门的品质指标。是衡量一个门的品质指标。 M=P tpdM 值越大,表示组件的性能越差。值越大,表示组件的性能越差。第80页/共84页CMOS集成门电路集成门电路 CMOS(Complementary MOS)逻辑门电路是继)逻辑门电路是继TTL之后开发的一种数字集成器件。之后开发的一种数字集成器件。 由于由于CMOS的工作速度可与的工作速度可与TTL相媲美,而相媲美,而CMOS的功的功耗和扇出数则远优于耗和扇出数则远优于TTL,

49、CMOS的抗干扰能力也比的抗干扰能力也比TTL强。强。因此,因此,CMOS电路可能超越电路可能超越TTL而成为占主导地位的逻辑器而成为占主导地位的逻辑器件。目前,几乎所有的大规模集成电路都采用件。目前,几乎所有的大规模集成电路都采用CMOS工艺制工艺制造,且费用较低。造,且费用较低。自学自学第81页/共84页-0.1103-0.1103-0.4-1.6IIL(max) / mA0.10.12040IIH(max) / A0.810.80.8VIL(max) / V23.522VIH(min) / V44816IOL(max) / mA-4-4-0.4-0.4IOH(max) / mA0.10.10.50.4VOL(max) / V4.44.42.72.4VOH(min) / VCMOS(74HCT系列)CMOS(74HC系列)TTL(74LS系列)TTL(74系列) 电路种类参数名称第82页/共84页习题习题P135P1352.1 画画Uo1、Uo2、Uo42.112.13(1)2.142.15第83页/共84页感谢您的观看!第84页/共84页

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。