xilinxFPGASelectIO模块

xilinxFPGASelectIO模块

《xilinxFPGASelectIO模块》由会员分享,可在线阅读,更多相关《xilinxFPGASelectIO模块(12页珍藏版)》请在装配图网上搜索。

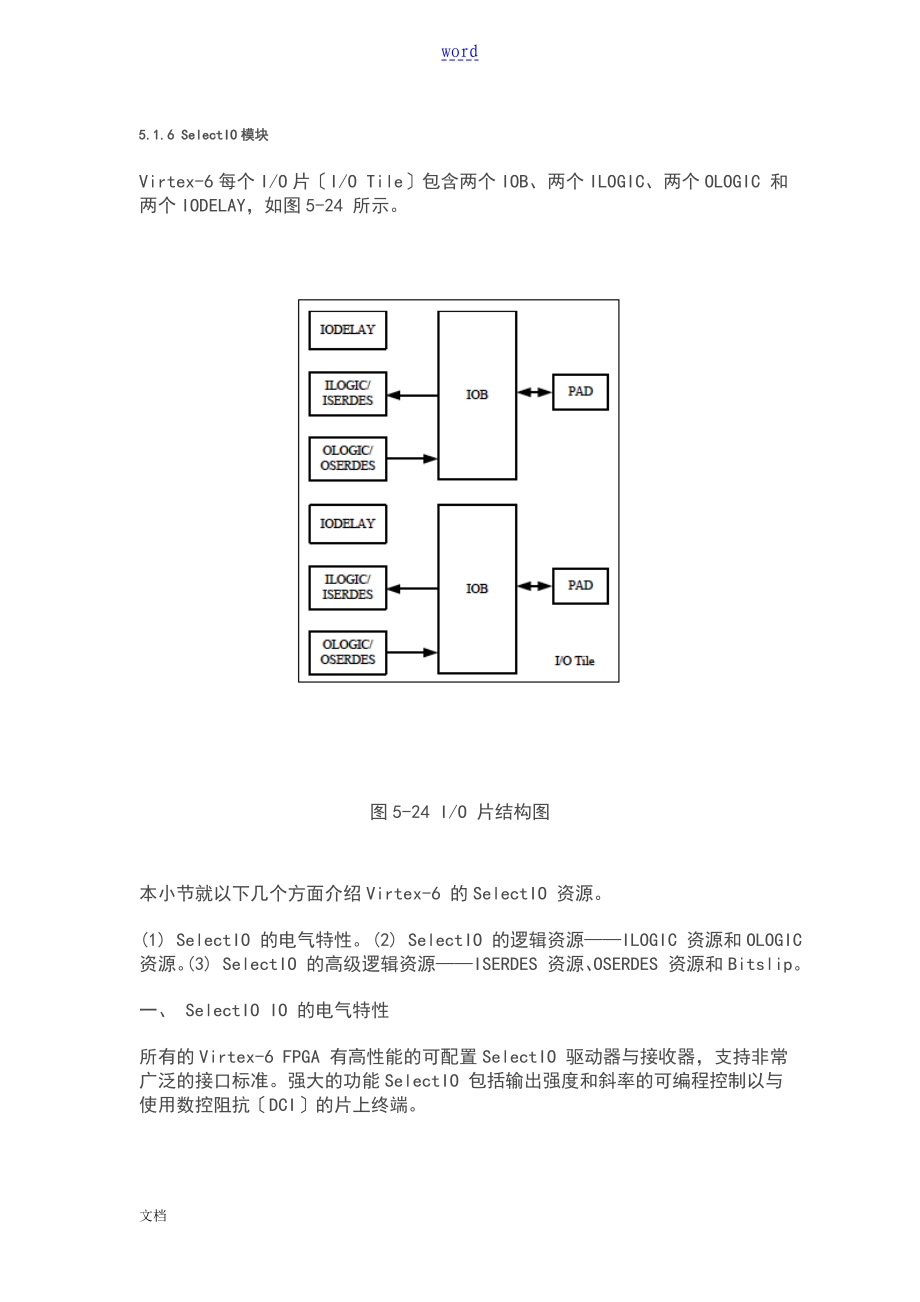

1、word5.1.6 SelectIO模块Virtex-6每个I/O片I/O Tile包含两个IOB、两个ILOGIC、两个OLOGIC 和两个IODELAY,如图5-24 所示。图5-24 I/O 片结构图本小节就以下几个方面介绍Virtex-6 的SelectIO 资源。(1) SelectIO 的电气特性。(2) SelectIO 的逻辑资源ILOGIC 资源和OLOGIC 资源。(3) SelectIO 的高级逻辑资源ISERDES 资源、OSERDES 资源和Bitslip。一、 SelectIO IO 的电气特性所有的Virtex-6 FPGA 有高性能的可配置SelectIO 驱动

2、器与接收器,支持非常广泛的接口标准。强大的功能SelectIO 包括输出强度和斜率的可编程控制以与使用数控阻抗DCI的片上终端。IOB 包含输入、输出和三态SelectIO 驱动器。支持单端I/O 标准LVCMOS、HSTL、SSTL和差分I/O 标准LVDS、HT、LVPECL、BLVDS、差分HSTL 和SSTL。注意:差分输入和VREF 相关输入由VCCAUX 供电。IOB、引脚与内部逻辑的连接如图5-25 所示。图5-25 IOB、引脚与内部逻辑连接图IOB 直接连接ILOGIC/OLOGIC 对,该逻辑对包含输入和输出逻辑资源,可实现数据和三态控制。ILOGIC和OLOGIC可分别配

3、置为ISERDES和OSERDES。Xilinx软件库提供了大量与I/O相关的原语,在例化这些原语时,可以指定I/O标准。与单端I/O相关的原语包括IBUF输入缓冲器、IBUFG时钟输入缓冲器、OBUF输出缓冲器、OBUFT三态输出缓冲器和IOBUF输入/输出缓冲器。与差分I/O相关的原语包括IBUFDS输入缓冲器、IBUFGDS时钟输入缓冲器、OBUFDS输出缓冲器、OBUFTDS三态输出缓冲器、IOBUFDS输入/输出缓冲器、IBUFDS_DIFF_OUT输入缓冲器和IOBUFDS_DIFF_OUT输入/输出缓冲器。二、 SelectIO的逻辑资源SelectIO的逻辑资源主要是指ILOG

4、IC和OLOGIC资源,它们完成了FPGA引脚到内部逻辑的连接功能,包括组合输入/输出、三态输出控制、存放器输入/输出、存放器三态输出控制、DDR输入/输出、DDR输出三态控制、IODELAYE1高分辨率可调整延迟单元与其控制模块。下面简要介绍ILOGIC和OLOGIC功能。(1) ILOGIC。图5-26 ILOGIC内部逻辑ILOGIC的内部逻辑如图5-26所示,可以实现的操作包括:异步/组合逻辑、DDR模式OPPOSITE_EDGE、SAME_EDGE或SAME_EDGE_PIPELINED、电平敏感型锁存器和边沿触发D型触发器。 异步/组合逻辑。 用来创建输入驱动器与FPGA内部资源之

5、间的直接连接。当输入数据与FPGA内部逻辑之间存在直接非存放连接,或者当“将I/O存放器/锁存器合并到IOB中的设置为OFF时,此通路被自动使用。 输入DDRIDDR。 Virtex-6器件的ILOGIC中有专用存放器来实现输入双倍数据速率DDR。可以通过例化IDDR的原语来使用此功能。IDDR只有一个时钟输入,下降沿数据由输入时钟的反相版本在ILOGIC内完成反相进展时钟控制。所有输入I/O模块的时钟均为完全多路复用,即ILOGIC或OLOGIC模块之间不共用时钟。IDDR支持以下三种操作模式:OPPOSITE_EDGE模式、SAME_EDGE模式和SAME_EDGE_PIPELINED模式

6、。SAME_EDGE和SAME_EDGE_PIPELINED与Virtex-5一样。这些模式允许设计人员在ILOGIC模块内部将下降沿数据转移到上升沿时钟域,以节省CLB和时钟资源并提高性能。这些模式是用DDR_CLK_EDGE属性实现的。各模式下时序图请参考图5-27、图5-28和图5-29。图5-27 OPPOSITE_EDGE模式下的输入双倍数据速率图5-28 SAME_EDGE模式下的输入双倍数据速率图5-29 SAME_EDGE_PIPELINED模式下的输入双倍数据速率 可编程绝对延迟单元IODELAYE1。 每个I/O模块包含一个可编程绝对延迟单元,称为IODELAYE1。IOD

7、ELAYE1可以连接到ILOGIC/ISERDES或OLOGIC/OSERDES模块,也可同时连接到这两个模块。IODELAYE1是具有32个tap的环绕延迟单元,具有标定的tap分辨率。请参考附带光盘中的Virtex-6 IO用户手册。IODELAYE1可用于组合输入通路、存放输入通路、组合输出通路或存放输出通路,还可以在内部资源中直接使用。IODELAYE1允许各输入信号有独立的延迟。通过在Virtex-6用户手册中规定的X围内选择IDELAYCTRL参考时钟,可以改变tap延迟分辨率。IODELAYE1资源可用作IDELAY、ODELAY或组合延迟。.IDELAYE1允许各输入信号有独立

8、的延迟。延迟单元可以被校验到一个绝对延时固定值(TIDELAYRESOLUTION),这个值不随工艺,电压和温度的变化而改变。IODELAYE1有四种操作模式:分别是零保持时间延迟模式IDELAY_TYPE=DEFAULT、固定延迟模式IDELAY_TYPE=FIXED、可变延迟模式IDELAY_TYPE=VARIABLE和可装载的可变延时模式IDELAY_TYPE=VAR_LOADABLE。零保持时间延迟模式允许向后兼容,以使用Virtex-5器件中的零保持时间延迟功能的设计,在这种模式下使用时,不需要例化IDELAYCTRL的原语。在固定延迟模式,延迟值由属性IDELAY_VALUE确定的

9、tap数决定,此值配置后不可更改,此模式必须例化IDELAYCTRL的原语。在可变延迟模式,配置后通过控制信号CE和INC来改变延迟值,此模式必须例化IDELAYCTRL的原语。在可装载的可变延时模式下,IDELAY TAP可以通过FPGA逻辑相连的5位TVALUEIN装载。当配置为此模式时,也必须例化IDELAYCTRL原语。 IDELAYCTRL延时控制模块。 当IDELAYE1或ISERDES的原语中的IOBDELAY_TYPE属性设置为FIXED、VARIABLE或者VAR_LOADABLE时,都必须例化IDELAYCTRL。IDELAYCTRL模块连续校验IODELAYE1的延时环节

10、,以减少工艺、电压和温度的影响。(2) OLOGIC资源。OLOGIC由两个主要模块组成,分别是输出数据通路和三态控制通路。这两个模块具有共同的时钟CLK,但具有不同的使能信号OCE和TCE。输出通路和三态通路可独立配置为边沿触发的D型触发器、电平敏感锁存器、异步/组合逻辑或者DDR模式。 组合数据输出和三态控制路径。 组合输出通路用来实现从FPGA内部逻辑到输出驱动器或输出驱动器控制端的直接连接。当FPGA的内部逻辑与输出数据或三态控制之间存在直接不存放连接,或者当“将I/O存放器/锁存器合并到IOB中的设置为OFF时,此路径被使用。 输出DDRODDR。 Virtex-6器件的OLOGIC

11、中具有专用存放器,用来实现DDR功能。要使用此功能,只需要例化ODDR。ODDR只有一个时钟输入,下降沿数据由输入时钟的反相时钟控制。ODDR支持两种操作模式:OPPOSITE_EDGE模式和SAME_EDGE模式。SAME_EDGE模式允许在ODDR时钟的上升沿将两个数据送至ODDR,以节省CLB和时钟资源并提高性能。OPPOSITE_EDGE模式使用时钟的两个沿以两倍吞吐量从FPGA内部采集数据,两个输出都送至IOB的数据输入或三态控制输入。图5-30所示为使用OPPPOSITE_EDGE模式时输出DDR的时序图。图5-31所示为使用SAME_EDGE模式时输出DDR的时序图。图5-30

12、OPPPOSITE_EDGE模式时输出DDR图5-31 SAME_EDGE模式时输出DDR输出ODDR可以将时钟的一个副本传送到输出。将ODDR原语的D1固定为High,D2固定为Low,时钟与数据ODDR的时钟一样。这个方案可以确保输出数据与输出时钟延时的一致性。三、 SelectIO的高级特性除了SelectIO的电器特性和专用于收发SDR或DDR数据的存放器结构之外,Virtex-6还提供了更高级的逻辑特性。其中包含串并转换器ISERDES、并串转换器OSERDES和Bitslip。(1) ISERDES。Virtex-6 ISERDES是专用的串并转换器,具有专门实现高速源同步应用的时

13、钟控制与逻辑功能。图5-32为ISERDES的结构图,其中包括串并转换器ISERDES、Bitslip子模块,以与对选通存储器接口的支持,如网络接口、DDR3接口和QDR接口。图5-32 ISERDES结构图 输入串并转换器。 ISERDES解串器可以实现高速数据传输,不要求FPGA内部资源与输入数据频率匹配。此转换器支持SDR和DDR。在SDR模式下,串并转换器可以实现2、3、4、5、6、7或8bit宽的并行字。在DDR模式下,串并转换器可以实现4、6、8或10位宽的并行字。ISERDES的原语ISERDES1如图5-33所示。图5-33 ISERDES的原语ISERDES1 Bitslip

14、模块。 Virtex-6器件中的所有ISERDES模块都包含一个Bitslip子模块。这个子模块可在源同步网络型应用中实现字对齐。Bitslip对ISERDES模块中的并行数据重新排序,以便将解串器所接收重复串行模式的每种组合都送至FPGA内部逻辑。这种重复串行模式通常称为培训模式许多网络和电信标准都支持培训模式。Bitslip操作通过将ISERDES模块的Bitslip引脚置为有效,可以在并行侧对输入串行数据流重新排序。此操作重复进展,直到找到训练模型。图5-34 中所示为SDR 和DDR 模式下Bitslip 操作的效果。为了便于说明,采用了八位数据宽度。Bitslip 操作与CLKDIV

15、 同步。在SDR 模式下,每次Bitslip 操作使输出模式左移一位。在DDR 模式下,每次Bitslip操作使输出模式在右移一位和左移三位之间交替变化。在此示例中,输出模式在第八次Bitslip 操作时复原到初始模式。这里假定串行数据是八位重复模式。图5-34 Bitslip 操作使用Bitslip 子模块的指导原如此如下。只有在NETWORKING 模式下,Bitslip 才有效。其他模式下,不支持Bitslip。要启动Bitslip 操作,BITSLIP 端口置为High 有效的时间必须持续在一个CLKDIV 周期。在SDR 模式下,Bitslip 的置位时间不能长达两个连续的CLKDI

16、V 周期;在两次Bitslip有效置位之间,Bitslip 的无效时间至少有一个CLKDIV 周期。在SDR 和DDR 两种模式下,从ISERDES 采样到Bitslip 有效的宣称输入到“bit-slippedISERDES 的输出Q1-Q6 被采样到FPGA 内部逻辑,总延迟是两个CLKDIV 周期。 对选通存储器接口的支持。 ISERDES 包含专用电路包括OCLK 输入引脚,可以完全在ISERDES 模块内部处理选通门到FPGA 跨时钟域的功能。该功能可以极大方便选通存储器的支持,如网络接口、DDR3 接口和QDR 接口。(2) 输出并串转换器OSERDES。Virtex-6 OSER

17、DES 是专用的并串转换器,用来实现高速源同步接口设计。每个OSERDES 模块包括一个数据串行器和一个实现三态控制的串行器。此转换器支持SDR 和DDR。数据串行化可达6:1如果使用“OSERDES 宽度扩展可达10:1。三态串行化可达4:1。OSERDES 的框图如图5-35 所示。 数据并串转换器。 一个OSERDES 模块中的数据并串转换器接收来自内部逻辑的二到六位并行数据,将数据串行化,然后通过OQ 输出将数据送至IOB。并行数据串行化是按照从数据输入引脚的最低位到最高的顺序进展的即D1 输入引脚上的数据传输到OQ 引脚的首位。OSERDES 使用CLK 和CLKDIV 两个时钟进展数据速率转换。CLK 是高速串行时钟;CLKDIV 是分频并行时钟。图5-35 OSERDES的结构框图 三态并串转换。 除了数据的并串转换,OSERDES模块还包含一个三态并串转换器,三态并串转换器最多只能串行化四位并行三态信号。三态转换器不能级联。OSERDES的原语如图5-36所示。图5-36 OSERDES的原语文档

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。