北邮-数字逻辑实验报告

北邮-数字逻辑实验报告

《北邮-数字逻辑实验报告》由会员分享,可在线阅读,更多相关《北邮-数字逻辑实验报告(30页珍藏版)》请在装配图网上搜索。

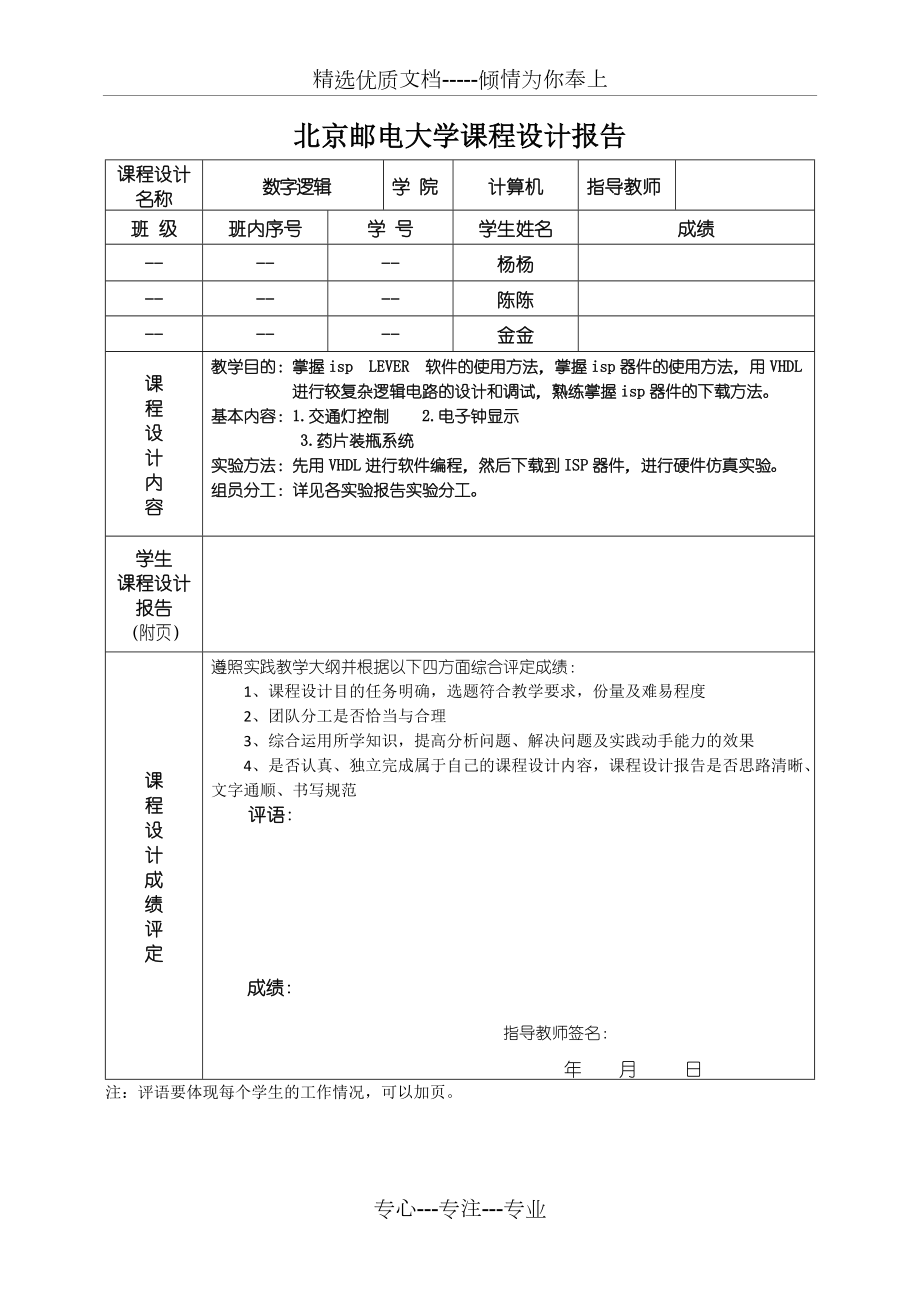

1、精选优质文档-倾情为你奉上北京邮电大学课程设计报告课程设计名称数字逻辑学 院计算机指导教师班 级班内序号学 号学生姓名成绩-杨杨-陈陈-金金课程设计内容教学目的:掌握isp LEVER 软件的使用方法,掌握isp器件的使用方法,用VHDL进行较复杂逻辑电路的设计和调试,熟练掌握isp器件的下载方法。基本内容:1.交通灯控制 2.电子钟显示 3.药片装瓶系统实验方法:先用VHDL进行软件编程,然后下载到ISP器件,进行硬件仿真实验。组员分工:详见各实验报告实验分工。学生课程设计报告(附页)课程设计成绩评定遵照实践教学大纲并根据以下四方面综合评定成绩:1、课程设计目的任务明确,选题符合教学要求,份

2、量及难易程度2、团队分工是否恰当与合理3、综合运用所学知识,提高分析问题、解决问题及实践动手能力的效果4、是否认真、独立完成属于自己的课程设计内容,课程设计报告是否思路清晰、文字通顺、书写规范评语: 成绩:指导教师签名: 年 月 日注:评语要体现每个学生的工作情况,可以加页。目录实验一:交通灯控制器设计一、实验目的学习采用状态机方法设计时序逻辑电路。掌握ispLEVER软件的使用方法。掌握用VHDL语言设计数字逻辑电路。掌握ISP器件的使用。二、实验所用器件和设备在系统可编程逻辑器件ISP1032一片示波器一台万用表或逻辑笔一只TEC-5实验系统,或TDS-2B数字电路实验系统一台三、实验内容

3、以实验台上的4个红色电平指示灯,4个绿色电平指示灯模仿路口的东南西北4个方向的红,绿,黄交通灯。控制这些交通灯,使它们按下列规律亮,灭。(1) 初始状态为4个方向的红灯全亮,时间1s。(2) 东,西方向绿灯亮,南,北方向红灯亮。东,西方向通车,时间5s。(3) 东,西方向黄灯闪烁,南,北方向红灯,时间2s。(4) 东,西方向红灯亮,南,北方向绿灯亮。南,北方向通车,时间5s。(5) 东,西方向红灯闪烁,南,北方向黄灯闪烁,时间2s。(6) 返回(2),继续运行。(7) 如果发生紧急事件,例如救护车,警车通过,则按下单脉冲按钮,使得东,南,西,北四个方向红灯亮。紧急事件结束后,松开单脉冲按钮,将

4、恢复到被打断的状态继续运行。四、设计思路(1) 将本实验分为分频,状态计数器,led输出三大模块;(2) 分频模块需要注意到占空比,采用when-else语句;(3) 状态计数器都分为5s,2s,5s,2s,四个状态时间,通过计数器作状 态转移;(5) led输出模块的黄灯闪烁可通过2HZ的方波信号实现。(6) 选择实验台上的5kHz频率时钟,作为设计中分频的初始时钟。(5) 紧急事件发生时,要注意保存必要的信息,已被紧急事件结束后,恢复到原状态继续运行使用。 五、设计方案模块图1、tralight(顶层模块代码)library ieee;use ieee.std_logic_1164.all

5、;use ieee.std_logic_unsigned.all;entity tralight is port(clk,emg: in std_logic; -5KHZ时钟输入,紧急输入 tout: out std_logic_vector(11 downto 0); -12盏led灯输出 tout2,tout1: out std_logic_vector(3 downto 0);-倒计时end tralight;architecture top of tralight is component fenpin -分频模块 port( clkin: in std_logic; -5KHZ时钟输

6、入 clkout1: out std_logic; -1HZ时钟 clkout2: out std_logic); -2HZ时钟 end component; component ztjishuqi -状态计数器模块 port( emg1,clk1: in std_logic; -紧急输入,1HZ时钟输入 stateout: out std_logic_vector(1 downto 0); -2位状态输出 daoout2,daoout1: out std_logic_vector(3 downto 0);-倒计时 end component; component led -led交通灯显示模

7、块 port(emg2,clk2: in std_logic; -紧急输入,2HZ时钟输入(方波闪烁) statein: in std_logic_vector(1 downto 0); -2位状态输入 ledout: out std_logic_vector(11 downto 0); -12盏led灯输出 end component;signal fenpin1: std_logic;signal fenpin2: std_logic;signal state: std_logic_vector(1 downto 0);begin u1: fenpin PORT MAP(clkin=clk

8、, clkout1=fenpin1, clkout2=fenpin2); u2:ztjishuqi PORTMAP(emg1=emg,clk1=fenpin1,stateout=state,daoout2=tout2,daoout1=tout1); u3: led PORT MAP(emg2=emg, clk2=fenpin2, statein=state, ledout=tout);end;2、fenpin(底层分频模块)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity fenpin

9、 is port( clkin: in std_logic; -5KHZ时钟输入 clkout1: out std_logic; -1HZ时钟 clkout2: out std_logic); -2HZ时钟end fenpin;architecture art of fenpin issignal temp: integer range 0 to 4999;begin process(clkin) begin if(clkinevent and clkin=1) then if(temp=4999) then temp=0; else temp=temp+1; end if; end if;

10、end process; clkout1=1 when(temp2500) else 0; clkout2=1 when(temp=2500 and temp3750) else 0;end art;3、ztjishuqi(底层状态计数器模块)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity ztjishuqi is port( emg1,clk1: in std_logic; -紧急输入,1HZ时钟输入 stateout: out std_logic_vector(1 downto

11、0); -2位状态输出 daoout2,daoout1: out std_logic_vector(3 downto 0);-倒计时end ztjishuqi;architecture art of ztjishuqi issignal temp: integer range 0 to 13;type State IS (s0,s1,s2,s3); signal current_state, next_state: State;begin process(emg1, clk1) begin if(emg1=0) then if(clk1event and clk1 =1 ) then if(t

12、emp=0 ) then stateout=00; temp=temp+1; daoout2=0100; daoout10 and temp=4) then stateout=00;temp=temp+1;daoout2=daoout2-1; daoout1=daoout1-1; elsif(temp=5 or temp=6) then stateout=01; temp=temp+1; daoout1=daoout1-1; elsif(temp=7) then stateout=10; temp=temp+1; daoout2=0110;daoout17 and temp=11) then

13、stateout=10;temp=temp+1;daoout2=daoout2-1;daoout1=daoout1-1; elsif(temp=12) then stateout=11; temp=temp+1; daoout2=daoout2-1; elsif(temp=13) then stateout=11; temp=0; daoout2=daoout2-1; end if; end if; end if; end process;end art; 4、led(底层led输出模块)library ieee;use ieee.std_logic_1164.all;use ieee.std

14、_logic_unsigned.all;entity led is port(emg2,clk2: in std_logic; -紧急输入,2HZ时钟输入(方波闪烁),1HZ时钟输入 statein: in std_logic_vector(1 downto 0); -2位状态输入 ledout: out std_logic_vector(11 downto 0); -12盏led灯输出end led;architecture art of led is begin process(emg2,statein,clk2) begin if(emg2=1) then ledout ledout c

15、ase clk2 is when 1 = ledout ledout ledout case clk2 is when 1 = ledout ledout= 0; end case; end case; end if; end process;end art;六、调试中出现的问题及解决方法在编写交通的的程序的时候,本人没有碰到太大的技术上的问题(因为本身程序的要求比较简单,模块数也不多)。主要的一些碰到挫折的地方有1、方波闪烁问题:在编译成功连上线之后,发现红绿灯正常,但是黄灯不出现闪烁也不亮。经分析代码后发现,黄灯的信号输入并没有产生方波,而只是一个一个的脉冲,要产生方波需要信号具有一定的占

16、空比。改进代码后此问题迎刃而解。clkout1=1 when(temp2500) else 0; clkout2=1 when(temp=2500 and tempclk,low=clk1,con1=timing);-提供脉冲(校时时不提供)u2: clock60 port map (sclr=clr,stiming=con(0),sclk=tclk,clks=clk1,v0=s0,v1=s1,co=c1);u3: clock60 port map (sclr=clr,stiming=con(1),sclk=tclk,clks=c1,v0=m0,v1=m1,co=c2);u4: clock24

17、 port map (hclr=clr,htiming=con(2),hclk=tclk,clkh=c2,y0=h0,Y=h1,co=c,noon=light);u5: ring port map (cclk=clk1,cc1=c1,cc2=c2,loud=speaker);end arc;底层模块clock24,用于时钟计时、校时及显示library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity clock24 isport( clkh,hclr,hclk,htiming: in std_log

18、ic; y0: out std_logic_vector(3 downto 0); -个位 Y: out std_logic_vector(6 downto 0); -十位 co,noon: out std_logic); -进位,上下午灯end clock24;architecture arc2 of clock24 issignal t1,t0: std_logic_vector(3 downto 0);signal bibibi: std_logic;beginbibibi= clkh when (htiming=0) else hclk; -判断是否处于校时状态process(bibi

19、bi,hclr)beginif (hclr=1) then-清零t0=0000;t1=0000;elsif (bibibievent and bibibi=1) thenif (t1=2 and t0=3 and htiming=0) then -模24进位co=1;else co=0;end if;-计数器if (t0=9) thent0=0000;t1=t1+1;elsif (t1=2 and t0=3) thent0=0000;t1=0000;elset0=t0+1;end if;-计数器END IF;end process;y0=t0;noon=1 when (t11 or (t1=1

20、 and t03) else 0; -上午亮灯,下午灯灭Y = when t1=0000 else -0 when t1=0001 else -1 when t1=0010 else -2 ;end arc2;底层模块clock60,用于分钟、秒钟的计时与校时library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL; entity clock60 is Port ( clks,sclr,sclk,stiming: in std_logic; v0,v1: out std_logic_vector(3 dow

21、nto 0); -个位,十位 co : out std_logic ); -进位end clock60;architecture arc1 of clock60 issignal t1,t0: std_logic_vector(3 downto 0);signal bibibi: std_logic;beginbibibi= clks when (stiming=0) else sclk;-判断是否处于校时状态process(bibibi,sclr)beginif (sclr=1) then-清零t0=0000;t1=0000;elsif (bibibievent and bibibi=1)

22、thenif (t1=5 and t0=9 and stiming=0) then-模24进位co=1;elseco=0;end if;-计数器if (t0=9) thent0=0000;if (t1=5) thent1=0000;elset1=t1+1;end if;elset0=t0+1;end if;-计数器end if;end process;v0=t0;v1=t1;end arc1;底层模块dclk,用于提供1Hz脉冲library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity dclk

23、 isport(high,con1: in std_logic;-con1表示校时按钮 low: out std_logic); -输出1Hz脉冲end dclk;architecture arc2 of dclk issignal temp: integer range 0 to 4999;beginprocess(high,temp,con1)beginif (highevent and high=1 and con1=0) then 在非校时状态if (temp=4999) then -分频,将5KHz做一个模5000的计数器输出temp=0;low=1;elsetemp=temp+1;

24、low=0;end if;end if;end process;end arc2;底层模块ring,用于整点报时library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity ring isport( cclk,cc1,cc2: in std_logic; loud: out std_logic);-响铃end;architecture behavioral of ring issignal count: integer range 0 to 5;signal loud1: std_logic;be

25、ginprocess(cclk,cc1,cc2)beginif (cclkevent and cclk=1) then-每到一个时钟脉冲,如果count符合条件便开始响铃if (count5) then count=count+1;loud1=not loud1; -响铃维持5秒,这样可做到一声一声地响elseloud1=0;end if;end if;if (cc1=1 and cc2=1) then -分钟进位的时候count归0count=0;end if;end process;loud=loud1;end behavioral;六、实验中遇到的主要问题及解决方法问题解决方案如何模拟时

26、钟系统以低位的进位做高位的时钟脉冲(即秒钟进位做分钟的clk,分钟进位做时钟的clk)如何对应时钟输出由于每个计数器都是采用“个位”和“十位”分别计数,则使该位连接到相应的灯上输出即可,最高位则使用七段译码器进行转换,因此增加一个LED的模块实现该功能如何显示上下午两个层面:1.时钟采用24进制计时;2.增加一个管脚连灯,判断当时钟为0,12区间内则亮灯,否则灭灯。如何提供1Hz的时钟脉冲在dclk模块里做一个模5000的计数器,使得5KHz做输入,进位做1Hz时钟输出。如何实现校时功能加入一个暂停键和三个控制键,当需要校时的时候则停下时、分、秒的计时,同时选择相应的控制按钮来分别调节时钟,此

27、时的脉冲由手动摁下QD给出如何实现整点报时采用秒钟的clk做时钟脉冲,每来一个时钟时如果count5,则count加1同时响铃,否则不响铃。每当有分钟进位的时候,让count=0,则count又可以继续计数,再次响铃。 具体问题可见调试日志七、层次设计的体会本实验由一个顶层模块clock来整合实现整个时钟系统的所有功能,其下有四个模块:dclk(提供1Hz脉冲),clock24(时钟计数器),clock60(分钟、秒钟计数器),ring(实现整点报 时),其中clock60会在主模块中调用两次,对应不同的参数以分别实现分钟、秒钟的功能。在顶层模块中调用其他底层模块,使得各部分功能并发进行。八、

28、实验分工 本实验由陈陈主编,调试及记录文档。实验五:药片装瓶系统设计一、实验目的掌握较复杂逻辑的设计、调试。采用VHDL语言,或原理图+VHDL语言来设计数字系统。学习数字系统设计方法。掌握ispLEVER软件的使用方法。熟悉ISP器件的使用。二、实验所用器件和设备在系统可编程逻辑器件ISP1032一片示波器一台万用表或逻辑笔一只TEC-5实验系统,或TDS-2B数字电路实验系统一台三、实验内容如图5-1左面所示,药片由输送管送入漏斗装置中,后者颈部每次只允许一粒药片掉进传送带上的瓶子里。漏斗的颈部有一个光传感器,它探测到每一粒药片后产生一个电脉冲信号。这个脉冲传送到计数器中,使其计数加1,这

29、样在药片装入瓶子过程的任一时刻,计数器都保存着瓶子中药片数量的二进制数。这个二进制数以计数器通过并行导线传送到比较器的输入端B。另一方面,每个瓶子中要装入的固定药片数量(例如50片)通过键盘手动设置。按键信号经过编码器编码后送到寄存器A保存,而代码转换器A将寄存器A中的BCD数变成二进制数送到比较器输入端A。假设每个瓶子要装50粒药片,当计数器的数值达到50后,比较器的A=B输出端出现高电平,指示瓶子已装满,立即关闭漏斗颈上的阀门使药片停止下落,与此同时它使传送带移动下一个瓶子到漏斗的下面。当瓶子到达漏斗颈正下方时,传送带的控制电路产生一个脉冲信号使计数器清0,比较器A=B输出端变成低电平,打

30、开漏斗阀门,重新开始药片滴落。图5-1 药片装瓶计数显示系统框图结合上面的药片装瓶系统设计实例,采用VHDL设计,并用ISP1032E大容量器件实现如图5-2所示的药片装瓶系统。实验台上的5个数码管作为显示系统,显示每瓶药片及总药片的数量。用实验台的红绿发光二极管来模拟对机电装置系统的输出,绿色灯亮表示启动机电装置,装瓶进行中;红色灯亮表示装瓶完成,机电装置关闭。输入子系统为包括BCD码每瓶装药数输入与装瓶开始脉冲输入,设计要求每瓶最大药片数50粒,最多装18瓶。启动装瓶开始脉冲后,如果输入数量超出最大装瓶数或者为零,要求显示系统出现告警提示。漏斗感应器送来的药片装瓶信号用2s信号模拟,可以用

31、实验台提供的5kHz的时钟分频产生。在实验台上调试设计。图5-2 药片装瓶系统四、设计思路图5-3示出了药片装瓶控制与显示系统的组成总框图,它可以划分为如下七个子系统:装瓶量计数模块 用进位来对总瓶数进行计数 单瓶药片计数模块 用时钟脉冲来对药片数进行计数分频模块 对5kHz的脉冲进行分频药片总量计数模块 用时钟脉冲来对药片数进行计数选择器模块 对开始暂停信号进行判断决定输出瓶数还是当前药片数五、设计方案(代码)library ieee;use ieee.std_logic_unsigned.all;use ieee.std_logic_1164.all;entity yaopian is定义

32、接口port(start,clk,zero: in std_logic;suminput,botnum: in std_logic_vector(7 downto 0);tabletsum2,tabletsum1,tabletsum0: out std_logic_vector(3 downto 0);warn,lighton,lightoff: out std_logic;outsum1,outsum0: out std_logic_vector(3 downto 0);end;architecture behavioral of yaopian iscomponent divider分频模

33、块port(clk1in: in std_logic;clk1out:out std_logic);end component;component tabsum药片总数计数模块port(start2,clk2,zero2: in std_logic;a,b: out std_logic;tabletsum22,tabletsum21,tabletsum20:out std_logic_vector(3 downto 0);end component;component btsum单瓶药片数计数port(start3,clk3,zero3: in std_logic;suminput3: in

34、std_logic_vector(7 downto 0);co3: out std_logic;output31,output30: out std_logic_vector(3 downto 0);end component;component botsum药瓶计数port(start4,co4,zero4: in std_logic;output41,output40: out std_logic_vector(3 downto 0);botnum4: in std_logic_vector(7 downto 0);warn4: out std_logic);end component;c

35、omponent chooser选择器port(start5:in std_logic;botsum51,botsum50,tabletsum51,tabletsum50: in std_logic_vector(3 downto 0);output51,output50: out std_logic_vector(3 downto 0);end component;signal tempclk,tempco,a: std_logic;signal temptsum1,temptsum0,tempbsum1,tempbsum0: std_logic_vector(3 downto 0);beg

36、inu1: divider port map(clk,tempclk);u2: tabsum port map(start,tempclk,zero,lighton,lightoff,tabletsum2,tabletsum1,tabletsum0);u3: btsum port map(start,tempclk,zero,suminput,tempco,temptsum1,temptsum0);u4: botsum port map(start,a,zero,tempbsum1,tempbsum0,botnum,warn);a= tempclk when suminput=1 else t

37、empco;u5: chooser port map(start,tempbsum1,tempbsum0,temptsum1,temptsum0,outsum1,outsum0);end behavioral;library ieee;use ieee.std_logic_unsigned.all;use ieee.std_logic_1164.all;entity botsum isport(start4,co4,zero4: in std_logic;output41,output40: out std_logic_vector(3 downto 0);botnum4: in std_lo

38、gic_vector(7 downto 0);warn4: out std_logic);end;architecture behavioral of botsum isbeginprocess(co4,zero4,start4)当有进位时药瓶计数beginif(zero4=1) thenoutput41=0000;output40=0000;elsif(co4event and co4=1 and start4=1) then-if(output41=1001 and output40=1001) then-output41=0000;-output40=0000;-elsif(output

39、40=1001) then-output41=output41+1;-output40=0000;-else-output40=output40+1;-end if;if (output40=1001) thenoutput40=0000;if (output41=1001) thenoutput41=0000;elseoutput41=output41+1;end if;elseoutput4010001) then-warn4=1;-else-warn4=0;-end if;end if;end process;warn4=botnum4) else超过额定瓶数时报警0;-process(

40、sum)-begin-if(sum18) then-warn4=1;-else-warn4=0;-end if;-end process;end behavioral;library ieee;use ieee.std_logic_unsigned.all;use ieee.std_logic_1164.all;entity btsum isport(start3,clk3,zero3: in std_logic;suminput3: in std_logic_vector(7 downto 0);co3: out std_logic;output31,output30: out std_lo

41、gic_vector(3 downto 0);end;architecture behavioral of btsum is-signal tout31,output30: std_logic_vector(3 downto 0);beginprocess(clk3,start3,zero3)当有时钟脉冲时开始计数beginif(zero3=1) thenoutput31=0000;output30=0000;elsif(clk3event and clk3=1 and start3=1) thenif(output31&output30=(suminput3) thenco3=1;outpu

42、t31=0000;output30=0001;elsif(output31&output30(suminput3) thenif(output30=1001) thenoutput31=output31+1;output30=0000;co3=0;elseoutput30=output30+1;co3=0;end if;end if;end if;end process;end behavioral;library ieee;use ieee.std_logic_unsigned.all;use ieee.std_logic_1164.all;entity chooser isport(sta

43、rt5:in std_logic;botsum51,botsum50,tabletsum51,tabletsum50: in std_logic_vector(3 downto 0);output51,output50: out std_logic_vector(3 downto 0);end;architecture behavioral of chooser isbeginprocess(start5)beginif(start5=0) then暂停时输出瓶数output51=botsum51;output50=botsum50;else计数时输出单瓶药片数output51=tabletsum51;output50=tabletsum50;end if;end process;-output51=botsum51 when start5=0 else- tabletsum51;-output50=botsum50 when start5=0 else- tabletsum50;end behavioral;libr

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。