2011年远程EDA设计题目

2011年远程EDA设计题目

《2011年远程EDA设计题目》由会员分享,可在线阅读,更多相关《2011年远程EDA设计题目(11页珍藏版)》请在装配图网上搜索。

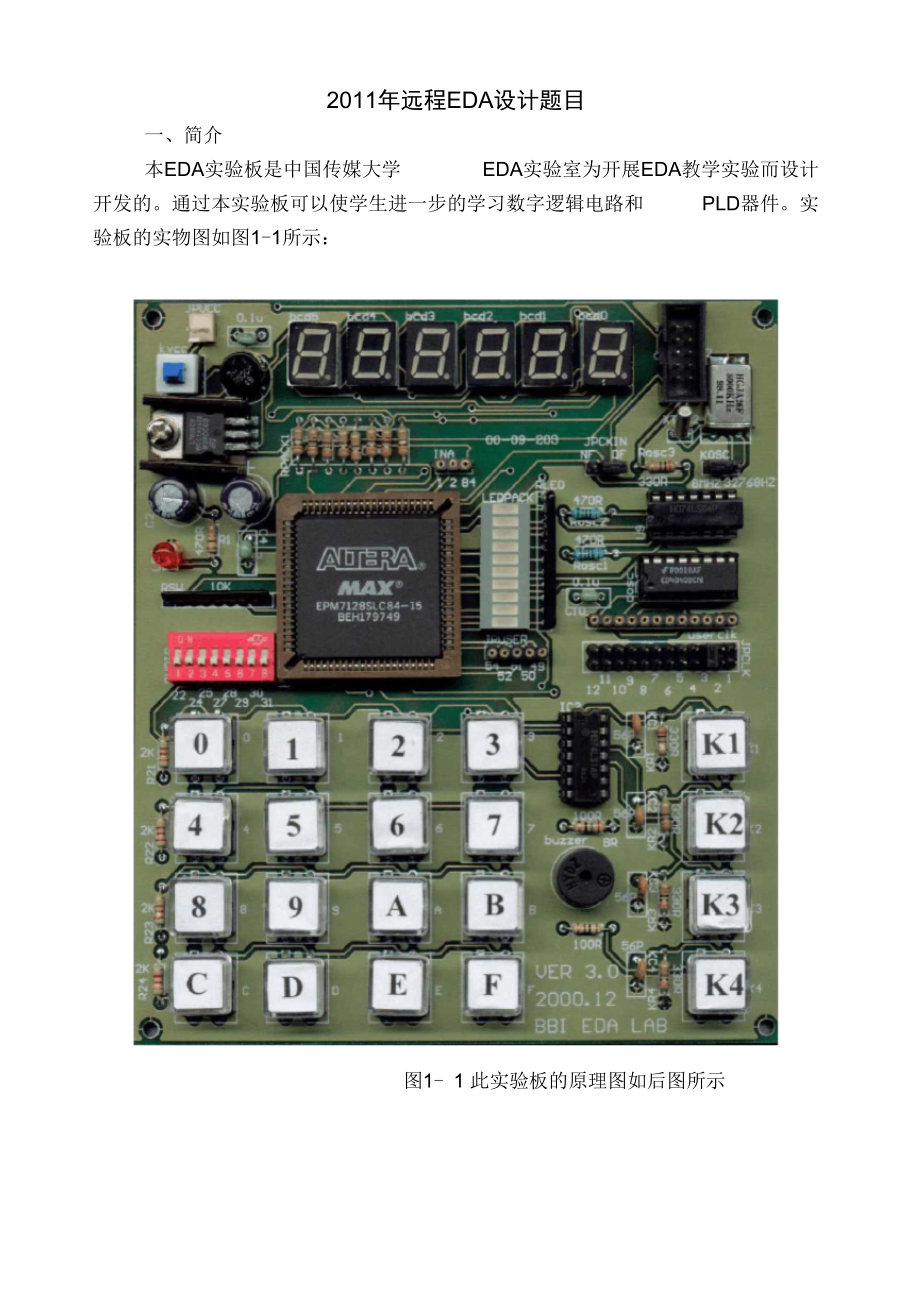

1、2011年远程EDA设计题目一、简介本EDA实验板是中国传媒大学 EDA实验室为开展EDA教学实验而设计 开发的。通过本实验板可以使学生进一步的学习数字逻辑电路和 PLD器件。实 验板的实物图如图1-1所示:图1- 1 此实验板的原理图如后图所示b cd 0/SEGM ENIb cd 1g f7SEGM ENTGNkKJP C K I N43 0R41LS 0 44LS0I C74134RLE330b u zzer BUZZERd o s c404 0K O S C2 屮 8.7 6.5 4 点b cd 28DG3DGg. 一 f03bENTcd 37SEGM ENTb cd 4g fa79l

2、aga7SEGM ENT7SEGM ENT101Ro s c24 7 ORCI N A34 7 OR175767778丄 X TA L 红 XT A L l|I 3 2768HZ8.0 0 M Hz9 A4LSGZIC79808182 84-7R PLED1C 4I1uC 2220 uB r i d g127805k v ccC 1*S W 0KJP C L K I DC24u ser cl k1-23456789101112PPPPPPPPDD DD DDDDD NGram12,4 56 7 3$9 3 7 6 5 4 3 * 4血1 : ; 4 5 6 7L eS W D I P? 2 2

3、 !k电子设计自动化VCC I /c I /O I /O I /OI /OGN) I /OVCC494i51GND丿OOO OOO/ / IV/C 8 7,CCI/O I/OI/O/O:/O/OGN) I/O| C 8 1卜/O7 NPUT/OE2 / GCLK22 PlO O C )OOODOOO / V O I / DI O /482 3 4 5 * 7 * 9 2 2 23 *浙(C 8 6C 8 3O O C O O O oO D I I V I / / I GI/O-VCCI/OC/O$N) 8NPUT/GCLK1 2NPUT/OE11 NPUT/ GCLRnJP U S E R22

4、0 u fI535240yek30yek20yek10yekC3-DOO8_ c r-7_D 06_D ID5-DT77?: /O/OVCC/O/O/O/O/O403936333C2C1C0C 3h- 2h 1h- 0h1K R 1鬥20*K C 1JL311156PLK R 58 i:E Y 11414K R 2K C 2E Y 2卄5 6P414第2页共9页K R 3K C 3K R 4K C 4卄56PHF5 6P本实验板的版本号是VER3.0 ,其开发环境是 ALTERA 公司的 MAX+PLUS2,其器件支持为 ALTERA公司PLCC84封装的MAX7000S系列芯 片,或者是与其

5、兼容的其它PLD芯片。EPM7000S系列芯片是ALTERA公司比较典型的PLD芯片,具有在线可编 程的功能,在具体实验我们选择了 EPM7128SLC84-15芯片。EPM7128SLC84-15 具有128个宏单元,2500个左右的可用门,PLCC 84封装,60个I/O引脚,4 个专用输入引脚(引脚图参见课本 P106)。可以满足中小规模实验的要求,如果 设计的规模比较大可以考虑使用 EPM7256S等芯片,其管脚是相互兼容的,只 是内部包含更多的逻辑单元。本实验板提供并口下载电缆一条,此电缆是针对ATMEL公司ATF1508AS 的,和ALTERA公司的BYTEBLASTER并不兼容。

6、实验板上有一个JTAG输入 接口,将此并口电缆和实验板上的接口连接就可以实现 JTAG编程下载。下载电缆只可以从一个方向插入 JTAG接口(有关下载电缆的详细资料请参阅有关资料)PLD芯片和其外围电路需要使用+5V的 直流稳压电源供电才能正常工作,实验板上自 己带有整流和稳压电路,可以使用 7.5到9伏左右能够提 供250mA以上电流的交流电源或直流电源供电。实验板上有一个电源开关,用来关闭或开启电源,电 源的开启或关闭可以通过发光二极管来指示,电源开启时 发光管点亮,否则熄灭。切记:不能在加电时插拔JTAG下载电缆,如要插拔下载电缆一定要关断 电源。二、使用说明1 关于时钟的使用说明:实验板

7、上有一个8MHZ的晶振,与74LS04组成时钟源。此时钟信号 一路送到跳线JPCKIN的NF端,当跳线跳到此端时,8MHZ时钟直接输 入到PLD芯片的83脚。另一路信号送到2的14级分频器CD4040 上,CD4040的输出经跳线JPCLK选择分频比送到跳线JPCKIN的DF端,由 此可以得到频率较低的时钟源送到 PLD芯片的83脚。当跳线JPCLK在1 端时,为2 1分频,当在12端时,为2 12分频。具体的频率值见下表。跳线端121110987频率Hz1953.13906.37812.5156253125062500跳线端654321频率Hz125000250000500000100000

8、0200000040000002 关于键盘输入使用说明:本实验板键盘输入分两部分,4个独立的按键,16个扫描识别的按键。4个独立的按键每个分别对应一个I/O 口,由原理图知,4个独立按键经施 密特非门做防抖输入。当按键没有按下时,施密特触发器的输入端通过电阻接 地,输出端为高电平,当按键按下时施密特触发器的输入端通过限流电阻接 VCC,因此输出端为低电平。(具体管脚的接口见附表)16个按键受I/O 口数量限制接成扫描形式,按4行4列的形式排列。4个行 信号C0、C1、C2、C3 一端经2K限流电阻后与VCC相连,另一端接PLD芯片 的4个输入口,因此当没有按键按下时,4个行信号始终为高。4个列

9、信号H0、 H、1H2、H3与PLD芯片的输出口相连,此四个端口顺序输出低电平,即同一 个时刻只有一个列信号输出低电平,其他三个输出高电平。因此当按键按下时,低电平的列,会将所对应的行信号电平拉低,由此就可以确定是哪个按键按下。 (具体管脚分配见附表)3DIP 开关的使用说明:实验板中包含 8 个 DIP 开关,每个 DIP 开关一端接地另一端接一个管脚, 每个管脚同时经过一个10K电阻接VCC。因此当DIP开关在OFF时,管脚电平 为高,当 DIP 开关为 ON 时,管脚电平为低。这样可以使管脚保持恒定的高或 低电平。(具体管脚分配见附表) 4发光排的使用说明:实验板中有一个 10 段发光排

10、, 每段发光管的正端接 PLD 芯片的 I/O 口,负 端通过限流电阻接地。当芯片输出高电平时发光管发亮否则熄灭。 (具体管脚分 配见附表)5蜂鸣器的使用说明:PLD 芯片的 56 脚输出经两级非门放大后送到蜂鸣器的正端,由此当 56 脚 输出高电平时,蜂鸣器发声,否则无声。 (适用于乐曲的演奏等实验) 6数码管的使用说明:实验板上有 6 个共阴极 7 段数码管,每个数码管的 A-F 连接在一起经限流 电阻后接到 PLD 芯片的 7 个 I/O 口,每个数码管的阴极分别接到 PLD 芯片的一 个 I/O 口。由此可以通过数码管阴极的电平来选通数码管, 当阴极电平为高时数 码管熄灭,当阴极电平为

11、低时数码管可以点亮。 这样6个数码管的阴极y0-y5通 过轮流输出低电平来选通某个数码管,某个时刻只有一个选通端输出低电平, 当选通的速度比较快时,因视觉暂留现象人眼观察到的数码是稳定显示的。 7其他使用说明:实验板上将没定义的几个 I/O 口和专用输入引脚通过插针孔引出。 专用引脚 为INA,I/O 口为JPUSER,其对应的管脚在板上标出。这些接口可以扩展实验 板的应用。比如用到第二时钟源时就可以用导线将时钟由的 2端 INA 引入 PLD 丄芯片。提示:1、外部输入的时钟虽然已经经过 CD4040分频,但是频率依然很高,需 要在芯片的内部将输入时钟再进行分频。由此提供秒脉冲,控制发光排的

12、闪亮。三、设计内容:交通灯控制器设计一个由一条主干道和一条支干道的汇合点形成的十字交叉路口的交通电子设计自动化( EDA )课程考试要求及答卷 第 5 页 共 9 页灯控制器。主干道有红黄绿三个交通灯(R1Y1G1),支干道有红黄绿三个交通 灯(R2Y2G2) , CLK是时钟输入端,在支干道处有一个按钮 X,用于行人控制交 通灯,正常状态无人按下X,此时X=1,主干道绿灯亮,支干道红灯亮;有人按 下按钮X=0,主干道和支干道黄灯亮,5秒后,主干道红灯亮,支干道绿灯亮, 再30秒后,主干道和支干道黄灯亮,再5秒后,主干道绿灯亮,支干道红灯亮; 如此循环。CLK X j交通灯控制器TO W主干道

13、 支干道R1 Y1 G1 R2 Y2 G2该设计有2个输入端,6个输出端。各端口对应在板子上的管脚定义:CLK定义在83脚CLK上, X定义在44脚KEY1 上, R1定义在70脚发光排1 上, Y1定义在69脚发光排2上, G1定义在68脚 发光排3上, R2定义在61脚发光排8 上, Y2定义在60脚发光排9上, G2定 义在58脚发光排10上。需要完成的设计内容:1、写出实现上述功能的设计思路,尽量详细(30分).2、在中设计完成上述功能,可以用原理图或者 VHDL ,并完成编译和仿真,将设计文档打包提交.(即将整个设计项目所在的目录用.RAR压缩后提交一个.RAR文件,需要包含设计所用

14、到的GDF或者VH DL文件,仿 真生成的Swf文件,以及下载所需要的Pof文件)(50分)3、 教师将提交的Pof文件写入PLD硬件时可以完成上面的功能要求 (20分)附件一:7000S实验板管脚定义管脚号管脚名称实验板上名称管脚号管脚名称实验板上名称11/O7段译码器中A56I/O蜂鸣器输出RING10/O7段译码器中B37I/O键盘输入的C09/O7段译码器中C39I/O键盘输入的c18/O7段译码器中D40I/O键盘输入的c26/O7段译码器中E41I/O键盘输入的c35/O7段译码器中F33I/O键盘输入的h04/O7段译码器中G34I/O键盘输入的h181/O7段译码器中DOT35

15、I/O键盘输入的h222/ODIP136I/O键盘输入的h324/ODIP283CLK时钟输入CLK25/ODIP320I/O数码管0的选择口27/ODIP417I/O数码管1的选择口28/ODIP515I/O数码管2的选择口29/ODIP618I/O数码管3的选择口30/ODIP716I/O数码管4的选择口31/ODIP812I/O数码管5的选择口44/O独立按键KEY184OE自定义输入接口 INA45./O独立按键KEY21GCLR自定义输入接口 INA46/O独立按键KEY32GCLK2自定义输入接口 INA48/O独立按键KEY449I/O自定义输入接口 JPUSER70/O发光排1

16、50I/O自定义输入接口 JPUSER69./O发光排251I/O自定义输入接口 JPUSER68/O发光排352I/O自定义输入接口 JPUSER67/O发光排454I/O自定义输入接口 JPUSER65/O发光排564/O发光排663/O发光排761/O发光排860/O发光排958/O发光排10注意事项:1、考生须在答卷封面上写明学号、姓名及所在学习中心, 并与答题内容装订在一起。答卷封面见下页(请考生下载打印, 并按照此封面样式完成答卷)。2、请考生务必于本学期课程考试时(2011年10月21日 至23日)将答卷交到当地学习中心,逾期不交者,考试成绩以0分计。2 0 1年10月课程考试答卷课程名称:电子设计自动化(EDA年级:层次:专业:学号:姓名:学习中心:成绩:教师签名:中国传媒大学现代远程教育年 月 日

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 中移动绩效管理系统1课件

- 第五节维生素D缺乏性佝偻病ppt课件

- 登革热主题班会ppt课件

- 新生儿持续肺动脉高压诊治进展课件

- 新湘少版三年级英语上册Unit2goodmorning课件

- 新生儿呼吸窘迫综合症(Neonatal-Respiratory-Distress-Syndrome)课件

- 中移动滚动规划中关于流量经营的考虑课件

- 电气排故高级证ppt课件

- 新浙教版-九年级科学上-第一章复习课件

- 把握新高考的难得机遇做一位成功的高考考生ppt课件

- 新生儿缺氧缺血性脑病课件

- 中科院讲义-分布式操作系统-Peterson和Dekker算法证明教学课件

- 新生儿巨细胞病毒感染课件

- 大学生恋爱观及恋爱问题的应对策略ppt课件

- 新生儿惊厥ppt课件