常用时序逻辑电的分析

常用时序逻辑电的分析

《常用时序逻辑电的分析》由会员分享,可在线阅读,更多相关《常用时序逻辑电的分析(74页珍藏版)》请在装配图网上搜索。

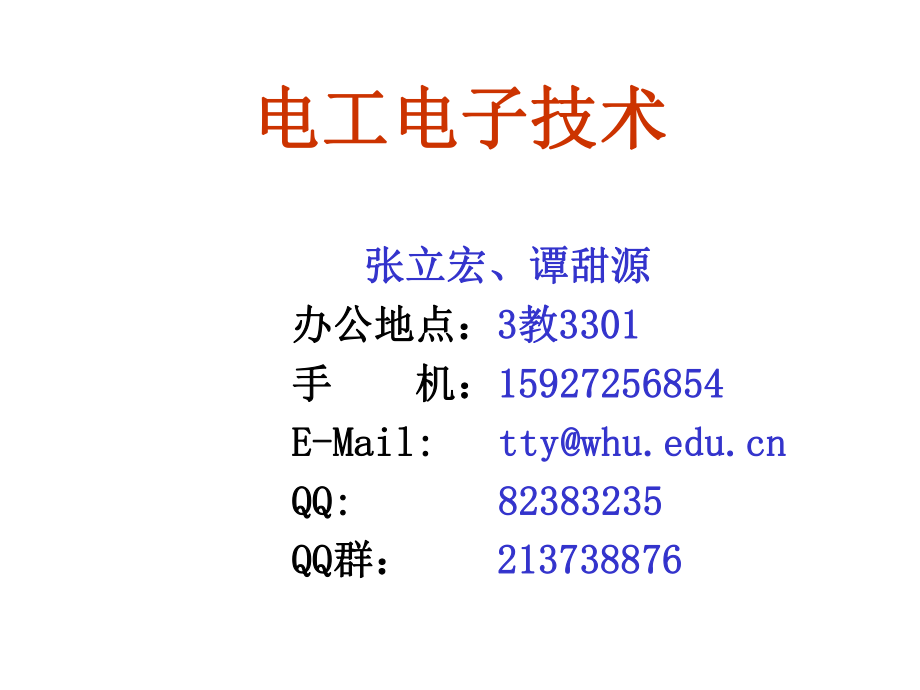

1、电工电子技术电工电子技术 张立宏、谭甜源张立宏、谭甜源 办公地点:办公地点:3 3教教33013301 手手 机:机:1592725685415927256854 E-Mail: E-Mail: QQ: QQ: 8238323582383235 QQ QQ群:群: 213738876213738876第十次作业参考答案双稳态触发器的分类双稳态触发器的分类按逻辑功能不同分按逻辑功能不同分T T(ToggleToggle)触发器触发器D D(DelayDelay)触发器触发器J JK K触发器触发器 同步触发器同步触发器R RS S触发器触发器基本触发器基本触发器边沿触发器边沿触发器按电路结构不同

2、分按电路结构不同分主从触发器主从触发器回顾回顾基本基本R-S触发器触发器& A& BQQSDRDQQSDRDSDRD Qn+1 0 0 0 1 1 0 1 1不定不定 Qn01置位端置位端复位端复位端 基本基本RSRS触发器触发器: 00 00态不定,态不定,11 11 态不变,其余同态不变,其余同R R记记 1 1nnQSQRSR回顾同步同步R-S触发器触发器& AQQSD& BRD& C& DSRCQQRDSDSRC同步同步RS触发器,状态翻转要触发器,状态翻转要CP 00不变不变11乱,乱, 其余雷同其余雷同S记。记。01RSRQSQnn特征方程:特征方程:CPSR Qn+10XXQn1

3、 1 1不定1 1 0 11 0 1 01 00 Qn回顾主从主从J-K触发器触发器C1RDSDSRQQSRQQ&QKJQQQRDSDKJC特征方程特征方程JKQn+11110 01 00nQ JKJK触发器,触发器,1111把数计,把数计,0000态不变,其余同态不变,其余同J J记记 JJnQnnnQKQJQ1双稳态触发器双稳态触发器 基本基本RSRS触发器触发器: 00 00态不定,态不定,11 11 态不变,其余同态不变,其余同R R记记 JKJK触发器触发器: 00 00态不变,态不变, 11 11态翻转,其余同态翻转,其余同J J记记 同步同步RSRS触发器触发器: 00 00态不

4、变,态不变,11 11 态不定,其余同态不定,其余同S S记记 D D触发器触发器: 同同D D记记 T T触发器触发器: 0态不变,态不变, 1态翻转态翻转TT触发器触发器: 随时钟脉冲随时钟脉冲翻转翻转1 0nnQSQRS RnnnQKQJQ1nnDQ1nnnQTQTQ1nnQQ11 1nnQSQRSR回顾回顾时序逻辑电路分析时序逻辑电路分析 时序逻辑电路:时序逻辑电路:输出变量状态输出变量状态不仅取决于当时的输入状不仅取决于当时的输入状态,还态,还与电路原来状态有关与电路原来状态有关。 组组合合电电路路 I O 存存储储电电路路 E S i j k m * *电路由组合电路和存储电路(其

5、核心为触发器)组成。电路由组合电路和存储电路(其核心为触发器)组成。 * *电路存在反馈。电路存在反馈。 结构特征结构特征: : 根据电路中各触发器状态变化时刻是否统一,根据电路中各触发器状态变化时刻是否统一,时序时序逻辑电路分为逻辑电路分为同步同步时序电路和时序电路和异步异步时序电路。时序电路。回顾时序逻辑电路的逻辑功能四种表示方法时序逻辑电路的逻辑功能四种表示方法 1D C1 & 1 & D0 Q0 FF0 Q0 & 1 1D C1 D1 Q1 FF1 Q1 Y A CP 输出方程输出方程A)QQ(Y10 A)QQ(D100 AQD01 驱动方程驱动方程 A)QQ(Qnnn1010 AQQ

6、nn011 状态方程状态方程1. 1. 逻辑方程组逻辑方程组时钟方程时钟方程12CCC回顾时序逻辑电路的逻辑功能四种表示方法时序逻辑电路的逻辑功能四种表示方法2. 2. 状态转换真值表状态转换真值表0 1 / 00 0/ 11 11 1 / 00 0 / 11 01 0 / 00 0 / 00 00 1 / 00 0/ 10 1状态表状态表nnQQ01YQQnn/1011A=1A=0状态转换真值表状态转换真值表010100011100010111011101001110100010001100000000nQ1nQ011nQ10nQYA回顾时序逻辑电路的逻辑功能四种表示方法时序逻辑电路的逻辑功

7、能四种表示方法3. 3. 状态图状态图 10 11 00 01 0/0 1/0 0/1 10 11 00 01 1/0 0/11/00/11/04. 4. 时序图时序图 CP A Q0 Q1 Y Q1Q0A/Y 时序逻辑电路的四种描述方式是可以相互转换的时序逻辑电路的四种描述方式是可以相互转换的 一个最简单的寄存器是能寄存一位二进制的数,它只需一个最简单的寄存器是能寄存一位二进制的数,它只需一个与非门和一个触发器组成。寄存多位二进制数,则需多一个与非门和一个触发器组成。寄存多位二进制数,则需多组一位寄存器组成。常用的有四位、八位、十六位等。组一位寄存器组成。常用的有四位、八位、十六位等。6.6

8、.2 6.6.2 寄存器寄存器1. 1. 组成及分类组成及分类 寄存器由寄存器由逻辑门逻辑门和和触发器触发器组成。组成。 寄存器是最基本的数字部件之一,它是用来寄存器是最基本的数字部件之一,它是用来暂时暂时存放参存放参与运算的数码(数据)和中间结果。与运算的数码(数据)和中间结果。(3)按取出方式分)按取出方式分(2)按存放方式分)按存放方式分(1)按其功能分)按其功能分代码寄存器代码寄存器(无移位功能)(无移位功能)移位寄存器移位寄存器(有移位功能)(有移位功能)并行并行(多用于代码存取)(多用于代码存取)串行输入串行输入(多用于移位)(多用于移位) 并行并行(多用于代码存取)(多用于代码存

9、取)串行输出串行输出(多用于移位)(多用于移位)QDQDQDF0F1F2Q2Q1Q0&2.2.数码寄存器数码寄存器(1 1)逻辑电路)逻辑电路(2 2)工作过程)工作过程取数取数寄存寄存 1 1)存放数码)存放数码2 2)取数)取数 该电路是由该电路是由D触发器组成的触发器组成的寄存器,当寄存脉冲出现时,寄存器,当寄存脉冲出现时,接收并保存输入端的数码到接收并保存输入端的数码到D D触发器的状态输出,以被后续触发器的状态输出,以被后续电路取用。电路取用。D2=1D1=0D0=1110110 该该寄存器的输入、输出也是寄存器的输入、输出也是并行方式并行方式。 可见,来一个脉冲数据向右移一位。经过

10、可见,来一个脉冲数据向右移一位。经过3个脉冲后,个脉冲后,Q0Q1Q2 =101,而且而且Q0已串行输出了已串行输出了101。再经过。再经过3个脉冲将个脉冲将从从Q1、Q2端分别输出端分别输出101,同时也将移出寄存器。,同时也将移出寄存器。010100103. 3. 移位寄存器移位寄存器(1 1)逻辑电路逻辑电路 前面介绍的寄存器为前面介绍的寄存器为并行并行输入输出方式,若要实现数据输入输出方式,若要实现数据从一个端子从一个端子串行串行输入时,那么寄存器必须具备移位功能。移输入时,那么寄存器必须具备移位功能。移位寄存器在计算机通信中应用广泛。位寄存器在计算机通信中应用广泛。 移位寄存器分左移

11、、右移和双向位移三种方式。下面移位寄存器分左移、右移和双向位移三种方式。下面以以3位右移寄存器位右移寄存器为例介绍器移位的原理。为例介绍器移位的原理。DRQ0Q1Q2QQJKF1QQJKF2QQJKF01C(2 2)工作过程)工作过程 0 1 0 1 0 0 0 0 0 1 0 1 0 0 0 0 0 1 0 1 0 0 0 0 0 1 0 1 0 0 0 0 0 1 0 1 0 0 0 0 0 1 0 1 0 0 0 0 0 1 0 1 0 0 0 0 0 1 0 1 0 0 0 0 0 1 0 1 0 0 0 0 0 1 0 1 0 0 0 0 0 1 0 1 0 0 0 0 0 1 0

12、1 0 0 0 0 0 1 0 1 0 0 0 0 0 1 0 1 0 0 0 0 0 1 0 1 0 0 0 0 0 1 0 1 0 0 0 0 0 1 0 1 0 0 0 0 0 1 0 1 0 0 0 0Q0Q1Q2C 1 0 1可见移位寄存器既可以实现串行输出,也可以实现并行输出。可见移位寄存器既可以实现串行输出,也可以实现并行输出。1 2 3 4 5 6(3 3)工作波形)工作波形1000101001000000000174LS19411623456789101112131415GEDRDDSRD0Q0Q1Q2+VCCD1D2D3DSLQ3CM1M0 1)管脚排列图管脚排列图CR R

13、D M0 M1 C 功功 能能 0 1 0 0 1 0 1 1 1 0 1 1 1 置置“0”保持保持右移右移左移左移并行输入并行输入 2)功能表)功能表左左移移输输入入功能控制端功能控制端时钟输入时钟输入74LS194是一种双向是一种双向4位移位寄存器,即内部由位移位寄存器,即内部由4个个R-S触触发器和各自的输入控制电路组成。其管脚排列如图示。发器和各自的输入控制电路组成。其管脚排列如图示。并并行行输输入入并并行行输输出出CR右右移移输输入入清清零零端端4. 4. 集成寄存器集成寄存器74LS19474LS1946.6.3 6.6.3 计数器计数器计数器的种类繁多,可用不同的方法分类计数器

14、的种类繁多,可用不同的方法分类 计数器的基本功能是对输入计数器的基本功能是对输入时钟脉冲个数时钟脉冲个数进行进行累计累计。它也可用于分频、定时、产生脉冲序列及进行数字运算等。它也可用于分频、定时、产生脉冲序列及进行数字运算等。(1)按计数基数分:)按计数基数分:二进制(二进制(2n类)类)非二进制非二进制(2)按时钟控制方式分:)按时钟控制方式分:(3)按计数方式分:)按计数方式分:同步计数器同步计数器异步计数器。异步计数器。加法计数器加法计数器减法计数器减法计数器 所谓同步是指各触发器是由同一个脉冲触发,而各触发器所谓同步是指各触发器是由同一个脉冲触发,而各触发器的状态翻转同时进行。电路如图

15、所示。的状态翻转同时进行。电路如图所示。1)写出方程式)写出方程式1 1同步计数器同步计数器(1)同步二进制计数器)同步二进制计数器将驱动方程代入特性方程得将驱动方程代入特性方程得 QJKF1QJKF0QJKF2Q2Q1Q0C&时钟方程时钟方程C0= C1 = C2 = C驱动方程驱动方程J0=K0=1 J1=K1= Q0 J2=K2= Q0Q1状态方程:状态方程:J-K触发器的特性方程为触发器的特性方程为 nnnQKQJQ1nnQQ010nnnnnQQQQQ101011nnnnnnnQQQQQQQ210210122)列状态表)列状态表nnQQ010nnnnnQQQQQ101011nnnnnn

16、nQQQQQQQ21021012nQ2nQ1nQ012nQ11nQ10nQ 次 态 初 态输入脉 冲 数000001001010010011011100100101101110110111111000123456783)逻辑功能)逻辑功能nQ2nQ1nQ012nQ11nQ10nQ 次 态 初 态输入脉 冲 数00000100101001001101110010010110111011011111100012345678 由状态表可以看出,它是按二进制加法规律递增计数,即由状态表可以看出,它是按二进制加法规律递增计数,即按自然态序变化,所以它是按自然态序变化,所以它是3位二进制加法计数器,计数长

17、度位二进制加法计数器,计数长度823N同步减法计数器同步减法计数器 1)驱动与控制方程)驱动与控制方程C0= C1 = C2 = CJ0=K0=1 2)工作波形工作波形3)状态表及逻辑功能)状态表及逻辑功能输入脉 冲数各级触发器状态Q2Q1Q0 0 1 2 3 4 5 6 7 0 1 1 1 1 0 0 0 0 1 1 0 0 1 1 0 0 1 0 1 0 1 0 1 8 0 0 0011QKJQJKF1QJKF0QJKF2Q2Q1Q0C&QQQ1022QQKJCQ0Q1Q2(2)同步十进制计数器)同步十进制计数器1)写出各方程)写出各方程式式JQKCF3QJQKCF2QJQKCF1QJQK

18、CF0Q&ZQ0Q1Q2Q3CPDR将驱动方程代入将驱动方程代入J-K触发器的特征方程得到状态方程触发器的特征方程得到状态方程100 KJnnnQKQQJ02301,nnQQKJ1022nnnnQKQQQJ032103,驱动方程驱动方程输出方程为:输出方程为: nnQQZ03nnQQ010状态方程状态方程nnnnnnQQQQQQ2031011nnnnnnnQQQQQQQ21021012nnnnnnnQQQQQQQ303210131nnnQJQKQ触发器特征方程触发器特征方程2)列状态表)列状态表12345678 Z进位进位 次次 态态 初初 态态 计计 数数 顺顺 序序nQ2nQ1nQ0nQ3

19、12nQ11nQ10nQ13nQ00000010010001100010010001101000100010101100111010101100111000010001001101010111001100000111100110011011110111111011110111110000109无效状态0000000001010011nnQQ010nnnnnnQQQQQQ2031011nnnnnnnQQQQQQQ21021012nnnnnnnQQQQQQQ30321013 3)有关概念)有关概念无效状态无效状态自启动电路自启动电路 计数器工作之前,必须通过计数器工作之前,必须通过复位端复位端复位

20、,使复位,使Q0Q1Q2使全部位使全部位0,随后每来一个脉冲,计数器,随后每来一个脉冲,计数器就改变一次状态。就改变一次状态。 任意进制任意进制系指除十进制和二进制(系指除十进制和二进制(2n)计数器外的称计数计数器外的称计数器,即器,即N进制计数器。任意进制计数器可分为进制计数器。任意进制计数器可分为偶数偶数和和奇数奇数进进制两大类。下面以制两大类。下面以3位触发器组成的偶数和奇数进制触发器为位触发器组成的偶数和奇数进制触发器为例,介绍任意进制计数器的组成特点和方法。例,介绍任意进制计数器的组成特点和方法。如果将如果将 反馈到反馈到J0端,它的功能又如何呢?端,它的功能又如何呢?Q0Q1Q2

21、QJF1QJF2QJF0CRDRDRD复位复位QKKKQQ 它是将它是将移位寄存器的移位寄存器的串行输出反相(或非端)后再串行输出反相(或非端)后再反馈反馈到到串行输入端串行输入端,构成的,构成的计数器计数器,此称为扭,此称为扭环型计数器。环型计数器。(3)任意进制计数器任意进制计数器扭环形计数器扭环形计数器工作过程及状态表工作过程及状态表 C Q0 Q1 Q2 0 0 0 1 0 0 1 1 0 1 1 1 1230功能及特点功能及特点 该计数器是一个该计数器是一个六进制六进制计数器,一般计数器,一般n个个触发器触发器可实现可实现2n进制进制的计数器,且为的计数器,且为偶数进偶数进制制计数器

22、。计数器。10001001101110110010002 3 4 5 640 1 1 50 0 1 60 0 0 如图示电路如图示电路1QCRDQJF1QJF2QJF0QKQQKKQ0Q1Q2奇进制扭环计数器奇进制扭环计数器工作过程及真值表工作过程及真值表 计数器工作之前,必须通过计数器工作之前,必须通过复位复位端复位,使端复位,使Q0Q1Q2使全部位使全部位0,随后每来一个脉冲,计数器,随后每来一个脉冲,计数器就改变一次状态。就改变一次状态。 C Q0 Q1 Q2 0 0 0 1 0 0 1 1 0 1 0 1 1230功能及特点功能及特点 以上分析可知,以上分析可知,扭环计数器可以实现任扭

23、环计数器可以实现任意进制计数器,换句话说,意进制计数器,换句话说,n个触发器既可个触发器既可以实现以实现2n进制的计数器,也能实现进制的计数器,也能实现2n-1进制进制计数器,计数器,关键在反馈线的连接关键在反馈线的连接,其规律为:,其规律为:10001001101010110002 3 4 540 1 1 50 0 0 nnQJQK00,前者100nnQJQK,后者如果将如果将Q1 反馈到反馈到K0端,也能实现五进值。端,也能实现五进值。QJF1QJF2QJF0CRDQKQQKKQ0Q1Q21)电路图)电路图2)状态表)状态表 Q0 Q1 Q2 C0 0 0 1 0 0 1 1 0 0 1

24、1 123040 0 1 50 0 0 1 0 10 1 12.2.异步计数器异步计数器(1)确定方程式)确定方程式 这里以十进制电路为例,先介绍用这里以十进制电路为例,先介绍用状态表状态表来分析计数器来分析计数器功能的分析方法,显然这里的关键是列状态表。其电路为功能的分析方法,显然这里的关键是列状态表。其电路为QJKF2QJKF1QJKF3QQQC0 =C 、C1 = Q0 、C2= Q1 、 C3 = Q0 CQJKF0QCQ3Q2Q1Q0&Z时钟方程:时钟方程:驱动方程:驱动方程:特征方程:特征方程:状态方程:状态方程:输出方程:输出方程:J0= K0=1,K1=131QJ J3= Q1

25、Q2 K3=1J2= K2=1,nnnQKQJQ1nnnnQQQQ32113nnQQ212nnnQQQ1311nnQQ010 Z= Q3Q0 (2 2)列状态表)列状态表(3)时序图时序图计数脉冲Z 1 2 3 4 5 6 7 8 9 1012nQ11nQ10nQ13nQnQ0nQ1nQ2nQ3根据状态表,可以很方便的转换成时序图。根据状态表,可以很方便的转换成时序图。nnnnQQQQ32113nnQQ212nnnQQQ1311nnQQ0100 0 0 10 0 0 00 0 0 10 0 1 00 0 1 10 1 0 00 1 0 10 1 1 00 1 1 11 0 0 01 0 0 1

26、0 0 1 00 0 1 10 1 0 00 1 0 10 1 1 00 1 1 11 0 0 01 0 0 10 0 0 00000000010 应用状态方程列状态表时还要考虑各触发器的触发脉冲应用状态方程列状态表时还要考虑各触发器的触发脉冲是否有效。如第是否有效。如第1个次态,若直接将初态代入状态方程计算个次态,若直接将初态代入状态方程计算结果为结果为“0111”,由于,由于Q0 Q1没有下降沿,故没有下降沿,故Q2 Q1不翻转,不翻转,故为故为0001 。C0 =C 、 C2= Q1 、C1 = Q0 C3 = Q0 Z= Q3Q0 (4 4) 时序电路分析举例时序电路分析举例 试分析电

27、路的逻辑功能试分析电路的逻辑功能QJKF1QJKF0QJKF2Q2Q1Q0CQQQ五进制加法计数器五进制加法计数器1)驱动与时钟方程)驱动与时钟方程2)工作波形)工作波形CQ0Q1Q23)逻辑功能分析)逻辑功能分析输入脉输入脉 冲数冲数各级触发器状态各级触发器状态Q2Q1Q0 0 1 2 3 4 5 6 0 0 0 0 1 0 0 0 0 1 1 0 0 0 0 1 0 1 0 0 1 C0 = C2 = C,C1 = Q0 J1= K1=1,K0=120QJ J2= Q1Q0 K2=16.3.4 6.3.4 集成计数器及应用集成计数器及应用 随着集成电路的发展,各种大规模集成计数器已大量的随

28、着集成电路的发展,各种大规模集成计数器已大量的生产和应用,集成计数器也分为生产和应用,集成计数器也分为异步异步集成计数器和集成计数器和同步同步集成集成计数器两大类。计数器两大类。以下各以一种为例,说明它们的方法和扩展应用。以下各以一种为例,说明它们的方法和扩展应用。脉冲引脉冲引入方式入方式型型 号号计数模式计数模式 清零方式清零方式预置数预置数方式方式 同同 步步74161741617474HC161HC16174HCT16174HCT16174LS19174LS19174LS19374LS19374LS16074LS16074LS19074LS1904 4位二进制加法位二进制加法4 4位二进

29、制加法位二进制加法4 4位二进制加法位二进制加法单时钟单时钟4 4位二进制可逆位二进制可逆双时钟双时钟4 4位二进制可逆位二进制可逆十进制加法十进制加法单时钟十进制可逆单时钟十进制可逆异步(低电平)异步(低电平)异步(低电平)异步(低电平)异步(低电平)异步(低电平)无无异步(高电平)异步(高电平)异步(低电平)异步(低电平)无无同步同步同步同步同步同步异步异步异步异步同步同步异步异步异步异步7474LS293LS29374LS29074LS290双时钟双时钟4 4位二进制加法位二进制加法二二五五十进制加法十进制加法无无异步异步(1 1)异步集成计数器)异步集成计数器CT1090(74LS29

30、0)1)逻辑电路及逻辑符号)逻辑电路及逻辑符号CT1090Q3Q0Q1Q2C1C0NS9(2)S9(1)R0(2)R0(1)QJF2QJF3QJF1QKQQKKQ1Q2Q3C1QJF0QKQ0C0二进制计数器二进制计数器五进制计数器五进制计数器RDS9(2)S&S9(1)R&R0(1)R0(2)SDRDRDSDRD3 3)构成十进制计数器)构成十进制计数器2)电路功能)电路功能 R0(1) R0(2) S9(1) S9(2) Q3 Q2 Q1 Q0 1 1 0 X X 0 0 0 0 0 0 X 0 X 1 1 1 0 0 1 X 0 0 X 0 X X 0 X 0 0 X X 0 0 X 计

31、数计数 计数计数 计数计数 计数计数CT1090Q3Q0Q1Q2C1C0N(a) MN采用采用反馈清零法反馈清零法或或反馈置数法反馈置数法跳过跳过M-N个状态个状态反馈清零法反馈清零法例:用例:用74LS290构成九进制计数器构成九进制计数器Q3 Q2 Q1 Q0S9(1) S9(2) R0(1) R0(2) C0 C1 CP0反馈置位法反馈置位法Q3 Q2 Q1 Q0S9(1) S9(2) R0(1) R0(2) C0 C1 CP01(2 2) 同步集成计数器同步集成计数器CT1161CT1161 1)逻辑符号)逻辑符号2)功能表)功能表CT1611162345678910111213141

32、5GEDCrCD0COQ0Q1+VCCQ2Q3TLDD1D2D3P 输输 入入 输输 出出 说说 明明Cr LD P T C D3 D2 D1 D0Q3 Q2 Q1 Q0CO 0 0 0 0 00异步清零 1 0 d3 d2 d1 d0d3 d2 d1 d0同步预置同步预置 1 1 1 1 计数计数CO=TQ3 Q2 Q1 Q0 1 1 0 保持保持CO=T Q3 Q2 Q1 Q0 1 1 0 保持保持0 由于由于CT1161具有异步清零的功能,故可以采用反馈具有异步清零的功能,故可以采用反馈复位信号使复位信号使Cr为零,使计数器在按自然态序计数的过程为零,使计数器在按自然态序计数的过程中,跳

33、过无效状态,而构成所需进制的计数器。中,跳过无效状态,而构成所需进制的计数器。 当当LD=Cr=“1”时,只要使能输入端时,只要使能输入端P、T中有一个为中有一个为“0”电平,此时无论有无计数脉冲电平,此时无论有无计数脉冲C输入,各触发器输入,各触发器的输出状态均保持不变。的输出状态均保持不变。当当LD=Cr=P=T=“1”时,进行计数,时钟上升沿触发。时,进行计数,时钟上升沿触发。 由于预置由于预置D0D3数据进入各触发器中时,需要时钟脉数据进入各触发器中时,需要时钟脉冲配合,故称同步预置。冲配合,故称同步预置。 由于清零不需与时钟脉冲由于清零不需与时钟脉冲C同步,就可以直接完成,同步,就可

34、以直接完成,故称为异步清零。故称为异步清零。(3)电路功能)电路功能(4)扩展应用)扩展应用CT16111623456789101112131415GEDCrCD0ZQ0Q1+VCCQ2Q3TLDD1D2D3P1)异步清零)异步清零2)同步预置)同步预置3)保持)保持4)计数)计数常用常用反馈复位法反馈复位法和和反馈预置法反馈预置法 。例:用例:用CT74LS161构成十进制计数器构成十进制计数器反馈清零法反馈清零法反馈置位法反馈置位法6.6.4 6.6.4 顺序脉冲分配器顺序脉冲分配器 在一些场合,有时候需要有一个在时间上有一定顺序在一些场合,有时候需要有一个在时间上有一定顺序的信号来控制一

35、些操作,能完成这类任务的时序电路就叫的信号来控制一些操作,能完成这类任务的时序电路就叫顺序脉冲发生器,或称分配器、节拍脉冲发生器。组成顺顺序脉冲发生器,或称分配器、节拍脉冲发生器。组成顺序分配器的电路有两类:一类是由序分配器的电路有两类:一类是由一般计数器和译码器组一般计数器和译码器组成的成的;另一类是由;另一类是由移位寄存器和译码器组成移位寄存器和译码器组成的。的。 图示电路可以输出图示电路可以输出8 8节拍脉冲。在实际应用中,需要节拍脉冲。在实际应用中,需要多多少个节拍少个节拍,一般就采用,一般就采用多少进制多少进制的计数器,再配以相应的的计数器,再配以相应的译码器,以得到所需的节拍数。当

36、需要译码器,以得到所需的节拍数。当需要改变节拍的周期改变节拍的周期时,时,可通过可通过改变改变C C脉冲的周期脉冲的周期来实现。来实现。1 .1 .一般计数器译码器型分配器一般计数器译码器型分配器(1 1)电路图)电路图 在时钟脉冲作用下,在时钟脉冲作用下, Y Y0 0Y Y7 7 将依次给出一串脉冲,脉将依次给出一串脉冲,脉冲的周期为冲的周期为8 8T TC C, Y Y0 0Y Y7 7 的输出依次比前一个输出滞后一个的输出依次比前一个输出滞后一个T TC C( T TC C 为时钟脉冲的周期)。为时钟脉冲的周期)。&Y0&Y1&Y2&Y3&Y4&Y5&Y6&Y70Q0Q1Q2Q1Q2Q

37、CJKQQCJKQQCJKQQ&Y0&Y1&Y2&Y3&Y4&Y5&Y6&Y70Q0Q1Q2Q1Q2QCJKQQCJKQQCJKQQ00000000(2 2)状态表)状态表(3 3)工作波形)工作波形态态序序Q Q2 2 Q Q1 1 Q Q0 0 输输出出0 01 12 23 34 45 56 67 70 0 00 0 10 1 00 1 11 0 01 0 11 1 01 1 1Y Y0 0Y Y1 1Y Y2 2Y Y3 3Y Y4 4Y Y5 5Y Y6 6Y Y7 71Y1Y0Y2Y3Y4Y5Y6Y72345678111111112. 2. 移位寄存器型分配器移位寄存器型分配器(1

38、1)环行计数器型脉冲分配器)环行计数器型脉冲分配器 由于环行计数器每个触发器由于环行计数器每个触发器Q端输出端输出已经是顺序脉冲已经是顺序脉冲了,了,因此不再需要加入译码器,就已具有脉冲分配器的功能。因此不再需要加入译码器,就已具有脉冲分配器的功能。QDF1QDF2QDF0Q0Q1Q2CSDRDRD整定整定1 3 2100010001100(2 2)扭环行计数器型分配器)扭环行计数器型分配器1 1)电路图电路图 从状态表可以看出,扭环行计数器从一种状态到另从状态表可以看出,扭环行计数器从一种状态到另一种状态时,只有一个触发器翻转,无须经过中间过度一种状态时,只有一个触发器翻转,无须经过中间过度

39、状态,这样用扭环行计数器和译码器组成的分配器也就状态,这样用扭环行计数器和译码器组成的分配器也就不存在不存在尖峰干扰尖峰干扰。 扭环行计数器型分配器是由扭环行计数器型分配器是由扭环行计数器扭环行计数器与与译码器译码器组成的。组成的。图示电路是由图示电路是由4位位D触发器组成的扭环行计数器型分配器。下触发器组成的扭环行计数器型分配器。下部为扭环行计数器。部为扭环行计数器。0Q0Q1Q2Q1Q2Q3Q3Q&Y0&Y1&Y2&Y3&Y4&Y5&Y6&Y7CDRDQQCDRDQQCDRDQQCDRDQQF0F1F2F3清零清零C2)状态转换表)状态转换表态态序序Q Q3 3 Q Q2 2 Q Q1 1

40、 Q Q0 0 输输出出0 01 12 23 34 45 56 67 70 0 0 00 0 0 10 0 1 10 1 1 11 1 1 11 1 1 01 1 0 01 0 0 0Y Y0 0Y Y1 1Y Y2 2Y Y3 3Y Y4 4Y Y5 5Y Y6 6Y Y7 7本章小结本章小结主要知识点:主要知识点:1.1.掌握掌握RSRS触发器触发器、JKJK触发器触发器、D D触发器触发器和和T T触发器触发器的逻辑功能的逻辑功能2.2.掌握时序逻辑电路的分析方法掌握时序逻辑电路的分析方法3.3.理解常用时序逻辑部件(理解常用时序逻辑部件(寄存器寄存器和和计数器计数器)的)的工作原理工作

41、原理思考题思考题填空题填空题回顾回顾1.组成组成25进制计数器至少需用进制计数器至少需用 个触发器。个触发器。 52. CT74LS161是是4位集成同步二进制加法计数器,如果用它来位集成同步二进制加法计数器,如果用它来实现一个同步十进制计数器,将有实现一个同步十进制计数器,将有 个无效状态。个无效状态。6思考题思考题计算题计算题回顾回顾一、写出图示电路的驱动方程、状态方程,列出状态转换表,一、写出图示电路的驱动方程、状态方程,列出状态转换表,分析电路的逻辑功能,判断是几进制计数器(设分析电路的逻辑功能,判断是几进制计数器(设Q2,Q1,Q0的初始状态均为的初始状态均为“0”)。)。 解:解:

42、10202020nnnnnQQ QQ QQQ11010101nnnnnQQ QQ QQQ各各JK触发器的驱动方程分别为:触发器的驱动方程分别为:JK触发器的特征方程为触发器的特征方程为: 将各将各JK触发器的驱动方程代入其特征方程,可得其状态方程分别为:触发器的驱动方程代入其特征方程,可得其状态方程分别为:002JKQ110JKQ201JQ Q22KQ1nnnQJ QKQ1201222012nnnnnnQQ QQQ QQ Q Q由此可得状态转换真值表为:由此可得状态转换真值表为: Q2nQ1nQ0nQ2n+1Q1n+1Q0n+1000001001010010011011100100000101

43、011110010111001该电路是一个可以自启动的五进制加法计数器。该电路是一个可以自启动的五进制加法计数器。 思考题思考题计算题计算题回顾回顾二、写出图示电路的驱动方程、状态方程,列出状态转换表,二、写出图示电路的驱动方程、状态方程,列出状态转换表,分析电路的逻辑功能,判断是几进制计数器(设分析电路的逻辑功能,判断是几进制计数器(设Q2,Q1的初的初始状态均为始状态均为“0”)。)。 解:解:111nnQQ12121212nnnnnnnQQQQ QQQ各触发器的驱动方程分别为:各触发器的驱动方程分别为:JK触发器的特征方程为触发器的特征方程为: 将各触发器的驱动方程代入其特征方程,可得其

44、状态方程分别为:将各触发器的驱动方程代入其特征方程,可得其状态方程分别为:11DQ221JKQ1nnQD1nnnQJ QKQ由此可得状态转换真值表为:由此可得状态转换真值表为: 该电路是一个四进制加法计数器。该电路是一个四进制加法计数器。 D触发器的特征方程为触发器的特征方程为: Q2nQ1nQ2n+1Q1n+10001011010111100思考题思考题计算题计算题回顾回顾三、图示电路为三、图示电路为JK触发器组成的数字部件,试分析逻辑电路触发器组成的数字部件,试分析逻辑电路的功能,并要求:(的功能,并要求:(1)写出各驱动方程和控制方程;()写出各驱动方程和控制方程;(2)画出画出Q2、Q

45、1、Q0的波形;(的波形;(3)列出真值表。)列出真值表。 解:解:(1)控制(时钟)方程为:控制(时钟)方程为:02CCC10CQ11=1JK(3)波形图为:波形图为: 该电路是一个五进制加法计数器。该电路是一个五进制加法计数器。 (2)驱动方程为驱动方程为: JQKF2JQKF1JQKF0RDCPQ2Q1Q0QQQ020 1nJQK2012 1nnJQ QKQ2Q1Q0100020013010401151006000CQ0Q1Q2(4)状态转换真值表为:状态转换真值表为: 存储器是数字系统和计算机的重要组成部分,它用来存存储器是数字系统和计算机的重要组成部分,它用来存放数据、资料和运算程序

46、等二进制信息。放数据、资料和运算程序等二进制信息。6.7 6.7 存储器存储器磁盘存储器磁盘存储器半导体存储器半导体存储器常见存储器有常见存储器有下面主要介绍半导体存储器。下面主要介绍半导体存储器。光盘存储器光盘存储器 可编程可编程ROM又可以细分为一次可编程存储器又可以细分为一次可编程存储器PROM、光可擦除可编程存储器光可擦除可编程存储器EPROM、电可擦除可编程存储器电可擦除可编程存储器E2PROM等。等。 EPROM和和E2PROM是利用是利用浮栅浮栅技术生产的可编程存储技术生产的可编程存储器。器。从制造工艺上分,可以分为二极管、双极型和从制造工艺上分,可以分为二极管、双极型和MOS型

47、。型。 按存储内容存入方式的不同,按存储内容存入方式的不同,ROMROM又可以分成又可以分成固定固定ROM和可编程和可编程ROM。 6.7.1 6.7.1 半导体存储器半导体存储器半导体存储器的分类半导体存储器的分类TTL电可擦电可擦E E2 2PROMPROM可编程可编程光可擦光可擦EPROMEPROM固定(掩膜式)固定(掩膜式)ROM一次性可编一次性可编PROMPROMMOS可改写型可改写型EPROMEPROMRAM 按存储功能来分,可以分为只读存储器按存储功能来分,可以分为只读存储器ROM和随机和随机存取存储器存取存储器RAM两大类。两大类。 a a、浮栅编程原理、浮栅编程原理(1)浮栅

48、)浮栅MOS管管 为了适应不同的擦除方式,浮栅为了适应不同的擦除方式,浮栅MOS管有两种不同的结构管有两种不同的结构形式,即形式,即 从结构讲,它们比普通的从结构讲,它们比普通的MOS管多了一个完全被管多了一个完全被SiO2包围而包围而隔离隔离的、处于的、处于浮置浮置状态的栅极,因此称为状态的栅极,因此称为“浮置栅浮置栅” 。N+N+PSGD浮栅隧道氧化层浮栅隧道氧化层MOS管管N+N+PSDG浮栅雪崩注入浮栅雪崩注入MOS管管浮置栅浮置栅DSG符号符号 当浮栅上带有负电荷时,使得当浮栅上带有负电荷时,使得MOS管的开启电压变高,如管的开启电压变高,如果给控制栅加上果给控制栅加上VT1控制电压

49、,控制电压,MOS管仍处于截止状态。管仍处于截止状态。 当浮栅上没有电荷时,给控制栅加上大于当浮栅上没有电荷时,给控制栅加上大于VT1的控制电压的控制电压 ,MOS管导通。管导通。25V25VGND5V5VGND iD VT1 VT2 vGS 浮栅无电子 O 编程前 iD VT1 VT2 vGS 浮栅无电子 浮栅有电子 O 编程前 编程后 5V5VGND5V5VGND导通导通截止截止b、浮栅编程与擦除、浮栅编程与擦除1)浮栅雪崩注入与擦除)浮栅雪崩注入与擦除 2)隧道效应注入与擦除)隧道效应注入与擦除 雪崩注入,即在雪崩注入,即在MOS管的漏极与衬底加上高电压管的漏极与衬底加上高电压(25V)

50、,使漏极与衬底的使漏极与衬底的PN结发生雪崩击穿而产生高能量的自由电子,结发生雪崩击穿而产生高能量的自由电子,同时栅极加正电压使高能量的自由电子穿过同时栅极加正电压使高能量的自由电子穿过SiO2层到达浮置栅。层到达浮置栅。 浮栅雪崩注入浮栅雪崩注入MOS管的芯片需要管的芯片需要用光擦除用光擦除,即将器件放,即将器件放在紫外光处照射在紫外光处照射1020min,浮栅上的电子获得足够能量,穿浮栅上的电子获得足够能量,穿过过SiO2层回到衬底中,管子就恢复到原始状态。层回到衬底中,管子就恢复到原始状态。 编程时源极、漏极接地,栅极加编程时源极、漏极接地,栅极加20V的脉冲电压,使衬底的脉冲电压,使衬

51、底中的自由电子通过隧道效应注入到浮置栅。中的自由电子通过隧道效应注入到浮置栅。 擦除时,将栅极接地,源极悬空、在漏极上加擦除时,将栅极接地,源极悬空、在漏极上加20V的高压的高压脉冲,使浮置栅上的自由电子通过隧道返回到衬底。脉冲,使浮置栅上的自由电子通过隧道返回到衬底。 根据向浮栅注入电子的方式不同,浮栅根据向浮栅注入电子的方式不同,浮栅编程分编程分雪雪崩注入崩注入和和隧道效应注入隧道效应注入两种。两种。1.1.只读存储器只读存储器ROM(1 1)ROM组成组成A A0 0A A1 1A An-1n-1W W0 0W W1 1W Wn-1n-1D D1 1D D0 0D Dn-1n-1存储输出

52、存储输出读出电路读出电路存储矩阵存储矩阵 NM位线位线(数据线)(数据线)(选择线)(选择线)字线字线地址译码器地址译码器存储矩阵存储矩阵地址译码器地址译码器读出电路读出电路 二极管二极管ROM的电路结构的电路结构D7D6D5D4D3D2D1D0+U1A1A01ENENENENENENENEND7D6D5D4D3D2D1D0ENW3W2W1W0地址译码器地址译码器存储矩阵存储矩阵缓冲器缓冲器(2) 分类分类根据构成存储矩阵的元件分为:根据构成存储矩阵的元件分为:以下以二极管型为例介绍工作原理。以下以二极管型为例介绍工作原理。二极管型二极管型W0W1W2W3D3D2D1D0W0W1W2W3D0D

53、3D2D1W0W1W2W3D3D2D1D0三极管型三极管型MOS 型型(3 3) ROM的工作原理的工作原理1)“与与”、“或或” 逻辑阵列逻辑阵列W0W1W2W3RD3位线与字线为位线与字线为 “或或”逻辑关逻辑关系系字线与地址输入字线与地址输入间为间为“与与”逻辑关系逻辑关系D3D2D1D0地址译码器地址译码器“与与”阵列阵列存储矩阵存储矩阵“或或” 阵阵列列+U11W0W1W3W2A0A1A0A1+UW3R D3 D2 D1 D0 +5V R R R R OE A0 A1 A1 A0 Y0 Y1 Y2 Y3 2 线线- -4 线线 译码器译码器 字线与位线的交点都是一个字线与位线的交点都

54、是一个存储单元。交点处有二极管存储单元。交点处有二极管相当存相当存1 1,无二极管相当存,无二极管相当存0 0当当OE=1时输出为高阻状态时输出为高阻状态000101111101111010001101地地 址址A1A0D3D2D1D0内内 容容当当OE=0时时2)数据写入)数据写入简化框图简化框图符号含义符号含义 交叉处的交叉处的“”表示第表示第i根字线与第根字线与第j根位线间有二极管。根位线间有二极管。当某字线被选中时,有点则读出当某字线被选中时,有点则读出“1”,无点处读出,无点处读出“0”。3)存储矩阵的表示)存储矩阵的表示 ROM一般用专门的装置写入数据,数据一旦写入,一般用专门的装

55、置写入数据,数据一旦写入,不能随便改写,在切断电源后,数据也不会消失,即具有不能随便改写,在切断电源后,数据也不会消失,即具有非易失性。非易失性。A0A1W0W1W3W2D3D2D1D0最小项译码器2. 2. 随机存取存储器随机存取存储器(1)RAM的结构的结构A A0 0A A1 1A An-1n-1W W0 0W W1 1W Wn-1n-1数据线数据线I/OI/O控制电路控制电路存储矩阵存储矩阵 NM(选择线)(选择线)字线字线地址译码器地址译码器读读/ /写控制(写控制(R/WR/W)片选(片选(CSCS)I/OI/O输入输入/ /输出输出地址译码器、地址译码器、输入输入/输出控制电路输

56、出控制电路 由结构框图可以看出,存储器有由结构框图可以看出,存储器有3类信号类信号线,线,存储矩阵、存储矩阵、3部分组成,部分组成,存储器由存储器由即即地址线地址线A、数据线数据线D和和控制线控制线C。(2)RAM存储单元存储单元 1)静态)静态RAM存储单元存储单元 存储单元是存储器的最基本存储细胞,存储单元是存储器的最基本存储细胞,RAM的存储单的存储单元与元与ROM的有很大区别,的有很大区别,RAM的存储单元必须是具有记的存储单元必须是具有记忆功能的电路,每个存储单元可存放忆功能的电路,每个存储单元可存放1位二值数据(位二值数据(“1”或或“0”)。按其工作原理不同分有静态)。按其工作原

57、理不同分有静态RAM和动态和动态RAM。 静态静态RAM的数据由触发器记忆,只要不断电,数据的数据由触发器记忆,只要不断电,数据就能永久保存;就能永久保存; 2)动态)动态RAM存储单元存储单元 动态动态RAM存储数据是基于电容器的电荷存储效应实现的,存储数据是基于电容器的电荷存储效应实现的,由于漏电电流的存在,电容上存储的数据(电荷)不能永久由于漏电电流的存在,电容上存储的数据(电荷)不能永久保存,因此必须定期给电容补充电荷,即所谓的保存,因此必须定期给电容补充电荷,即所谓的刷新刷新。常见。常见的动态的动态RAM存储单元有三管和单管两种,其中单管单元为:存储单元有三管和单管两种,其中单管单元

58、为: T 存储单元存储单元写操作写操作:X=1 =0WET导通,电容器导通,电容器C与位线与位线B连通连通 输入缓冲器被选输入缓冲器被选通,数据通,数据DI经缓冲经缓冲器和位线写入存器和位线写入存储单元储单元 如果如果DI为为1,则向,则向电容器充电,电容器充电,C存存1;反之电容器放反之电容器放电电,C存存0 。 - 刷新刷新R行选线行选线XOD读读/写写WEID输出缓冲器输出缓冲器/灵敏放大器灵敏放大器刷新缓冲器刷新缓冲器输入缓冲器输入缓冲器位位线线B读操作读操作:X=1 =1WET导通,电容器导通,电容器C与位线与位线B连通连通 输出缓冲器输出缓冲器/灵敏放大器灵敏放大器被选通,被选通,

59、C中存储的数据中存储的数据通过位线和缓冲器输出通过位线和缓冲器输出 T / 刷新刷新R行选线行选线XODWEID输出缓冲器输出缓冲器/灵敏放大器灵敏放大器刷新缓冲器刷新缓冲器输入缓冲器输入缓冲器位位线线B每次读出后,必须及时每次读出后,必须及时对读出单元刷新,即此对读出单元刷新,即此时刷新控制时刷新控制R也为高电平,也为高电平,则读出的数据又经刷新则读出的数据又经刷新缓冲器和位线对电容器缓冲器和位线对电容器C进行刷新。进行刷新。 当字、位有效时,控制管当字、位有效时,控制管T1、T3导通,此时,当导通,此时,当T2导通,导通,则读位线呈低电平,读则读位线呈低电平,读“0”;当;当T2截止,则读

60、位线呈高电截止,则读位线呈高电平,读平,读“1”。 T2是否能导通,取决于是否能导通,取决于C上是否有电荷。上是否有电荷。有则导通,无则截止有则导通,无则截止。写数据写数据写位线呈高电平,给电容充电,即写写位线呈高电平,给电容充电,即写“0”;读数据读数据当当C上上有(充足)电荷时写有(充足)电荷时写“0”,无电荷时写,无电荷时写“1”。T1T2T3C读读位位 线线写写位位 线线字字选择选择 线线 T2导通的条件导通的条件写位线呈低电平,电容放电,即写写位线呈低电平,电容放电,即写“1”。3.3.存储器容量及扩展存储器容量及扩展(2 2)容量)容量字字用于表示数据和指令的二进制数,称为字。用于

61、表示数据和指令的二进制数,称为字。字长字长 一个字的位数,叫字长。一个字的位数,叫字长。字数字数字的个数,叫字数。字的个数,叫字数。字节字节8 8位二进制数据的字长为一个字节。位二进制数据的字长为一个字节。 存储器容量常以字数和字长的乘积表示,其存储器容量常以字数和字长的乘积表示,其计量单位为计量单位为k k、M、G G。 字长是衡量数字系统精度的重要指标,存储器中以字字长是衡量数字系统精度的重要指标,存储器中以字为单位进行存储,即利用一组存储单元存储一个字。为单位进行存储,即利用一组存储单元存储一个字。 10241024个字数,简称个字数,简称1 1k k。1k=21k=21010=1024

62、 1=1024 1M=2=22020=1024k=1024k,1G=21G=23030=1024=1024M。(1 1)有关术语)有关术语(3 3)RAMRAM存储容量的扩展存储容量的扩展1)位扩展)位扩展 通常通常RAM芯片的字长有芯片的字长有1位、位、 4位位、8位、位、16位和位和32位等。当实际的存位等。当实际的存储系统的字长超过芯片的字长时,则需对储系统的字长超过芯片的字长时,则需对RAM芯片实行位扩展。芯片实行位扩展。2)字扩展)字扩展D0D1D2D3D4D5D6D7译译器器码码A7A0CEI/O2564A7A0CEI/O2564A7A0CEI/O2564A7A0CEI/O2564A7A0CEI/O2564A7A0CEI/O2564A7A0CEI/O2564A7A0CEI/O2564A0A7片选控制器

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。