集成电路课程设计指导书

集成电路课程设计指导书

《集成电路课程设计指导书》由会员分享,可在线阅读,更多相关《集成电路课程设计指导书(15页珍藏版)》请在装配图网上搜索。

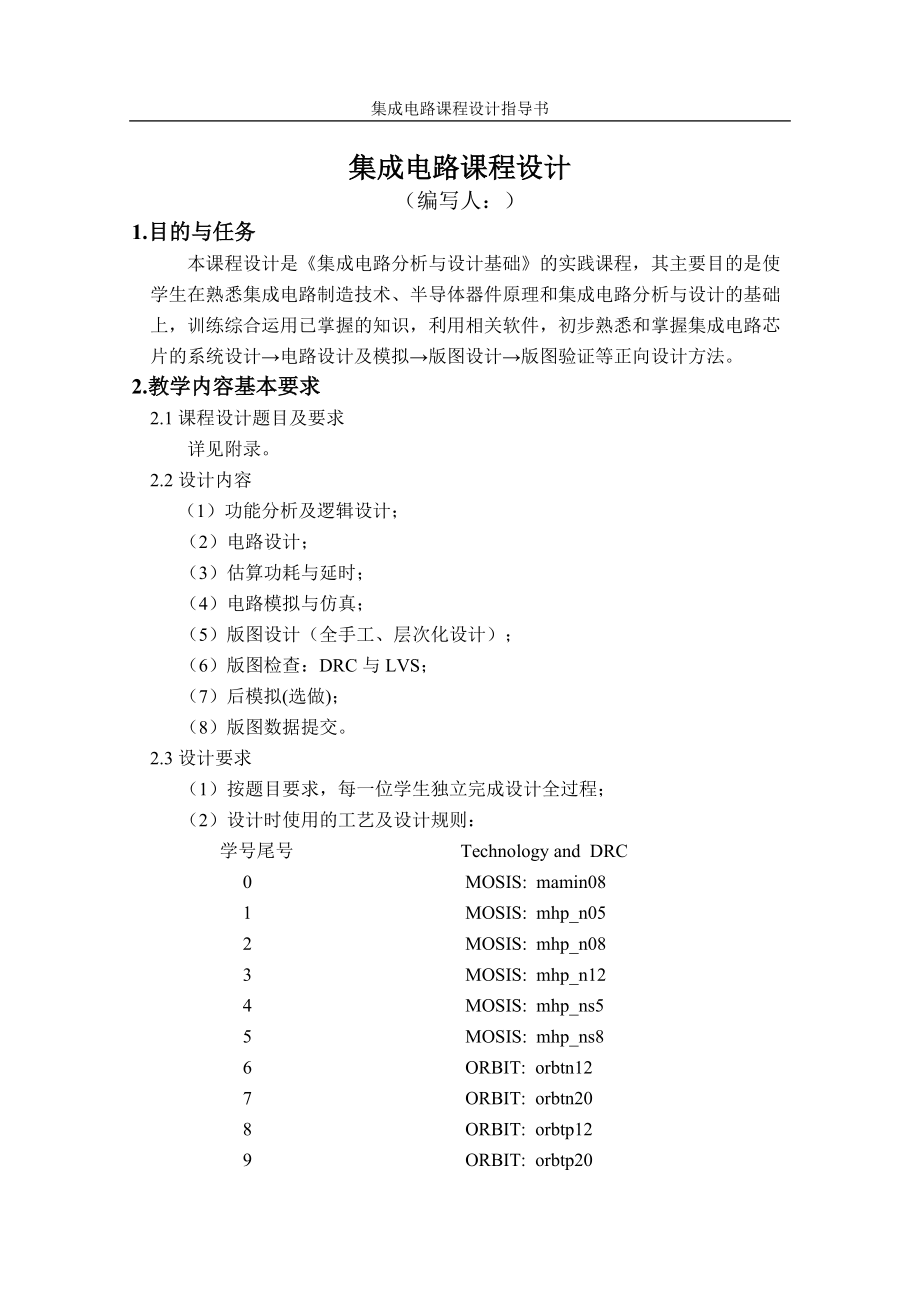

1、集成电路课程设计指导书集成电路课程设计(编写人:)1.目的与任务本课程设计是集成电路分析与设计基础的实践课程,其主要目的是使学生在熟悉集成电路制造技术、半导体器件原理和集成电路分析与设计的基础上,训练综合运用已掌握的知识,利用相关软件,初步熟悉和掌握集成电路芯片的系统设计电路设计及模拟版图设计版图验证等正向设计方法。2.教学内容基本要求2.1课程设计题目及要求详见附录。2.2设计内容(1)功能分析及逻辑设计;(2)电路设计;(3)估算功耗与延时;(4)电路模拟与仿真;(5)版图设计(全手工、层次化设计);(6)版图检查:DRC与LVS;(7)后模拟(选做);(8)版图数据提交。2.3设计要求(

2、1)按题目要求,每一位学生独立完成设计全过程;(2)设计时使用的工艺及设计规则: 学号尾号 Technology and DRC0 MOSIS: mamin08 1 MOSIS: mhp_n05 2 MOSIS: mhp_n08 3 MOSIS: mhp_n12 4 MOSIS: mhp_ns5 5 MOSIS: mhp_ns8 6 ORBIT: orbtn12 7 ORBIT: orbtn20 8 ORBIT: orbtp12 9 ORBIT: orbtp20 (3)根据所规定的工艺及设计规则,选取合理的模型库,也可自己建立合理的模型,使用其参数进行相关计算;(4)选用以(lambda)为单

3、位的设计规则。3.主要教学环节3.1设计安排(1)课程设计时间为两周;(2)第1天上午讲授设计的要求、布置设计题目;(3)第1天完成功能分析及逻辑设计;(4)第3天完成电路设计;(5)第4天完成功耗与延时估算;(6)第5天完成电路模拟与仿真;(7)第8天完成版图设计及检查(8)第910天完成设计报告,答辩。注:各人可根据自己的完成情况,灵活掌握,并尽可能提前完成。3.2指导与答疑现场有教师答疑,学生有疑难问题可找教师答疑。教师一般只提供指导性意见,学生应充分发挥主观能动性,提高分析问题和解决问题的能力。3.3设计的考评教师根据学生设计全过程的完成情况、答辩成绩和课程设计报告书综合评出该课程设计

4、成绩。4.课程设计报告的内容和要求(1) 课程设计报告的内容必须包括上述设计内容的每一项,每一项要有设计思路分析,合理性分析;(2) 每一个参数计算要列出计算公式来源,选用原始参数依据;(3) 每一级电路参数计算(主要是W/L)要有相应的电路图;(4) 模拟时要列出源程序,所用模型参数,结果及分析;(5) 版图设计要有单元版图和总体布置版图;(6) 总结这次课程设计的经验和体会;(7) 每人提交一份报告书;(8) 提交电子版所有设计内容:电路图、模拟结果、版图、设计报告书。附录:设计题目及设计方法简介1.设计题目1.1器件名称:(1) 38线译码器的74HC138芯片(学号尾号为双数的同学);

5、(2) 含两个24译码器的74HC139芯片(学号尾号为单数的同学);(3) 或自选复杂程度与此相当的其他芯片,但需指导教师同意。1.2要求的电路性能指标:(1) 可驱动10个LSTTL电路(相当于15pF电容负载);(2) 输出高电平时,|IOH|20A,VOH,min=4.4V;(3) 输出底电平时,|IOL|4mA,VOL,man=0.4V;(4) 输出级充放电时间tr=tf,tpd25ns;(5) 工作电源5V,常温工作,工作频率fwork=30MHz,总功耗Pmax150mW。2.设计方法简介(以74HC139为例)2.174HC139芯片简介74HC139是包含两个2线 4线译码器

6、的高速CMOS数字电路集成芯片,能与TTL集成电路芯片兼容,它的管脚图如图1所示,其逻辑真值表如表1所示。图1 74HC139的管脚图表1 74HC139真值表片选输入数据输出CsA1A0Y0Y1Y2Y30000111001101010110101111101111174HC139的逻辑表达式:,74HC139的逻辑图如图2所示:图2 74HC139的逻辑图2.2电路设计2.2.1输出级电路设计据要求,输出级等效电路如图3所示。输入Vi为前一级的输出,可认为是理想的输出,即ViLVss,ViH=VDD。图3 输出级等效电路(1) 输出级 N管(W/L)N的计算当输入为高电平时,输出为低电平,N

7、管导通,后级TTL有较大的灌电流输入,要求|IOL|4mA,VOL,man=0.4V,依据NMOS管的理想电流方程分段表达式:或依据NMOS管的理想电流方程统一表达式:求出(W/L)N,min极限值,往大值取整数,以为单位表示(下同)。特别提示:计算过程中,要统一各参数的单位。(2)输出级 P管(W/L)P的计算当输入为低电平时,输出为高电平,P管导通。同时要求N管和P管的充放电时间tr=tf,分别求出这两个条件下的(W/L)P,min极限值,然后取大者。 以|IOH|20A,VOH,min=4.4V为条件计算(W/L)P,min极限值:用PMOS管的理想电流方程分段表达式:或依据PMOS管的

8、理想电流方程统一表达式:求(W/L)P,min极限值。 N管和P管的充放电时间tr和tf表达式分别为: 以tr=tf为条件计算(W/L)P,min极限值。比较和中(W/L)P,min值,取大值者作为输出级的(W/L)P值。2.2.2内部基本反相器中的各MOS尺寸的计算内部基本反相器如图4所示,它的N管和P管尺寸依据充放电时间tr和tf方程来求。关键点是先求出式中CL(即负载)。图4 内部反相器它的负载由以下三部分电容组成:本级漏极的PN结电容CPN;下级的栅电容Cg;连线杂散电容CS。 本级漏极PN结电容CPN计算CPNCj(Wb)+Cjsw(2W+2b)其中Cj是每um2的结电容,Cjsw是

9、每um的周界电容,b为有源区宽度,可从设计规则获取。如若最小孔为22,孔与多晶硅栅的最小间距为2,孔与有源区边界的最小间距为2,则取b6。Cj和Cjsw可用相关公式计算,或从模型库选取,或用经验数据。总的漏极PN结电容应是N管和P管的总和,即:CPN(Cj,NWNCj,PWP)bCjsw,N(2WN2b)Cjsw,P(2WP2b)注:此处WN 和WP为未知数。 栅电容Cg计算CgCg,NCg,P(WNWP)L此处WN和WP为与本级漏极相连的下一级N管和P管的栅极尺寸,近似取输出级的WN和WP值。连线杂散电容CSCS一般CPNCg10CS,可忽略CS作用。因此,内部基本反相器的总负载电容CL为上

10、述各电容计算值之和。把CL代入tr和tf的方程式,并根据tr=tf25ns的条件,计算出WN和WP,得:2.2.3内部逻辑门MOS尺寸的计算内部逻辑门的电路如图5所示。根据截止延迟时间tpLH和导通延迟时间tpHL的要求,在最坏情况下,必须保证等效N管、P管的等效电阻与内部基本反相器的相同,这样三输入与非门就相当于内部基本反相器了。因此,N管的尺寸放大3倍,而P管尺寸不变,即:图5 内部逻辑门的电路2.2.4输入级设计由于本电路是与TTL兼容,TTL的输入电平ViH可能为2.4V,如果按正常内部反相器进行设计,则N1、P1构成的CMOS将有较大直流功耗。故采用如图6所示的电路,通过正反馈的P2

11、作为上提拉管,使ViH较快上升,减小功耗,加快翻转速度。图6 输入级电路(1)输入级提拉管P2的(W/L)P2计算为了节省面积,同时又能使ViH较快上升,取(W/L)P21。若取L=2,W=2,要特别注意版图的画法,不要违反设计几何规则。为了方便画版图,此处的L允许取6。(2)输入级P1管(W/L)P1的计算此P1管应取内部基本反相器的尺寸(即本小节2中计算出的内部基本反相器中P管的(W/L)P,内部反相器尺寸)。(3)输入级N1管(W/L)N1的计算由于要与TTL电路兼容,而TTL的输出电平在0.42.4V之间,因此要选取反相器的状态转变电平:又知:式中,从中可求出CMOS 反相器N1管(W

12、/L)N1值。2.2.5缓冲级的设计(1)输入缓冲级由74HC139的逻辑图可知,在输入级中有三个信号:Cs、A1、A0。其中Cs经一级输入反相器后,形成,用去驱动4个三输入与非门,故需要缓冲级,使其驱动能力增加。同时为了用驱动,必须加入缓冲门。由于A1、A0以及各驱动内部与非门2个,所以可以不用缓冲级。Cs的缓冲级设计过程如下:Cs的缓冲级与输入级和内部门的关系如图7所示。图中M1为输入级,M2为内部门,M3为缓冲级驱动门。M1的P管和N管的尺寸即为上述所述的图7 Cs的缓冲级输入级CMOS反相器P1管和 N1管尺寸,M2的P管和N管的尺寸即为内部基本反相器P1管和 N1管尺寸,M3的P管和

13、N管的尺寸由级间比值(相邻级中MOS管宽度增加的倍数)来确定。如果要求尺寸或功耗最佳,级间比值为210。具体可取。N为扇出系数,它的定义是:在本例中,前级等效反相器栅的面积为M2的P管和N管的栅面积总和,下级栅的面积为4个三输入与非门中与Cs相连的所有P管和N管的栅面积总和。从中得出M3管尺寸为:(2)输出缓冲级由于输出级部分要驱动TTL电路,其尺寸较大,因而必须在与非门输出与输出级之间加入一级缓冲门M1,如图8所示。将与非门M0等效为一个反相器,类似上述Cs的缓冲级设计,计算出M1的P管和N管的尺寸。图8 输出缓冲级2.2.6输入保护电路设计因为MOS器件的栅极有极高的绝缘电阻,当栅极处于浮

14、置状态时,由于某种原因(如触摸),感应的电荷无法很快地泄放掉。而MOS器件的栅氧化层极薄,这些感应的电荷使得MOS器件的栅与衬底之间产生非常高的电场。该电场强度如果超过栅氧化层的击穿极限,则将发生栅击穿,使MOS器件失效,因此要设置保护电路。输入保护电路有单二极管、电阻结构和双二极管、电阻结构。图9所示的为双二极管、电阻结构输入保护电路。保护电路中的电阻可以是扩散电阻、多晶硅电阻或其他合金薄膜电阻,其典型值为300500。二极管的有效面积可取500m2,或用Shockley方程计算。输入保护电路的版图可按相关的版图设计要求自己设计,也可调用单元库中的pad单元版图。如果版图设计中准备调用单元库

15、中的pad标准单元版图,因其包含保持电路,就不必别外的保护电路设计。图9 输入保护电路至此,完成了全部器件的参数计算,汇总列出各级N管和P管的尺寸。2.3功耗与延迟估算在估算延时、功耗时,从输入到输出选出一条级数最多的去路进行估算。在74HC139电路从输入到输出的所有各支路中,只有Cs端加入了缓冲级,其级数最多,延时与功耗最大,因此在估算74HC139芯片的延时、功耗时,就以Cs支路电路图(如图10所示)来简化估算。图10 估算延时、功耗Cs支路电路2.3.1模型简化由于在实际工作中,四个三输入与非门中只有一个可被选通并工作,而另三个不工作,所以估算功耗时只估算上图所示的支路即可。在Cs端经

16、三级反相器后,与四个三输入与非门相连,但图10所示的支路与另外不工作的三个三输入与非门断开了,所以用负载电容CL1来等效与另外三个不工作的三输入与非门电路,而将工作的一个三输入与非门的两个输入接高电平,只将Cs端信号加在反相器上。在X点之前的电路,由于A0,A1,Cs均为输入级,虽然A0、A1比Cs少一个反相器,作为工程估算,可以认为三个输入级是相同的,于是,估算功耗时对X点这前的部分只要计算Cs这一个支路,最后将结果乘以3倍就可以了。在X点之后的电路功耗,则只计算一个支路。2.3.2功耗估算CMOS电路的功耗中一般包括静态功耗、瞬态功耗、交变功耗。由于CMOS电路忽略漏电,静态功耗近似为0,

17、工作频率不高时,也可忽略交变功耗,则估算时只计算瞬态功耗PT即可。按下列公式计算瞬态功耗。PT=CL总Vdd2fmax其中:CPN为本级漏极PN结电容,按2.2.2相关公式计算Cg为与本级漏极相连的下一级栅电容,按2.2.2的Cg计算CS为从本级漏连接到下一级栅的连线杂散电容,其值较小,可忽略不计CL1为被断开的三个三输入与非门栅电容,按2.2.2的Cg计算CL为最后一级(即输出级)的下一级栅电容,即负载电容15pFX前、X后表示Cs支路电路中X点之前或X点之后的所有器件对于74HC138器件,整个芯片功耗为2PT。估算出的功耗与设计指标比较,若满足要求,进行下一步工作;若不满足要求,修改设计

18、,直到满足设计指标为止。2.3.3延迟估算算出每一级等效反相器延迟时间,总的延迟时间为各级(共6级)延迟时间的总和。各级等效反相器延迟时间可用下式估算:各字母代表的意义如图11所示。汇总列出每一级器件延迟时间,最后得出总的延迟时间。估算出的总延迟值时间与设计指标比较,若满足要求,进行下一步工作;若不满足要求,修改设计,直到满足设计指标为止。ttVoViVddVdd0.90.50.10t ftpLHtpHLt r0.5图11 延迟时间,上升与下降时间2.4电路模拟电路模拟中为了减小工作量,使用上述功耗与延迟估算部分用过的Cs支路电路图。为了计算出功耗,在两个电源支路分别加入一个零值电压源VI1和

19、VI2,电压值为零(如图12所示),在模拟时进行直流扫描分析,然后就可得出功耗。图12 电路模拟用Cs支路电路把此电路图转化为SPICE文件,加入电路特性分析指令和控制语句。2.4.1直流分析当VCS由0.4V变化到2.4V过程中,观察波形得到阈值电压(状态转变电平)VI。VI的值应为1.4V。2.4.2瞬态分析从波形中得到tpLH、tpHL、tr和tf,然后进行相关计算。2.4.3功耗分析对电压源VI1和VI2进行直流扫描分析:“.dc lin source vI1 0 5 0.1 sweep lin source vI2 0 5 0.1 ”,输出“.print dc p( VI1) p(V

20、I2)”,从波形中得出p( VI1 )max和 p(VI2)max,总功耗:Ptotal23p( VI1 )max p(VI2)max模拟分析得到的结果与设计指标比较。若满足要求,进行下一步工作;若不满足要求,修改相关参数,直到满足设计指标为止。参数修改后,不必对原来前面的计算重新再一次计算。只要依据模拟结果,说明修改相关参数的理由即可。特别提示:模拟结果务必全部达到设计指标后再进行下一步的版图设计,否则,所设计的版图将前功尽弃。2.5版图设计层次化、全手工设计版图。所谓层次化设计版图,就是先设计单元版图,由简单的单元版图再组成较复杂的单元版图,一层层设计,直致完成芯片的整体版图。按版图设计的

21、注意事项进行布图和布线,还要注意散热的均匀性和热量容易散发。2.6版图检查2.6.1版图设计规则检查(DRC)做DRC检查时应该分成小块(单元)检查。每一部分做成一个单元,每个单元进行DRC检查。在全部通过后,将单元组合成电路,最终做一次全版图的DRC,以确保全版图正确。2.6.2电路网表匹配(LVS)检查电路图提取的网表文件(.sp)与版图提取的网表文件(.spc),进行元件和节点的匹配检查。如果匹配,表明版图的连接及版图中各管子的生成是正确的。因此,只要保证电路图是正确的,LVS检查就可以验证版图的正确性。2.6.3后模拟(选做)从版图提取SPICE网表文件(.spc),加载电路特性分析指令和控制语句,进行模拟。然后对结果进行相关分析,查验是否达到设计指标要求。2.6.4版图数据的提交所设计的版图通过DRC和LVS的检查,以及ERC检查(本次设计不做),然后转换成制造掩膜用的码流数据,用GDS-II格式。

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。