《集成电路课程设计》大作业报告 一个9bit循环式两步ADC的设计与实现

《集成电路课程设计》大作业报告 一个9bit循环式两步ADC的设计与实现

《《集成电路课程设计》大作业报告 一个9bit循环式两步ADC的设计与实现》由会员分享,可在线阅读,更多相关《《集成电路课程设计》大作业报告 一个9bit循环式两步ADC的设计与实现(14页珍藏版)》请在装配图网上搜索。

1、一个9bit循环式两步ADC的设计与实现 摘要:设计了一个9bit循环式两步AD转换器。整个电路完全采用全定制方法进行设计,对于电路每一个模块按照模拟电路的设计方法进行设计仿真。整体电路仿真性能较好,且通过了版图DRC,LVS验证。对版图进行参数提取(LPE)进行后仿也取得了很好的测试性能。后仿测试的ADC输出信号无杂散动态范围(SFDR)达到了60dB以上。关键词:循环式两步ADC注:本实验报告包括设计原理,电路设计,版图设计,后仿真以及设计结论等部分组成,由本小组成员共同书写完成。为了便于统筹阅览,将部分报告内容单独写成一个文档,并在本文中以链接的方式指向它。下文中凡是有链接的地方均以下划

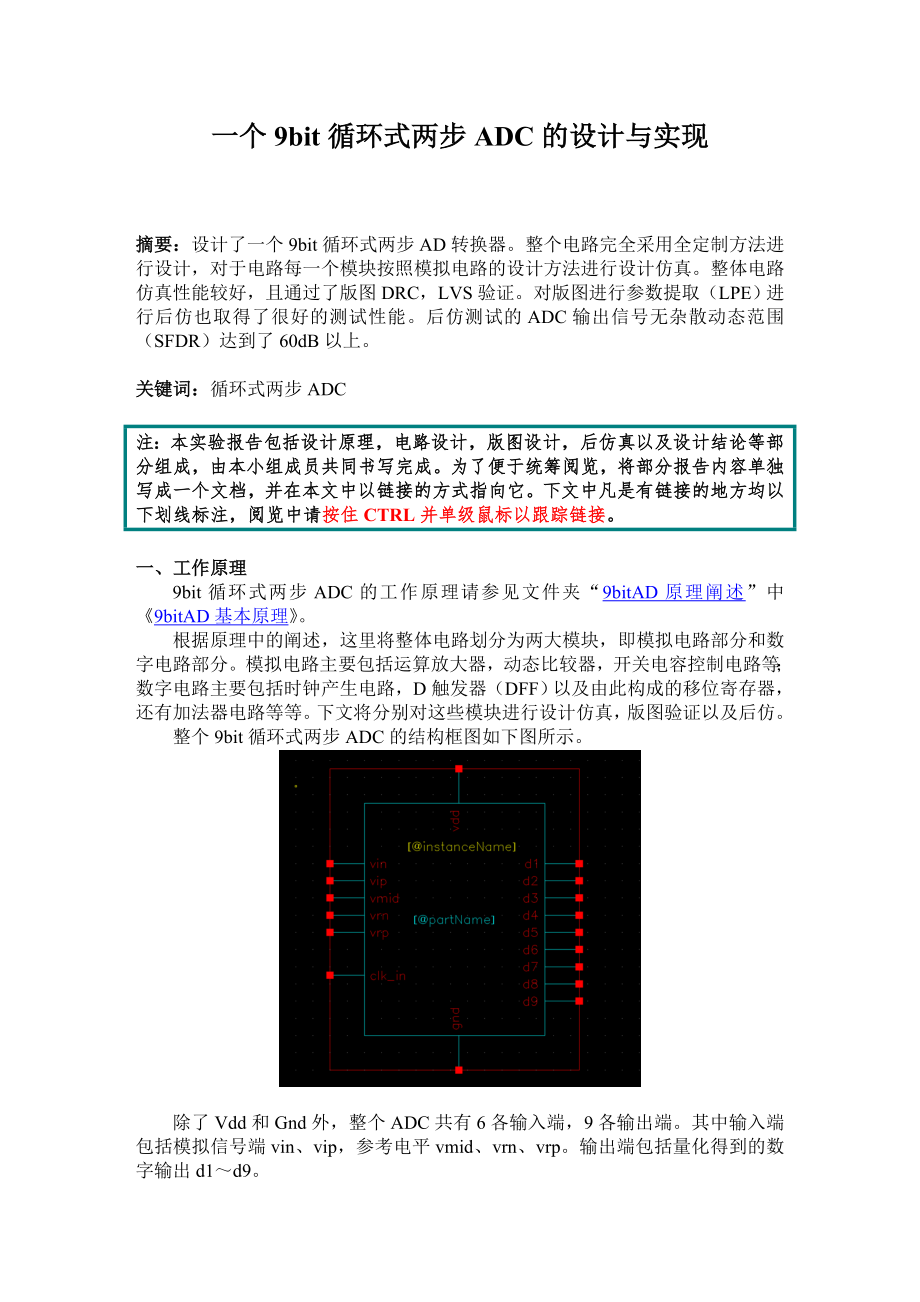

2、线标注,阅览中请按住CTRL并单级鼠标以跟踪链接。一、工作原理9bit循环式两步ADC的工作原理请参见文件夹“9bitAD原理阐述”中9bitAD基本原理。根据原理中的阐述,这里将整体电路划分为两大模块,即模拟电路部分和数字电路部分。模拟电路主要包括运算放大器,动态比较器,开关电容控制电路等;数字电路主要包括时钟产生电路,D触发器(DFF)以及由此构成的移位寄存器,还有加法器电路等等。下文将分别对这些模块进行设计仿真,版图验证以及后仿。整个9bit循环式两步ADC的结构框图如下图所示。除了Vdd和Gnd外,整个ADC共有6各输入端,9各输出端。其中输入端包括模拟信号端vin、vip,参考电平v

3、mid、vrn、vrp。输出端包括量化得到的数字输出d1d9。将上图展开得到如下的模块框图。 图中clk部分为时钟产生电路部分,part1为模拟电路部分,part2为数字电路部分。值得注意的是,由于动态比较器的输入是模拟信号,输出被认为是数字信号,在设计中将动态比较器所在的开关控制信号产生部分纳入模拟电路中。二、电路设计本部分包括整体电路、重要的单元电路的电路原理设计,前仿,版图设计,以及后仿的结果,但不包括整体电路的后仿结果。我们的设计思路是,将每一个单元(例如OTA)在Layout尺寸的限制下按照完整的设计流程进行设计,即进行前仿,版图设计,DRC/LVS验证和LPE后仿,以形成可重复利用

4、的通用模块。最后只需将各个单元模块实现互连,这样做思路清晰且容易查错修改。1 重要单元电路设计1.1 运算放大器设计了一种单级Cascode运算放大器,它具有增益较高,输出电压摆幅较大且运算速度较快的特点。有关运算放大器的详细内容参见文件夹“OTA报告”中的运算放大器。该报告包括以下主要内容:电路原理(原理概述,性能估计),前仿测试(包括功能验证,工艺角仿真验证,温度域仿真验证等),版图设计(布局考虑,DRC/LVS结果),版图参数提取与后仿真结果,前后仿真结果对比等。运算放大器在设计中的宏模型符号如下图所示。1.2 动态比较器有关动态比较器的详细内容请参见文件夹“比较器报告”中的compar

5、ator。文中设计了一种动态比较器,并完成了前仿,版图设计以及后仿的设计流程。报告中包括如下内容:电路工作原理,性能参数仿真(速度,功耗,回程干扰,失调等),版图设计,后仿以及前后仿结果对比。由动态比较器组成的开关信号产生电路在本设计中被认为是模拟电路,它和运算放大器、开关电容阵列一起构成循环式ADC信号转换的核心部分。1.3 数字处理部分中的基本单元电路在时钟产生电路、移位寄存器等数字处理模块中将广泛使用反相器、与非门、DFF等逻辑单元。将这些单元设计成为通用模块,以便在设计中重复利用。这里将这些单元的设计内容写入报告基本单元电路中,详见文件夹“基本单元电路报告”。报告中包括了DFF,移位寄

6、存器阵列,反相器以及与非门的设计。其中主要讨论了DFF的设计,包括如下内容:电路原理,性能仿真,参数估计,时钟馈通效应,版图设计等。1.4 时钟产生电路设计了一种产生两相不交叠时钟的电路,并完成了前仿,版图设计以及后仿等设计流程。详细内容请参见文件夹“时钟产生电路报告”中的时钟产生电路。该部分包括以下主要内容:电路原理,主要性能参数估计,前仿,版图设计,参数提取与后仿,前后仿真对比等。时钟产生电路在设计中的宏模型表示符号如下图所示。 时钟产生电路除了Vdd和Gnd端外,输入端为时钟信号clk_in,输出端包括f1,f2,k1,k2,nf1,nf2,nk1,nk2,s1,s2,ns1,ns2。1

7、.5 加法器加法器主要将移位寄存器的输出结果(8位)相加,即构成一个9bit加法器。为了便于模块化设计,这里设计了一个一位全加器,然后由这些一位全加器构成9bit异步加法器。全加器的设计报告详见“加法器报告”中的adder。主要内容包括:电路原理、性能仿真、版图设计、后仿等。加法器在设计中的宏模型单元如下图。一位全加器除了Vdd和Gnd外,输入端包括A,B,Ci(进位输入端),输出端包括S(和),Co(进位输出端)。9bit全加器由9个一位全加器构成,其电路原理图如下。9bit全加器电路宏模型符号如下图所示。输入端包括l1l9、m1m8,输出端包括d1d9。2 整体电路设计在前面的电路原理中已

8、经详细介绍了9bit循环式ADC的电路工作原理,整体电路如第2页图所示。电路中不仅包括模拟电路部分,也包括数字电路部分。在进行HSPICE仿真时并不区分数据是模拟信号还是数字信号,因此在数字部分中电平5V代表信号“1”,电平0V代表信号“0”。由于采用全定制设计,整体HSPICE仿真速度非常慢,但仿真结果可信度较高。仿真文件参见文件夹“HSPICE仿真文件/整体电路前仿文件”中的sheji_full。仿真测试中设定参数如下:输入模拟信号为70.8KHz的正弦波,其直流电平为2V,交流幅度为1V,即满量程输入。采样输出时间间隔为0.4us,一共采样输出信号1024个点(每个点为一个9bit数据)

9、,以便于进行DFT频谱分析。文件,显示了仿真相关信息。为便于直观验证,将输出的9位数字信号按照如下公式计算,得到的应当是正弦采样信号。dout = d1*256+d2*128+d3*64+d4*32+d8*2+d9仿真结果如下页图所示,这里仅绘制了一个半周期的输出dout。可以看出,输出信号也是正弦信号,这说明该设计能够正常工作。仿真结果还显示,输出信号在转换时有很多毛刺,这是由于数字电路中的竞争冒险造成的。只要合理设置采样点的时刻,这些毛刺并不影响输出结果。将输出数据导入matlab中进行谱分析,m文件为文件夹“MATLAB测试文件”中的full_out。对full_out.m文件仿真,得到

10、如下的仿真结果。下图是输出信号dout的采样曲线。对上图进行局部放大,可以清晰地观察其正弦特性。对输出采样点作离散傅立叶分析,得到下面的频谱曲线。图中纵坐标是归一化后的数值。根据编写的m文件可以测试出输出信号的无杂散动态范围SFDRdB,输出信噪比为SNRdB。三、版图设计本设计是一个混合信号处理器件,它即包含模拟电路部分,由包含数字电路部分。为了使器件工作稳定,减少不同电路之间的串扰,在版图规划中应尽量将模拟部分和数字部分分离。本设计总体规划芯片面积为1mm1mm的方形区域,其中上半部分为模拟电路,下半部分为数字电路。如下图所示。模拟部分的电源和地分别接AVDD和AGND;数字部分的电源和地

11、分别接DVDD和DGND。在本次设计中,为了便于对电路进行LVS验证和LPE参数提取,先将所有电源接成VDD,地接成GND,即整个电路共享一套电源和地。当LVS和LPE后仿通过后,再将两部分的电源和地分开,并在版图上加上输入、输出pad,完成整个芯片的设计。详细的Layout布局如下图所示。为了使芯片布局更加紧凑,面积利用更加合理,在实际版图绘制中进行了微调。芯片中的空余部分主要加上了保护环以实现电路模块之间的隔离。9位数字信号输出输入信号实际绘制的版图反色照片如下,这里将其进行了分区域标注,以便于和上图进行对比。在设计完成(通过DRC,LVS以及LPE后仿)后,将模拟部分和数字部分的电源、地

12、分离,并加上pad。最终完成的版图设计照片如下。不带pad的版图gds文件见文件夹“各模块版图设计相关文件/full_withoutpad”中drclvs.gds;带pad的版图gds文件见文件夹“包含pad的版图设计相关文件”中的drclvs.gds。其中前者通过了DRC,LVS,LPE;后者通过了DRC验证。四、后仿真对版图进行LPE参数提取,共提取出1574个MOS管,5个电阻,12个电容以及764个寄生电容。按照前面前仿的方法对提取的电路进行仿真,得到输出数据dout如下页图。这里先列出仿真.lis文件中的相关信息。同样将输出数据导入Matlab中进行频谱分析,得到如下结果。将上图进行

13、局部放大得到如下结果。 对结果进行离散傅立叶变换得到下面的频谱图。编写m文件求得输出信号SFDRdB,信噪比SNRdB。将前仿和后仿的结果列表对比如下。仿真时间输出SFDR输出SNR前仿dBdB后仿dBdB五、结论本次设计完成了较完整的集成电路设计流程,通过一个月来全组成员的努力,我们设计的9bit循环式两步ADC能够正常工作,完成了设计的任务。在设计的过程中,我们的体会主要有以下几点。1我们采取的是全定制设计的方法,尤其对于数字电路,我们也按照模拟电路的方法进行设计,仿真,验证。这种方法最大的好处在于仿真结果更加可靠,而且设计的思路清晰,但其代价是增加了版图绘制的难度,因为数字电路部分MOS

14、管较多;另外,这种方法也直接影响了仿真的速度。本次设计的前仿和后仿时间都在12个小时以上。2模块化的设计思想有利于整体修改、调试。电路中有很多子单元,例如OTA、比较器、DFF等具有很强的功能独立性。我们在设计这些子单元时,也按照完整的流程进行设计,保证每一个模块的电路程序,版图,后仿结果都接近于理想值。因此在最后构架芯片整体结构时,我们只需关心模块间的连线是否正确。3在2的基础上,我们小组5个成员基本上每人负责一个模块的设计,包括从前仿、版图设计到后仿,这样每个人都对整个设计流程比较熟悉,这也方便了电路的整体调试。4后仿的结果显示,对于单音测试,输出SFDR60dB,这个结果好于前仿的结果,

15、一个原因在于后仿舍弃了前面几个不稳定的数据。5在仿真调试的过程中,我们没有一开始便仿真整个电路,仍是按照模块化的思想进行仿真验证的。值得一提的是,电路的模拟部分是全电路的核心,我们在仿真时特别将模拟部分进行仿真,并验证得到的结果。在保证模拟电路部分正常工作之后,我们才加入后面的数字电路进行仿真测试。6整个版图布局紧凑,但由于这是我们初次完成较大规模的版图,里面难免有很多地方值得改进。我们感觉对版图设计的技巧掌握还不够,这些需要在今后的学习中不断积累经验了。7虽然完成了整个设计并取得了良好的仿真性能,但是我们没有使用综合的办法来设计数字部分,缺少了在这方面学习的经验,不得不说是一个遗憾了。希望在

16、以后的学习中能在这方面有所充实。整个设计完成持续了近两个月的时间,其中版图设计与HSPICE仿真占据了大量时间。9衷心感谢李老师和助教老师的指导,帮助我们解决了很多实际困难。附、分工合作情况一、电路设计李淼动态比较器的设计,包括原理图绘制,前仿,后仿;9bit全加器的设计,包括原理图绘制,前仿,后仿。邬建元时钟产生电路的设计,包括原理图绘制,前仿,后仿;移位寄存器的设计,包括原理图绘制,前仿,后仿。章英杰基本逻辑单元的设计,包括DFF,反相器,与非门等,完成了原理图绘制,前仿,后仿;1位全加器的设计,包括原理图绘制,前仿,后仿。徐友春开关电容电路的设计,包括原理图绘制;运算放大器的部分设计,包

17、括原理图绘制,部分仿真。陈润运算放大器的部分设计,包括部分仿真测试;整体电路的模块化构成,全电路的前仿,后仿。二、版图绘制李淼动态比较器版图,以及由此构成的开关控制信号产生电路部分;9bit加法器版图。邬建元由DFF阵列构成的移位寄存器版图;数字电路模块之间的互连。章英杰基本逻辑单元的版图绘制,包括DFF,反相器,与非门等;1位全加器版图。徐友春开关电容电路版图;时钟产生电路版图;模拟电路模块之间的互连。陈润整体电路版图设计布局;运算放大器版图;整体电路的互连,以及加pad处理。三、报告完成李淼比较器报告:comparator;加法器报告:adder。邬建元时钟产生电路报告:时钟产生电路;全电路基本原理报告:9bitAD基本原理部分。章英杰基本单元报告:基本单元电路;全电路基本原理报告:9bitAD基本原理部分。徐友春运放报告:运算放大器前仿部分。陈润运放报告:运算放大器版图设计与后仿部分;总体报告:一个9bit循环式两步ADC的设计与实现;完成了上交报告文件的整理。

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 人教版小学三年级数学认识年月日ppt课件

- 人教版五年级下册数学知识点总结ppt课件

- 人教版数学七下《10.1统计调查》ppt参赛课件

- 人教版七年级语文病句解题技巧ppt课件

- 人教版四年级数学教学重难点ppt课件

- 人教版小学六年级下学期数学《抽屉原理ppt课件》公开课

- 人教版三年级数学下册第一单元复习ppt课件

- 人教版七年级英语上册复习ppt课件

- 人教版七年级下册英语单词填空专练ppt课件

- 安全技术防范管理---第二章风险评估基本知识

- 人教版八年级物理下册杠杆ppt课件

- 人教版九年级化学上元素ppt优秀课件

- 人教版六年级上-诗经采薇ppt课件

- 人教版六年级上册数学《倒数的认识》ppt课件

- 人教版道德与法治一年级下册第8课《大自然谢谢您》ppt课件