模拟集成电路课程设计

模拟集成电路课程设计

《模拟集成电路课程设计》由会员分享,可在线阅读,更多相关《模拟集成电路课程设计(6页珍藏版)》请在装配图网上搜索。

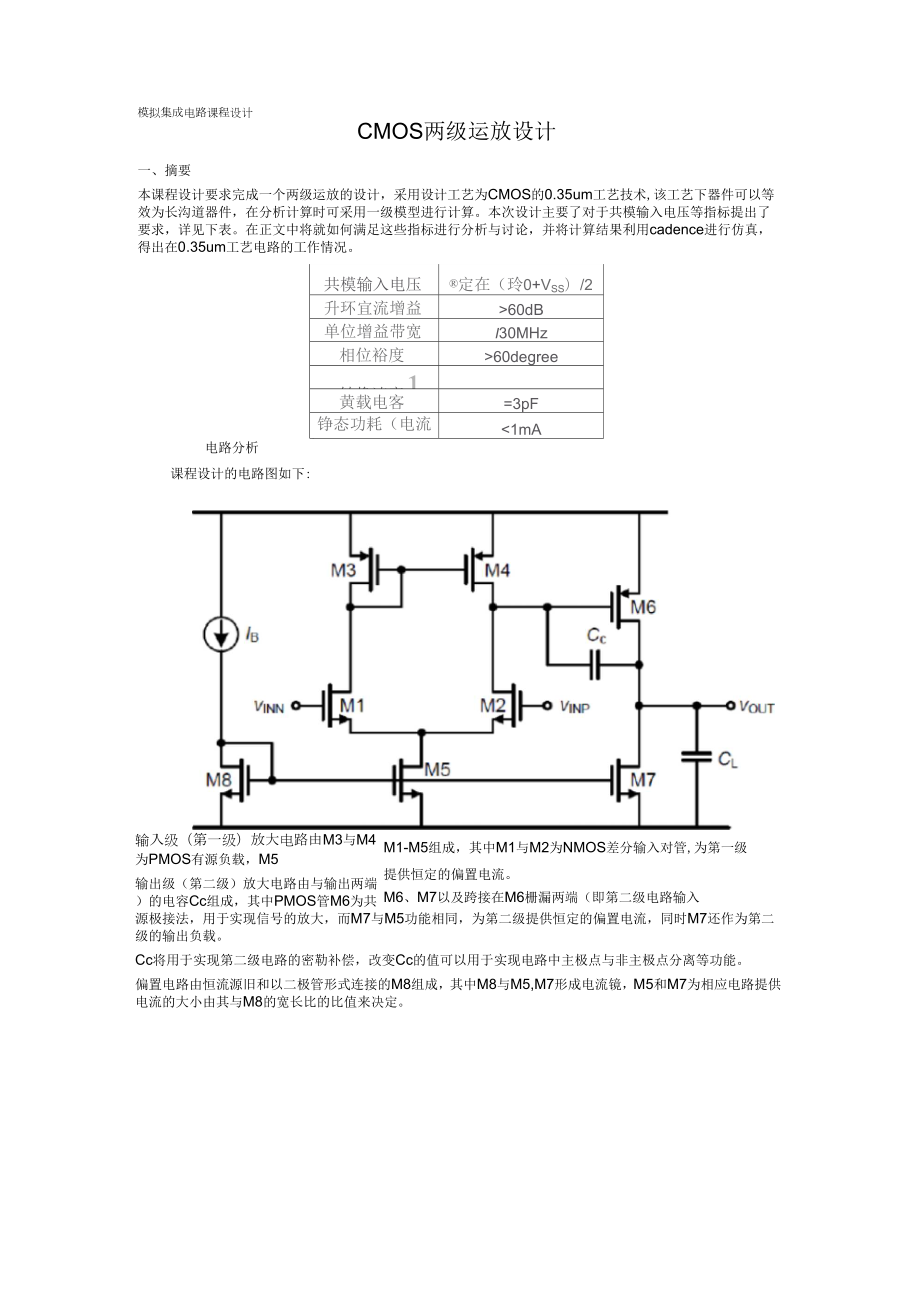

1、模拟集成电路课程设计CMOS两级运放设计一、摘要本课程设计要求完成一个两级运放的设计,采用设计工艺为CMOS的0.35um工艺技术,该工艺下器件可以等效为长沟道器件,在分析计算时可采用一级模型进行计算。本次设计主要了对于共模输入电压等指标提出了要求,详见下表。在正文中将就如何满足这些指标进行分析与讨论,并将计算结果利用cadence进行仿真,得出在0.35um工艺电路的工作情况。共模输入电压定在(玲0+VSS)/2升环宜流增益60dB单位增益带宽I30MHz相位裕度60degree转换速率1黄载电客=3pF铮态功耗(电流)1mA电路分析课程设计的电路图如下:M1-M5组成,其中M1与M2为NM

2、OS差分输入对管,为第一级提供恒定的偏置电流。M6、M7以及跨接在M6栅漏两端(即第二级电路输入输入级(第一级)放大电路由M3与M4为PMOS有源负载,M5输出级(第二级)放大电路由与输出两端)的电容Cc组成,其中PMOS管M6为共源极接法,用于实现信号的放大,而M7与M5功能相同,为第二级提供恒定的偏置电流,同时M7还作为第二级的输出负载。Cc将用于实现第二级电路的密勒补偿,改变Cc的值可以用于实现电路中主极点与非主极点分离等功能。偏置电路由恒流源旧和以二极管形式连接的M8组成,其中M8与M5,M7形成电流镜,M5和M7为相应电路提供电流的大小由其与M8的宽长比的比值来决定。设计指标本模块将

3、根据设计要求的指标逐一进行分析:开环直流增益:考虑直流增益时忽略所有电容的影响,画小信号图如下:IrtGm1*Vin口。2,4Vds1Gm6*Vds1ro6,7Vout丫Ti丫T由小信号图可以得到电路中的直流增益为:K=-扎讥区湛血膈7式中和2,4=,考虑到差分输入对管的一致性,故&n:l代为表示。|(W/L)l=(W/L),从而临=临,故上述表达式中用同时,考虑到下式:以及表达式:r-ATI从而可以将直流增益表达式表述为:A二.一5一(电I命(*)&十七)同时可以将入用替换,可以得出增益的大小在设计时只与MOS管的过驱动电压和沟道长度有关,当过驱动电压确定时(一般选取0.2V),则需要通过增

4、加沟道长度L来提高增布0由于对于0.35um的工艺库并不熟悉,可以通过对单管进行dc仿真,得到所需的厄利电压等参数,但在实际应用中并不需要,主要做法是根据计算得到的电路偏置电流,通过确定的过驱动电压进行单管仿真得到合适宽长比的工作在饱和区的MOS管。单位增益带宽(GBW0:分析GBW时需要考虑电路在高频条件下的工作情况,小信号图如下:Gm1*Vin(c【为环叽环町以及q之和,41同理)上图中忽略了M3点产生的极点,原因有两个:1.M3点产生的极点大小为村IC&i临J,约等于伊*!*在GBW之外;2.由于小信号电流经过M1再经过M3,M4电流镜与直接经过M2到达输出的电流两者之间为相加形式,即产

5、生了一个前馈通路,从而将引入一个零点,又由于两条通路的放大倍数一致,从而引入的零点为极点的两倍。引入的零点将对极点进行补偿,进一步削弱了极点对增益以及相位裕度的影响,从而对于M3点的极点可以忽略。对于上图中的情况进行分析可得到有极点:1Pi对浦遥制&扁可同时还存在一个零点为:由于九4&演,所以主极点为P】,从而得到同时考虑到相位裕度的要求,由于负极点以及正零点均会是相位恶化,对于双极点系统,通常要求:(对于本课程设计考虑到有正零点介入,将在电路设计中具体分析。)所以对于零点越远,其与GBW的关系基本由和用116的比值决定,周|仙越大越好;对于非主极点,从表达式中可以看出Cc越大,GBW越小(P

6、1越小),巧越大,可视为实现了两个极点的分离。可以近似认为需要满足以下要求:当CCCiH时,2菖心30MHzGBW=me,吨(电1命从上式可以计算的扇A18.81M,即1537.61(/12. 根据相位裕度的要求:PM60”为实现相位裕度的要求,用下式进行估算:GRWGBWPM=90-Cretan-arttanA自俨p2z1IiPM=60.2),即非主极由于=挥L,所以p2,要求p23GBW(当p2=3GBW时,点在3GBW之外,零点在9倍GBW之外能够实现。则可以得到下式:%&祯即&仙hlI对于相同的%疽则可以得到:保529扇根据SR的表达式:SR30V/usR=rnin(SRmrSReJ根

7、据前两个分析得到的结果:上!厂1|)翡71串以函=SRint*3也所以得到:ZBS1镇im=V-拥讴LC.r.,atIrsee21A30进一步计算得到:DSjusi;SR与GBW要求:将该结果与GBW分析中得到的结果进行比较可以得到,同时满足*DS5A373/13. 直流增益的实现:Av60dB.4WPA,=-j*)】()/十%)1同时利用亍二V可以得到:4*EN七EP=殍%);瓦-匕山(电峋+VepUM*+处血)从上式可以得到A*至于沟道长度L和过驱动电压有关,在过驱动电压设置为0.2V的情况下,为实现大的直流增益,需要增大沟道长度L,故统一选取MOS管沟道长度L=3Lmin=1um,采用此

8、沟道长度来进行设计。4. 宽长比数据设定:由于对于工艺库没有了解,不清楚uCox等参数的数据,所以采用仿真的的方法设计出在确定偏置电流和过驱动电压下合适的MOS管宽长比。出于留足余量的考虑,同时由于功耗要求相对宽裕,设计时取、=日血=,上7=BOOuA。设计宽长比参数如下:(W/L)l=(W/L)2=5(加3=(W/L)4=10(W/L)s=(W/L)a=5(W/L)fi=200(W/L)7=50五、Cadence仿真Av图,零极点图,电路图,六、结论与讨论本次课程设计结合我本人所上的ASIC实验的课程设计利用Cadence设计完成,对于自己完成的设计总体来说数据均已达标。但我认为依然可以从如

9、下角度进行改进:1. 分别就低功耗和高速两个角度进行设计,由于此次设计过程中对于各项参数都留了很宽裕的空间(特别是相位裕度,在初期设计时感觉比较难满足),所以造成了M6,M7两管的过大,虽然如此提供了相对好的相位裕度,功耗上的损失却很大。故从低功耗的角度可以减小M6,M7的尺寸,使其恰好工作在设计指标的范围内。而对于高速角度,可以增大M1,M2等第一级MOS管的尺寸同时第二级M6,M7适当减小,这样第一级的电流增加可以有效的提高SR对于MOS管沟道长度的设计,在本次设计中直接将L全部定义在了1um,但是L的选择从一定程度上影响了电路最后的面积,同时对于1/f噪声等也一会造成影响,所以是否可以考虑分开划分MOS管的沟道长度。不过对于本设计有一定的难度,因为M6与M3,M4要做到匹配,同时M7也最好能够与M5,M8做到匹配,所以沟道长度都需要选取一致。根据以上一些想法,我对电路设计进行了一些修改得到以下的方案。

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。