四位二进制加法计数器

四位二进制加法计数器

《四位二进制加法计数器》由会员分享,可在线阅读,更多相关《四位二进制加法计数器(22页珍藏版)》请在装配图网上搜索。

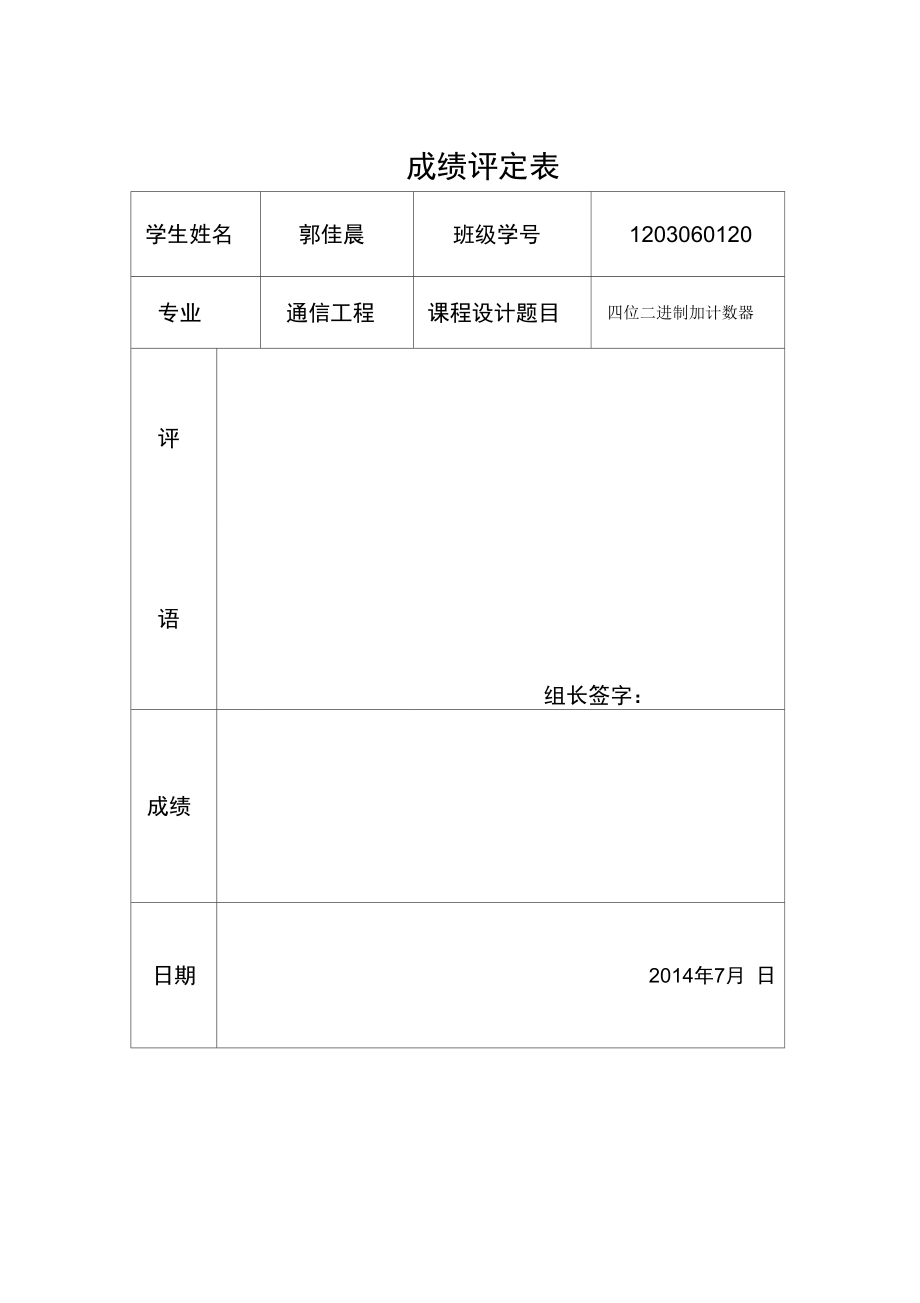

1、成绩评定表学生姓名郭佳晨班级学号1203060120专业通信工程课程设计题目四位二进制加计数器评语组长签字:成绩日期2014年7月 日课程设计任务书学院信息科学与工程学院专业通信工程学生姓名郭佳晨班级学号1203060120课程设计题目四位二进制加计数器(缺 0110,0111,1010,1011 ,)实践教学要求与任务:1、了解数字系统设计方法2、熟悉VHDL语言及其仿真环境、下载方法3、熟悉Multisim环境4、设计实现四位二进制加计数器(缺 0110,0111,1010,1011)工作计划与进度安排:第一周 熟悉Multisim环境及QuartusH环境,练习数字系统设计方法, 包括采

2、用触发器设计和超高速硬件描述语言设计,体会自上而 下、自下而上设计方法的优缺点。第一周在QuartusH环境中用VHDL语言实现四位二进制加计数器(缺0110,0111,1010,1011)显示结果波形,并下载到目标芯片上,在实验箱上 观察输出结果。在Multisim环境中仿真实现四位二 进制加计数 器(缺0110,0111,1010,1011 ),并通过虚拟器验证其 正确性。指导教师:2014 年7月 日专业负责人:2014年7月 日学院教学副院长:2014年7月 日摘要Quartus II是Altera公司的综合性 PLD/FPGA开发软件,支持原理图、 VHDL、 VerilogHDL

3、以及 AHDL (Altera Hardware Description Language 等多种设计输入 形式,内嵌自有的综合器以及仿真器以完成从设计输入到硬件配置的完整 PLD设计流程。Multisim 是 In teractive Image Tech no logies (Electro nics Workbe nch 公司推出 的以Windows为基础的仿真工具,适用于板级的模拟/数字电路板的设计工作。 它包含了电路原理图的图形输入、电路硬件描述语言输入方式,具有丰富的仿真分析能力。Multisim为用户提供了丰富的元器件,并以开放的形式管理元器件, 使得用户能够自己添加所需要的元器

4、件。本次数电课程设计使用 Quartus II仿真环境以及VHDL下载和Multisim仿 真环境来编译实现四位二进制同步减法计数器。 在Multisim中选用四个JK触发 器来实现四位二进制减法计数器。 运用卡诺图求解时序方程。逻辑电路图中,四 个小红灯即为显示器,从右到左显示时序图中的十二种状态,其中,灯亮表示“ 1”, 灭表示“ 0”,从而达到计数目的。关键字:VHDI硬件描述语言、四位二进制加计数器、QUARTUS、Multisim、目录一. 课程设计目的.1二. 课设题目实现框图.1三. 实现过程 .1(一)VHDL勺编译和仿真 .11. 建立工程 .12. VHDL 源程序43.

5、编译及仿真过程 64. 引脚锁定及下载 .95. 仿真结果分析 11(二)电路设计 111 求驱动方程 122. 基于 Multisim 的设计电路图 .153. 逻辑分析仪显示的波形 . 154. 仿结果分析 16四. 设计体会 16五. 参考文献 17课程设计目的1. 了解同步加计数器的工作原理和逻辑功能;2. 学会用VHDL语言对计数器进行编译和仿真;3. 掌握Quartusll的使用方法;4. 掌握Multisim的使用方法。状态图0000 01A1111 110】、课程设计实现框图0010 0011 100 -010114叶 110 001 T000(缺少 0110,0111,101

6、0,1011)三、实现过程(一 )VHDL的编译和仿真1. 建立工程创建一个工程,具体操作过程如下:(1) 点击File - New Project Wizard 创建一个新工程,如图1;图1(2) 点击Next,为工程选择存储目录、工程名称、顶层实体名等,并点击Next,若目录不存在,系统可能提示创建新目录,如图2所示,点击“是”按钮创建新目录;图2(3) 系统提示是否需要加入文件,在此不添加任何文件,如图3;Select he iJeian Hiles- pqu wanl to includE in the goiiEit, Qid Add All In add all des an fi

7、le iin Ihu project Lfaeciury to Ikit? pojkicL. IM 归 ju ca-i 吕轲ddd design files to Lpt? pujeci: LiteFile nameifcc nfliincSpecify lhe oath names of any nan defauk libraiicsV.卫 ackFioii xJh. | 眼梢图3(4) 点击Next,进入设备选择对话框,如图4,这里选中实验箱的核心芯片CYCLONE 系列 FPGA 产品 EP1C6Q240C8;(5) 点击Next,系统显示如图5,提示是否需要其他EDA工具,这里不选任

8、何其他工具;Ww Prnipft Wi7ardl: FRA Tool Settings page 4 of 5Speedy tie JtFwr EDA tools - in dddkion to theQuartix II :offwane - used vjith the prqecr.厂iEDAd頤恋誠逐迎矗制浊di;iFafmat: |E&lF厂 Not cvaiabf=厂 EDAsirrulariontod;zllForm孔 |VHDL 厂 Not avalabfejJ厂 EDA timrigtootAFnmn卄 IjJF- Mt irvalcibbt B址k | Hbtt FifdM

9、h | 取睛 |图5(6) 点击Next后,系统提示创建工程的各属性总结,若没有错误,点击Finish, 工程创建向导将生成一个工程,在窗口左侧显示出设备型号和该工程的基本信 息等。2. VHDL源程序 library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;en tity coun t16 isport(cp,r:in std_logic;q:out stdo gic_vector(3 dow nto 0);end coun t16;architecture behavioral of coun t16

10、 is signal count:std_logic_vector(3 downto 0); beginprocess(cp,r)beginif r=0 then count=0000;elsif cpevent and cp=1 thenif count=0101 thencount=1000;else count=count+1;if count=1001 then count=1100;else count=count+1;end if;end if;end if;end process;qNew 创建一个设计文件,选择设计文件的类型为 VHDL File, 如图 6;(2) 在编辑窗口

11、中编辑程序,如图 7;Aron m.TlA 皿mL卵gzawtnrtf ? iIoxie: 1 J rR4 mwcli 轴兰 il LiKWSJ卜:旳I母冷;.出.斗 A 叱 g hiTr, -vs-rp ) .n :r 社“ X ?AL-NFev7 Jh*_ Jll 土 4 沁 吗 IJfMi“ i iiriij,i I*ps wrSt v*图7(3) 输入程序后,存盘;(4) 点击Process in g-Start Compilatio n编译该文件,系统将开始编译,结束后,给出提示信息和编译结果,如图8所示:bii411JL匚*神.i屮童 gim irrcwsri w+i h* 冲E

12、:idd!elFlm幕罰.IB FL-I jSAihliwi 1 svlhR. | F M_| d-i I Im- 3_| ! 4击*厂戸:*, 巳卜pfa Fin L mlLbLiiPr!? h iM僵m M也|! 电 L 911 LI IM L4RF? Ki hiz inOL 袖ELZkCXT|4Th:*2 0 C C I il ln K-. m i o u) q f I(91)(5) 建立时序仿真文件,选择“Vector Waveform File”,如图9;|卜阳-f斗L |匸PNF-.I-血 Cvl-rM- i?T3 1二.一 t 5 S 比硕弓三i NBJl!MkLIllTZ vl

13、LBFlnFln吧rlMl.Mh 藍mu左-tMwy 如 MW DwyaOklci *. F r F4 饰爲*I*? 士 vrtTrt|Hh Fk rdX.I*lFihWbLAiMna*rhat4| iWf w| 血壬恫他g * 員电*“曜fir: hsiJlv:ui iwr-Lt ihe! idLL a* : aE tm -rzrmii: imctvdVifl-lffl Tpovj piW tWPRLPWIF *PM4-W IWr|r 411*441ZiJr: ZlKfc -*i Zatwi-JfcL Esn lv :arE:djrtvd 0 IT? 忙 Kt Ex 工=!= zvJrar

14、|fi i 他:“w 甲LW4 *W n.LHS fefrh w WIFI-mipifE 門裤*.广 M图9(6) 出现的界面中,在 Name空白处击右键,Insert Insert Node or Bus,单击W呃凸E.,单击丄,再单击目oqOK并对其进行仿真,如图10所示;| 毎 CAMlELritf1!:Cv卜51;乍(1靠 MwrP rCMIW 年M曲 f3iEjictpawwTi 古Iff ljuTCIE|:-i|E十Ecoijjila Tn j.1 *b-L 出舌 4/ktu EI *芬 P ail4ti_ ri a ii+!.*H- if - *:- 卜八-wr驚 pry:H占

15、blci)| C? -?n i“l ;靳二 fi 】、Ed! EM kiluK *1 tutlW.超,* Cf.h Fi hp-MMi t号riAdb 晦Hi *谢科豪Hcrkw Flgv Tirnmri1 .#8 FE ktnvMi -tinMfiarEiaimw f Mhp :*ndrt:n II片ir0| Fh Eir R:. h-*| Flog/(8)仿真后存盘4.引脚的锁定及下载各引脚的锁定如表1所示:信号名称引脚cp28q3114q2115qi116qO117r58表1引脚的锁定和下载分别如图12和图13所示:图135.仿真结果分析结果分析:由仿真波形图可以清晰的看出减法计数器的工

16、作过程,由0000起依次递加,最后加1111两个状态。当复位键复位后,回到 0000重新开始循环。2. Multism实现过程1 求驱动方程相关结构示意框图和状态转换图见上 (二)所示步骤。选择四个时钟脉冲下 降沿触发的JK触发器,因要使用同步电路,所以时钟方程应该为 CP0 CR CP2 CP3 CP(1)求状态方程由所示状态图可直接画出如图 2.1所示电路次态Q: 1 Q; 1 Q1n 1 Q01 1的卡诺 图,再分解开便可以得到如图2.2所示各触发器的卡诺图。要的逻辑门外,没有专门的运算电路;计算结果由电路中的各个触发器记忆和表 示;计数器计满之后自动归零,若再输入CP脉冲又会从零开始计

17、数,在CP脉冲 作用下,它总是周而复始循环工作的。 Q; Q0Q3n 1000111100000010010010000110101011000xxxxxxxx1111011110000011111010011100xxxxxxxxn 1b. Q 3的卡诺图:q:q;Q3n Q2 000111100000000101Lxx11110L1 r1011JxxL.-Jc. q2 1的卡诺图: Q:QoQan q20001111000o10oir 10Xr力Xii产1101JJvJio0XXn 1d. Q1的卡诺图:1n QoQa Q200011110000I10( 、10100XX110厂r1011

18、000XXL 丿e. Q0 1的卡诺图: Qin QoQa q2000111100011000110XX1110011010XX(2)状态方程Q31Qg: Q31Q21 Qg:Q; 1Q21Q1nQ01 Q3nQ1nQ(n Q31Q21Q1nQ;1Qg; Qg; Q3nQ;Q0qS 1Q01 q3Q;(3)驱动方程JK触发器的特性方程 Qn 1 JQn KQn将状态方程与特性方程比较,可得驱动方程,如下J3 QMK3QWJ 2Qn Q?QinK2Q0 QQ QQJiQMQ1QTqT)Ki Q0Jo 1Ko12.基于Multisim的设计电路图根据上面计算出的结果的不同J和K值选择不同的元件进行

19、电路的连接。 电路图3.逻辑分析仪显示的波形逻辑分析仪显示的波形如图15所示:4. 仿真结果分析结果分析:由图15可以清楚地看到在一个周期内,由小到大,依次完成了加计 数器的功能。由于缺省了 0110,0111,1010、1011这两个状态,波形仿真中状态 发生了跳变,即由0101跳变到1000,由1001跳到1100,完成一个周期计数后, 下一周期继续 从0000开始,不断循环往复。四、设计体会在本次数字电路课程设计中,我受益匪浅。我原本对二进制加法计数器这一 节学习不是很透彻,对于相关设计过程和分析方法并不大熟练。 在同学和老师的 讲解下,最终还算顺利完成。这对我以后学习相关的课程以及进行

20、更高层次的数 字电路设计都奠定了不错的基础。在设计过程中, 出现了各种各样的问题, 有些是单一原因引起的, 有的是综 合原因引起的, 这些都很考验我的毅力与坚持。 但是我掌握了研究这类问题的方 法,即问题解决的过程就是要从问题所表现出来的情况出发, 通过反复推敲, 作 出相应判断,逐步找出问题的症结所在,从而一举击破。对于数字电路设计, 尤其在使用 Multism 进行逻辑电路的连接与分析时, 这 种分析解决问题的能力就更为重要。 要在复杂的电子器件和密密麻麻的连线中找 出头绪来, 并不是一件很容易的事情。 往往要从新再来一次, 但是这样的问题就 出在计算上,尤其是在化简卡诺图时, 务必小心谨

21、慎, 一个字符写错或者漏掉一 些信息,相应得出的驱动方程就会有天壤之别, 自然逻辑电路就不能实现最初的 设计功能。 而且在连线的过程中一定要仔细的找准位置, 一旦出错需要删除某些 线的时候一定要删准确。因此,我把这次课程设计看成一次综合学习的机会。在学习过数字电路技术基础简明教程 之后,我已经算是掌握了一定的数 字电路设计的基础以及相应的分析方法、 实践能力以及自学能力。 虽然遇到了不 少问题,但是在向老师和同学请教的学习过程中,我又改正了不少错误的认识, 对数字电路的设计与分析方法的掌握也有了一定的提高, 我相信这些知识与经验 对以后的学习会有极大的帮助。五、参考文献1 数字电子技术基础简明教程(第三版)高等教育出版社余孟尝主编2 数字集成电子技术教程高等教育出版社 李世雄,丁康源主编3 数字逻辑与硬件描述语言实验指导书沈阳理工大学信息学院技术中心王东明,喻红婕, 吴迪主编4 康华光电子技术基础数字部分.康华光.北京:高等教育出版社,2000.5.VHDL实用教程.潘松,王国栋,西安:电子科技大学出版社,2001.

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 嵌入式系统概论-以S3C2440核心为架构课件

- 地理事象的季节变化课件

- 地理中外著名旅游景观欣赏课件

- 地理中图版选修5第一章第二节主要自然灾害及其分布课件

- 地理中考复习-地图课件

- 北师大版历史八年级下册第17课《筑起钢铁长城》课件1

- 北师大版历史八下《祖国统一的历史大潮》课件5

- 北师大版历史八下《欣欣向荣的科教文体事业》3课件

- 北师大版历史八下《蓝色的地中海文明》课件

- 北师大版历史九年级下册第10课“冷战”与“热战”丁飞鹤T-课件

- 北师大版历史八下第17课《大河流域的文明曙光》课件

- 北师大版历史九上1718课课件

- 高中化学热力学复习10多重平衡与化学计算ppt课件

- 高中化学第1章化学反应与能量转化第3节化学能转化为电能电池ppt课件1鲁科版选修

- 高中化学第三节玻璃、陶瓷和水泥公开课课件