四相步进电机定位控制系统

四相步进电机定位控制系统

《四相步进电机定位控制系统》由会员分享,可在线阅读,更多相关《四相步进电机定位控制系统(21页珍藏版)》请在装配图网上搜索。

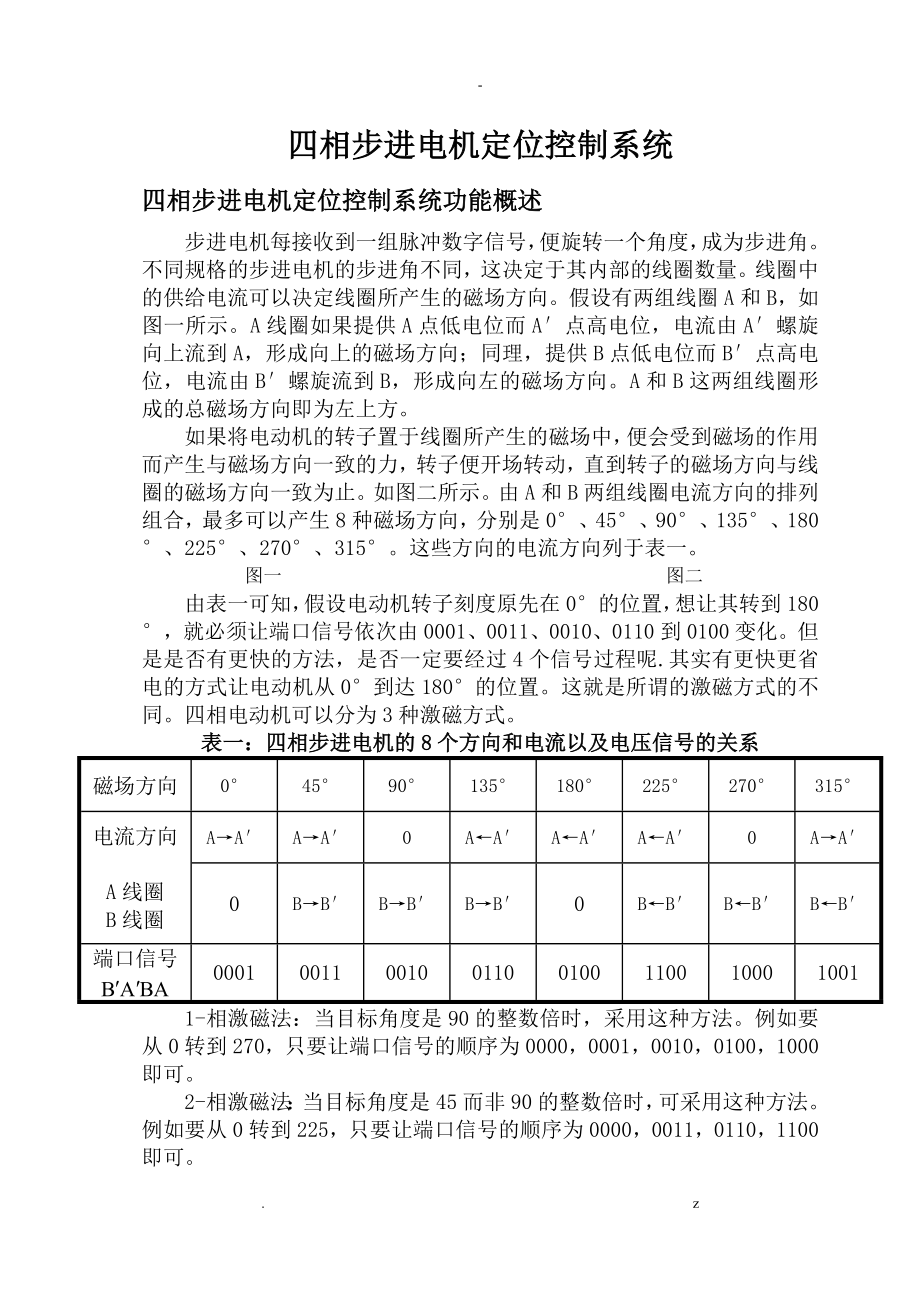

1、-四相步进电机定位控制系统四相步进电机定位控制系统功能概述步进电机每接收到一组脉冲数字信号,便旋转一个角度,成为步进角。不同规格的步进电机的步进角不同,这决定于其内部的线圈数量。线圈中的供给电流可以决定线圈所产生的磁场方向。假设有两组线圈A和B,如图一所示。A线圈如果提供A点低电位而A点高电位,电流由A螺旋向上流到A,形成向上的磁场方向;同理,提供B点低电位而B点高电位,电流由B螺旋流到B,形成向左的磁场方向。A和B这两组线圈形成的总磁场方向即为左上方。如果将电动机的转子置于线圈所产生的磁场中,便会受到磁场的作用而产生与磁场方向一致的力,转子便开场转动,直到转子的磁场方向与线圈的磁场方向一致为

2、止。如图二所示。由A和B两组线圈电流方向的排列组合,最多可以产生8种磁场方向,分别是0、45、90、135、180、225、270、315。这些方向的电流方向列于表一。图一 图二由表一可知,假设电动机转子刻度原先在0的位置,想让其转到180,就必须让端口信号依次由0001、0011、0010、0110到0100变化。但是是否有更快的方法,是否一定要经过4个信号过程呢.其实有更快更省电的方式让电动机从0到达180的位置。这就是所谓的激磁方式的不同。四相电动机可以分为3种激磁方式。表一:四相步进电机的8个方向和电流以及电压信号的关系磁场方向04590135180225270315电流方向A线圈B线

3、圈AAAA0AAAAAA0AA0BBBBBB0BBBBBB端口信号000100110010011001001100100010011-相激磁法:当目标角度是90的整数倍时,采用这种方法。例如要从0转到270,只要让端口信号的顺序为0000,0001,0010,0100,1000即可。2-相激磁法:当目标角度是45而非90的整数倍时,可采用这种方法。例如要从0转到225,只要让端口信号的顺序为0000,0011,0110,1100即可。1-2-相混合激磁法:按照表二中所列的信号顺序。表二:四相步进电机3种不同激磁方式对应提供的端口信号磁场方向04590135180225270315端口信号000

4、100110010011001001100100010011-相激磁2-相激磁1-2-相激磁四相步进电机定位控制系统的VHDL源码及注释-四相步进电机例如程序library IEEE;use IEEE.std_logic_1164.all;use IEEE.std_logic_arith.all;use IEEE.std_logic_unsigned.all;entity step_motor isport (reset:in STD_LOGIC; -系统复位信号 dir: in STD_LOGIC; -步进电机正反转方向控制开关0:逆时针;1:顺时针 clk: in STD_LOGIC; -

5、系统时钟FPGA内部提供的4MHz的时钟信号 ini: in STD_LOGIC; -使能开关 manner: in STD_LOGIC_VECTOR (1 downto 0); -激磁方式的选择开关00:自动选择激磁方式;-01:1-相激磁;10:2-相激磁;11:1-2-相激磁 angle: in STD_LOGIC_VECTOR (7 downto 0); -步进角的倍数设定输入键 baBA: out STD_LOGIC_VECTOR (3 downto 0); -步进电机的状态输出end step_motor;architecture stepmotor_arch of step_mo

6、tor issignal count: INTEGER range 0 to 7; -内部电路的计数累加器,用于产生输出所需对应的状态signal tInc: INTEGER range -2 to 2; -设定累加器所需的累加/减计数值signal tIni: INTEGER range -1 to 0; -设定累加器所需的计数初值signal angleDnCount: INTEGER range 255 downto 0; -设定步进角所需的计数次数signal angleDntDec: INTEGER range 2 downto 1; -设定步进角所需的累减计数值begin -步进电

7、机方向设定电路模块该模块的功能是设定步进电机的旋转方向顺时针或逆时针,并设定电机在顺时针转动或逆时针转动时所需的初值与累加/减值。 process(dir,manner,angle) begin if dir=0 thencase manner is when 01 = -1-相激磁 tIni=0; tInc=2; angleDntDec -2-相激磁 tIni=-1; tInc=2;angleDntDec -1-2-相激磁 tIni=0; tInc=1; angleDntDec -自动选择激磁方式-angle为偶数即角度为90的倍数时,采用1-相激磁,否则2-相激磁 if (angle(0)

8、=1) then -2-相激磁 tIni=-1; tInc=2; angleDntDec=2; else -1-相激磁 tIni=0; tInc=2; angleDntDec -1-相激磁 tIni=0; tInc=-2; angleDntDec -2-相激磁 tIni=-1; tInc=-2; angleDntDec - 1-2-相激磁 tIni=0; tInc=-1; angleDntDec -自动选择激磁方式 if (angle(0)=1) then -2-相激磁 tIni=-1; tInc=-2; angleDntDec=2; else -1-相激磁 tIni=0; tInc=-2;

9、angleDntDec=2; end if; end case; end if; end process; -步进电机步进移动与定位控制电路模块该模块的主要功能是利用ini使能开关,将数值传到该模块中,并配合输入的clk系统时钟作为同步控制信号,进展步进电机的步进移动与定位控制。 counting_reset: process(reset,ini, angle, clk) begin if reset=1 then -复位低电平有效 count=0; angleDnCount=0; elsif clkevent and clk=1 then if ini=0 then -使能高电平有效 cou

10、nt=0+tIni; angleDnCount=CONV_INTEGER(angle); else count angleDntDec then -判断是否已到达设定位置 angleDnCount = angleDnCount-angleDntDec; else angleDnCount = 0; end if; end if; end if; end process; -编码输出电路模块该模块的功能是将count与angledncount产生的数值经过编码,并利用baBA输出连线信号,将结果输出显示。 baBA =7;end stepmotor_arch;四相步进电机定位控制系统的模块图四相

11、步进电机定位控制系统的仿真结果自动模式,顺时针,旋转角为45*11的情况:自动模式,顺时针,旋转角为45*16的情况:1-相激磁,逆时针,旋转角为45*7的情况:1-相激磁,顺时针,旋转角为45*7的情况:2-相激磁,逆时针,旋转角为45*17的情况:2-相激磁,逆时针,旋转角为45*17的情况:1-2-相激磁,顺时针,旋转角为45*11的情况:1-2-相激磁,顺时针,旋转角为45*8的情况:直流电机速度控制系统直流电机速度控制系统功能概述驱动电路称为桥式驱动或是H型驱动电路如右图所示,采用的控制方法称为脉冲宽度调制法PWM,即利用晶体管on-off导通-不导通进展控制的方法。使用FPGA纯数

12、字式的控制时,假设电机速度从静止开场加速,首先Q1、Q2必须维持导通一段时间,此时电机所承受的电压约为供电电压U,称之为强加速。待速度接近目标速度时,加速可以减缓,此时Q1、Q2和Q3、Q4轮流导通,只是Q1、Q2在一个周期内所导通的时间ton比Q3、Q4导通的时间toff长一些,此时称为弱加速。任何时候,电机所承受的平均电压U0可表示为U0=U*tontofftontoff。如果速度已经到达目标,便可以调整ton和toff的时间比例使之相等,此时平均电压为零,称为定速控制。由此可知,平均电压假设为正值,是加速控制;负值时是减速控制;为0时即到达匀速。当然,还涉及到确定电机目前的速度是多少,比

13、目标速度快还是慢,也就是速度检测的问题,常用的方法是光遮断法,在此就不再论述了。在程序仿真时只简单的输入固定的速度模拟一下。直流电机速度控制系统的VHDL源码及注释library IEEE;use IEEE.std_logic_1164.all;use IEEE.std_logic_arith.all;use IEEE.std_logic_unsigned.all;entity motorctrl is port (clk: in STD_LOGIC; -FPGA内部提供的4MHZ的时钟信号 reset: in STD_LOGIC; -系统内部自复位信号 speed_now: in STD_L

14、OGIC_VECTOR (7 downto 0); -速度检测编码器检测到的当前速度 target_speed: in STD_LOGIC_VECTOR (7 downto 0); -设定电机预定到达的目标速度 th_speed: in STD_LOGIC_VECTOR (7 downto 0); -设定电机进入弱加速时的临界速度差值 pwme: out STD_LOGIC); -脉宽调制的输出,负责控制电机转动的信号end;architecture motorctrl_arch of motorctrl is-define the signal_structure and flow of t

15、he device定义内部信号signal t125: INTEGER range 0 to 124; -125个时钟的计数器signal t375: INTEGER range 0 to 374; -375个时钟的计数器signal t500: INTEGER range 0 to 499; -500个时钟的计数器signal dth: STD_LOGIC_VECTOR (7 downto 0); -设定电机进入弱加速时的临界值dth=target_speed-th_speedsignal pwm: STD_LOGIC; -负责产生脉宽调制的信号,提供正确的输出-相位类型,负责产生正反转两种

16、状态信号,用来控制电机的加速和减速phase有2种状态:状态0:phase=phb1,电机正转加速状态;状态1:phase=phb2,电机反转减速状态。type phase_type is (phB1, phB2);signal phase: phase_type;-速度类型,负责产生加速、弱加速、减速与定速4种状态信号,以控制电机的转速speeding4种状态:状态0:speeding=upa,电机进展加速动作; 状态1:speeding=upb,电机进展弱加速动作;状态2:speeding=dn,电机进展减速动作;状态3:speeding= target_speed th_speed ,则

17、进展弱加速控制,ton = (3/4)ktclk, toff = (1/4)ktclk;3) 如果speed_now target_speed,则减速控制,ton = (1/4)ktclk, toff = (3/4)ktclk;另外,方向控制通过将pwme信号的输出反向。根据上面的分析,需要3个分频器,分别产生ktclk ,(1/4)ktclk 和(3/4)ktclk的周期信号。假设时钟周期tclk为10MHz,电机频率为20kHz,因此k=10MHz/20kHz =500,(1/4)k=125,(3/4)=375,这也就是定义t125,t375,t500三个计数器的原因。peeding_ma

18、chine: process (reset,clk)begin if reset=1 then -复位高电平有效 speeding = UPA; dth=00000000; elsif (clkevent and clk=1) then dth -情况1 if (speed_now = target_speed) then speeding target_speed) then speeding = Dn; elsif (speed_now dth) then speeding =dth) and (speed_now 弱加速临界速度&=dth & speed_now 限速speed_now

19、target_speed现速弱加速临界速度speed_now dth speeding -情况2 if (speed_now = target_speed) then speeding = final; elsif (speed_now dth) then speeding =dth) and (speed_now target_speed) then speeding target_speed) then speeding = Dn; endif; UPA加速UPB弱加速Dn减速Final匀速现速=限速speed_now = target_speed现速弱加速临界速度speed_now 限速

20、speed_now target_speed现速弱加速临界速度&=dth & speed_now -情况3 if (speed_now = target_speed) then speeding = final; elsif (speed_now dth) then speeding target_speed) then speeding =dth) and (speed_now target_speed) then speeding = UPB; end if;UPA加速UPB弱加速Dn减速Final匀速现速=限速speed_now = target_speed现速弱加速临界速度speed_

21、now 限速speed_now target_speed现速弱加速临界速度&=dth & speed_now -情况4 if (speed_now target_speed) then speeding =dth) and (speed_now target_speed) then speeding = UPB;elsif (speed_now = target_speed) then speeding = final;elsif (speed_now dth) then speeding = UPA;end if;UPA加速UPB弱加速Dn减速Final匀速现速=限速speed_now =

22、target_speed现速弱加速临界速度speed_now 限速speed_now target_speed现速弱加速临界速度&=dth & speed_now null; end case; end if;end process;-相位控制模块该模块具有以下控制功能:1) 如果希望正向转动即Q1,Q2导通,则使用状态0:phb1;2) 如果希望反向移动即Q3,Q4导通,则使用状态1:phb2;上面的速度设定模块只是对有关的输入信号进展判断,告知FPGA用何种模式进展速度控制,并不产生输出信号pwm。因此,必须设计第二个状态判别器“phase,负责计数与产生pwm脉宽调制信号。phase相位

23、控制器的设计原理如下:phb1状态为Q1,Q2开启即pwme=1,而Q3,Q4关闭即pwme=0的状态,phb2状态为Q1,Q2关闭,而Q3,Q4开启。三极管的开关时间依据所激活的计数器而定。phase_machine: process (reset,clk)begin if reset=1 then -复位高电平有效 t500 = 0; t375 = 0; t125 = 0; pwm=0; pwme=0; phase=phB1; elsif (clkevent and clk=1) then pwme if (speeding=UPA) thent375=374;t125=124;t500=

24、499;pwm=1; -加速状态pwm恒为1,不用计数器 elsif (speeding=UPB) thent500=499;t375=t375-1;t125=124;pwm=1; -弱加速状态pwm输出为1是375个时钟,0为125个时钟 elsif (speeding=Dn) thent500=499;t375=t375-1;t125=124;pwm=0; -减速状态pwm输出0是375个时钟,1为125个时钟 elsif (speeding=final) thent500=t500-1;t375=374;t125=124;pwm=1; -匀速状态下,pwm输出1和0的时间均为500个时钟

25、 else t500 = 0; t375 = 0; t125 = 0;pwm=0; end if;if (t375=0 or t500=0) then -计数器记满后,相位转换 t500=499; t375=374; phase if (speeding=UPA) thent375=374;t125=124;t500=499;pwm=1; elsif (speeding=UPB) thent500=499;t375=374;t125=t125-1;pwm=0; elsif (speeding=Dn) thent500=499;t375=374;t125=t125-1;pwm=1; elsif

26、(speeding=final) thent500=t500-1;t375=374;t125=124;pwm=0; else t500 = 0; t375 = 0; t125 = 0;pwm=0; end if;if (t125=0 ort500=0) then -计数器记满后,相位转换 t500=499; t125=124; phase null; end case; end if;end process;end motorctrl_arch;直流电机速度控制系统的模块图直流电机速度控制系统的仿真结果加速情况弱加速情况匀速情况减速情况按键脉冲宽度处理电路设计原理在时钟上升沿检测按键脉冲,并设

27、置一计数器,记录按键脉冲的持续时间。假设计数器在按键脉冲变为0(即按键松开)时,计数值小于10,则按键无效,输出保持低电平;计数值大于9(计数从0开场)且小于100,则按键有效,输出一个时钟脉冲的高电平;计数值大于99,则超出按键应持续的时间,err输出高电平用以报错。VHDL源程序及简要注释library IEEE;use IEEE.std_logic_1164.all;use IEEE.std_logic_arith.all;use IEEE.std_logic_unsigned.all;entity dithering is port (clk: in STD_LOGIC; -FPGA内

28、部提供时钟信号reset: in STD_LOGIC; -复位信号 put: in STD_LOGIC; -输入按键脉冲err: out STD_LOGIC; -错误指示(题目规定脉冲宽度可能为10100个时钟宽度,超过则报错 get: out STD_LOGIC); -输出脉冲end;architecture arch of dithering issignal t: integer; -计数器beginprocess (reset,clk)beginif reset=1 then -复位信号高电平有效 t = 0; get = 0;err = 0;elsif (clkevent and c

29、lk=1) then if(put=1) then -按键高电平时,计数t = t+1;get = 0;err = 0;else -按键松开释放时,查看计数值if(t10) then -计数值10即脉冲宽度小于10,按键无效get = 0;err = 0;elsif(t10 & 100即脉冲宽度为10100个时钟宽度之间,按键有效get = 1;err = 0;elseget =100即脉冲宽度多于100个时钟宽度,报错err = 1;end if;t = 0;end if;end if;end process;end arch;仿真结果少于10个时钟脉冲的情况10个时钟脉冲的情况多于10个但

30、少于100个时钟脉冲的情况多于100个时钟脉冲的情况帧同步检测电路设计原理利用一个状态机,根据收到的位宽1位的二进制序列来进展状态之间的转换,从而完成帧同步检测。状态机的状态转换如以下图所示:Type0Type0Type0Type0Type0Type0000000111111到达状态5(type5)后,输出一个时钟周期的高电平。VHDL源程序及简要注释library IEEE;use IEEE.std_logic_1164.all;use IEEE.std_logic_arith.all;use IEEE.std_logic_unsigned.all;entity synchro is por

31、t (clk: in STD_LOGIC; -FPGA内部时钟信号 reset: in STD_LOGIC; -复位信号 put: in STD_LOGIC; -位宽1位的二进制序列输入 get: out STD_LOGIC); -检测结果输出end;architecture arch of synchro is-定义状态type synchro_type is (type0, type1, type2,type3,type4,type5);signal phase: synchro_type;beginprocess (reset,clk)beginif reset=1 then -复位信号

32、高电平有效phase = type0;getget =0; if (put=0) thenphase = type1;elsephase get =0; if (put=1) then phase = type2;elsephase get =0; if (put=0) then phase = type3;elsephase get =0; if (put=1) then phase = type4;elsephase get =0; if (put=1) then phase = type5;elsephase get =1; if (put=0) then phase = type1;e

33、lsephase null; end case; end if;end process;end arch;仿真结果赛跑计时用秒表的设计设计原理利用一个状态机,根据key的输入来进展状态之间的转换,从而完成计时及显示功能。状态机的状态转换如以下图所示:图示代表输入(key)/输出(second)Type0Type0Type0Type0Type01/count1/count1/count11/count21/0其中,count指当前计数值,count1,count2分别是第二、三次按下key时记录的时间。VHDL源程序及简要注释library IEEE;use IEEE.std_logic_116

34、4.all;use IEEE.std_logic_arith.all;use IEEE.std_logic_unsigned.all;entity stopwatch is port (clk: in STD_LOGIC; -时钟信号(为了便于仿真,假设100Hz reset: in STD_LOGIC; -复位信号 key: in STD_LOGIC; -按键信号已经经过防抖动和脉冲宽度处理 second: out STD_LOGIC_vector(5 downto 0); -输出记录时间end stopwatch;architecture arch of stopwatch issigna

35、l c : std_logic_vector(7 downto 0); -分频计数器signal count, count1, count2 : std_logic_vector(5 downto 0); -存放器用来暂存中间数据signal sec:std_logic; -分频后周期1s的信号-定义状态type stopwatch_type is (type0, type1, type2,type3,type4);signal phase: stopwatch_type;begindiv_sec:process(reset,clk) -分频得到周期1s的信号beginif reset=1 t

36、hen sec=0;c=00000000;elsif (clkevent and clk=1) thenif (c=99) thenc=00000000;sec=1;else c=c+1;sec=0;end if;end if;end process;process(reset,clk) -状态机,用于状态转换及记录中间数据 beginif reset=1 then phase = type0;count1 = 000000;count2 phase phase = type2;count1 phase = type3;count2 phase phase = type0;count1 = 0

37、00000;count2 null; end case;end if;end if;end process;process(reset,clk) -输出控制beginif reset=1 then second second second second second second null; end case;end if;end process;process(reset,sec) -秒表计数 beginif reset=1 then count count count count count null;when others = null; end case;end if;end process;end arch;仿真结果. z

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。