基于FPGA电子琴

基于FPGA电子琴

《基于FPGA电子琴》由会员分享,可在线阅读,更多相关《基于FPGA电子琴(22页珍藏版)》请在装配图网上搜索。

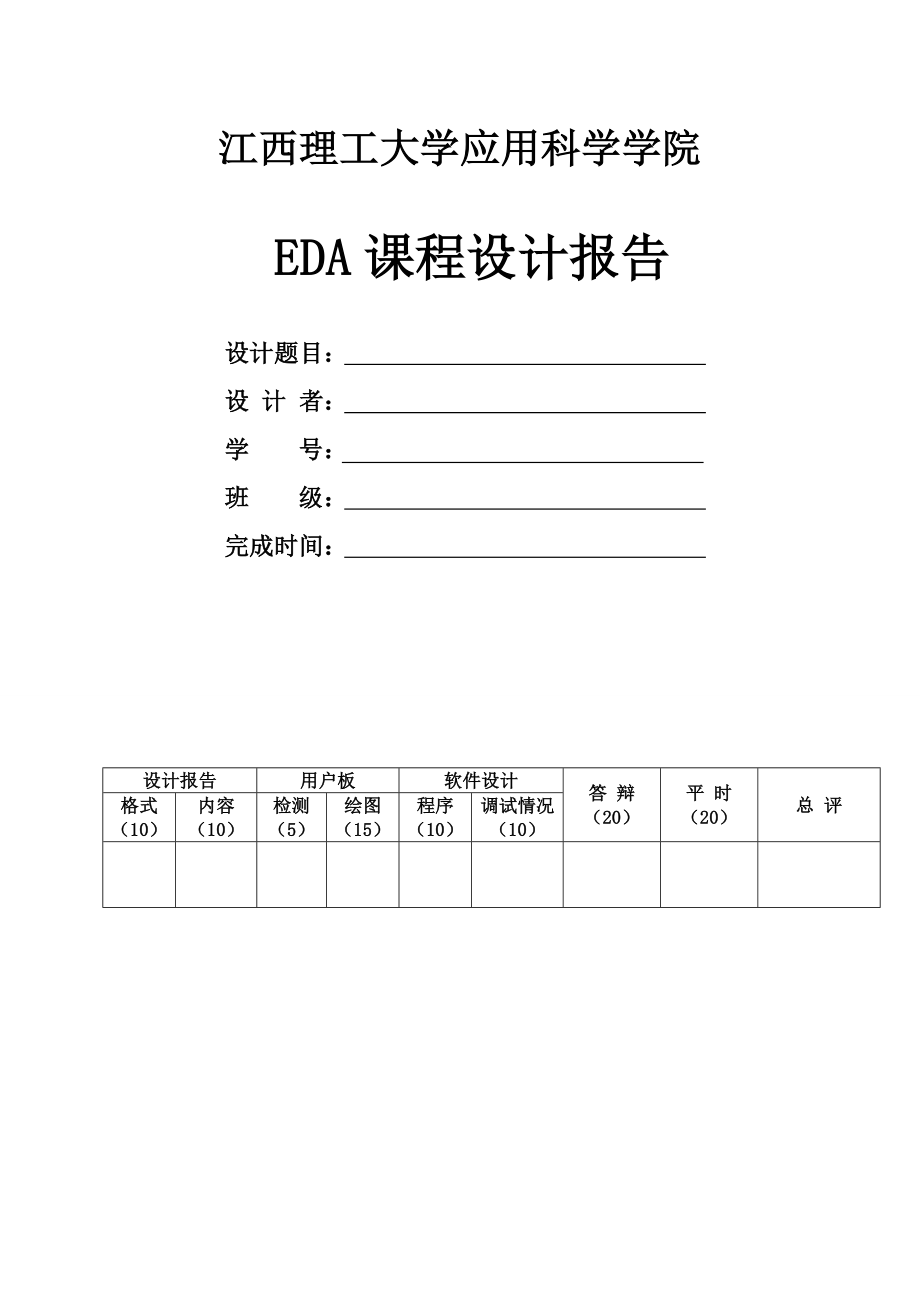

1、江西理工大学应用科学学院 EDA课程设计报告设计题目: 设 计 者: 学 号: 班 级: 完成时间: 设计报告用户板软件设计答 辩(20)平 时(20)总 评格式(10)内容(10)检测(5)绘图(15)程序(10)调试情况(10)摘要 文中介绍了电子琴系统的整体设计,并基于超高速硬件描述语言VHDL在Xilinx公司的Spartan系列的2sc200PQ208-5芯片上编程实现. 电子琴系统的设计包含四个模块,分别是控制输入电路、FPGA、显示电路和扬声器电路。其中FPGA模块的设计是整个电子琴系统设计的核心内容。四个模块的有机组合完成了电子琴自动演奏的功能。文中还详细介绍了FPGA功能模块

2、的原理及其工作时序仿真图。本产品的特点是成本较低,性能稳定,精度高,有一定的开发价值。Design of Electronics_orgon system based on FPGAAbstract: It will introduce the integrate designelectronics_orgon system based on FPGA. The design will be achieved in the 2sc2005pq208 chipof Xilinx corporation with the VHDL(Very High-speed Description-Langu

3、age) The design of Electronics_orgon System consist of 4 parts, they are control input circuit、FPGA、display circuit and speaker circuit. The program design of FPGA is the core of the system design. Four parts combined to achieve the automatic play electronics_orgon system. the article illuminates th

4、e detail of the basic law of FPGA module and its working timing characteristics. Since the most specialty of the product is its low cost、high precision, its worth developing.Keyword: FPGA VHDL Electronics_orgon system Automatic play目 录摘要 1目录. 2第一章 系统设计. 4 第一节 设计要求. . 1.1 基本部分1.2 发挥部分 第二节 设计思路. 整体设计方

5、案. 3.1 方案一.3.2 方案二.3.3 方案三.第四节 比较方案.第二章FPGA简介 6 第一节 FPGA背景第二节 FPGA的基本原理2.1 MHZ_generator模块的原理2.2 NoteTabs模块的原理2.3 ToneTaba模块的原理2.4 Speakera模块的原理第三节 FPGA的基本特点第四节 FPGA基本结构第三章 单元电路设计. 10 第一节 顶层模块(top)的设计 第二节 自动演奏模块(automusic)的设计第三节 音调发生模块(tone)的设计第四节 数控分频模块(speaker)的设计第四章 PS2键盘控制电子琴程序 第一节 VHDL语言简介12第二节

6、 软件设计 第五章 总结心得 13 第六章 参考文献. 14第七章 附录. 15第一章 系统设计第一节 设计要求1.1 基本部分 设计一八音电子琴,由键盘输入来控制其对应的音响。1.2 发挥部分 设计一乐曲自动演奏器,由用户自己编制乐曲存入电子琴,电子琴可以完成自动演奏的功能。第二节 设计思路 通过可编程逻辑器件(PLD)和VHDL硬件描述引言来实现电子琴的基本部分和发挥部分的设计。对于基本部分,设计的主体是数控分频器,对输入的频率进行分频,得到各个音阶对应的频率最为输出。对于发挥部分,则在原设计的基础上,增加一个乐曲存储模块,代替了键盘输入,产生节拍控制(index数据存留时间)和音阶选择信

7、号,即在此模块中可存放一个乐曲曲谱真值表,由一个计数器来控制此真值表的输出,而由此计数器的计数时钟信号作为乐曲节拍控制信号,从而可以设计出一个纯硬件的乐曲自动演奏电路。 通过可编程逻辑器件(PLD)和VHDL硬件描述引言来实现电子琴的基本部分和发挥部分的设计。对于基本部分,设计的主体是数控分频器,对输入的频率进行分频,得到各个音阶对应的频率最为输出。对于发挥部分,则在原设计的基础上,增加一个乐曲存储模块,代替了键盘输入,产生节拍控制(index数据存留时间)和音阶选择信号,即在此模块中可存放一个乐曲曲谱真值表,由一个计数器来控制此真值表的输出,而由此计数器的计数时钟信号作为乐曲节拍控制信号,从

8、而可以设计出一个纯硬件的乐曲自动演奏电路。第三节 整体设计方案3.1 方案一:采用数字逻辑电路制作,用IC 拼凑焊接实现,这种电路很直观,简单方便。但应用数字逻辑电路制作的话,使用的器件较多,连接复杂,体积大,功耗大。电路中焊点和线路较多会,使成品的稳定度和精度大大降低。3.2 方案二: 采用现场可编程逻辑器件(FPGA)制作,利用EDA软件中的VHDL硬件描述语言编程进行控制,然后烧制实现.采用FPGA来设计的原理图如图1.1所示.它由控制输入电路、FPGA、显示电路和扬声器电路组成。控制输入电路显示电路FPGA扬声电路图1.1 采用FPGA设计的电子琴原理方框图 控制输入电路主要是为用户设

9、计的,起到一个输入控制的作用.FPGA是现场可编程逻辑器件,也是本设计方案的核心内容,它是实现电子琴运作的主要控制模块.由设计者把编好的VHDL程序烧制到现场可编程逻辑器件FPGA中,然后通过控制输入电路把乐谱输入到FPGA,产生不同的频率驱动扬声器,发出不同的乐谱.同时也把发出的乐谱符号通过显示器输出.3.3 方案三: 单片机现在已经达到很成熟的阶段了,它的应用也十分广泛. 采用单片机来实现电子琴,它的原理方框图与用FPGA来实现的原理方框图类似,如图1.2所示.控制输入电路显示电路MCU(单片机)扬声器电路图1.2 采用单片机实现电子琴的原理方框图 图1.1和图1.2的基本原理都相同,唯一

10、不同的是一个是用FPGA来制作一个是用单片机来实现.采用单片机来实现电子琴,主要的核心是单片机的设计. 第四节 比较方案 对于电子琴的设计,三个方案均可以实现,但是第一个方案中采用的是数字逻辑电路来制作,该电路硬件所需的器材多,体积庞大,比较复杂,而且精度和稳定度都不是很高.第二个方案采用的是现场可编程逻辑器件来实现, 它的优点是所有电路集成在一块芯片上,此方案所需的外围电路简单,这样它的体积就减少了,同时还提高了系统的稳定度。还可以用Modelsim XE 5.3d软件进行仿真和调试等。设计人员可以充分利用VHDL硬件描述语言方便的编程,提高开发效率,缩短研发周期,降低研发成本;而且易于进行

11、功能的扩展,实现方法灵活,调试方便,修改容易.方案三也有它的优点,但同时也存在缺点.它对设计者的要求比较高,设计者对软硬件必须十分熟悉.和方案二来比它的实验仿真没有方案二简单直观,调试也有一定的难度.在外界环境相同的条件下,方案三设计出来的产品精度和稳定度要比方案二稍微差一些.因此,电子琴的设计我们选择方案二来实现第二章 FPGA简介第一节 FPGA 背景目前以硬件描述语言(Verilog 或 VHDL)所完成的电路设计,可以经过简 单的综合与布局,快速的烧录至 FPGA 上进行测试,是现代 IC 设计验证的技术主流。这些可编辑元件可以被用来实现一些基本的逻辑门电路(比如AND、OR、XOR、

12、NOT)或者更复杂一些的组合功能比如解码器或数学方程式。在大多数的FPGA里面,这些可编辑的元件里也包含记忆元件例如触发器(Flipflop)或者其他更加完整的记忆块。 系统设计师可以根据需要通过可编辑的连接把FPGA内部的逻辑块连接起来,就好像一个电路试验板被放在了一个芯片里。一个出厂后的成品FPGA的逻辑块和连接可以按照设计者而改变,所以FPGA可以完成所需要的逻辑功能。 FPGA一般来说比ASIC(专用集成芯片)的速度要慢,无法完成复杂的设计,而且消耗更多的电能。但是他们也有很多的优点比如可以快速成品,可以被修改来改正程序中的错误和更便宜的造价。厂商也可能会提供便宜的但是编辑能力差的FP

13、GA。因为这些芯片有比较差的可编辑能力,所以这些设计的开发是在普通的FPGA上完成的,然后将设计转移到一个类似于ASIC的芯片上。另外一种方法是用CPLD(复杂可编程逻辑器件备)。 第二节 FPGA的基本原理2.1 MHZ_generator模块的原理 分频器的输入是一个标准时钟频率,输出是每秒12MHZ的频率和8HZ的频率。其内部实际是一个计数器,根据所需要的要求进行不同的分频设计。本程序中已知标准频率为32MHZ,要得到12MHZ和8HZ的频率,通过计算我们可以确定它的分频系数. MHZ_generator模块的工作时序仿真图(略),它的程序见附录2.2 NoteTabs模块的原理 Not

14、eTabs模块其实就是一个乐谱预置器,可设置电子琴演奏的乐谱.原理很简单即来一个脉冲输出一个已设置好的乐谱.假定预先设计的乐谱为3 3 3 5 5 5 6 2 1 1 3 3 3 3 3 3它的输出工作时序仿真图如图2.2所示,程序见附录.图2.2 NoteTabs模块的工作原理仿真图2.3 ToneTaba模块的原理 ToneTaba模块是一个音阶发生器,实质是译码电路,控制音调的预置数.乐谱信号是该模块的敏感信号, 输入的每一个乐谱都将被译成与之相对映的频率从Tone端口输出去控制Speakera模块,让Speakera模块发出不同的音调.ToneTaba模块在将乐谱译成相映的频率的同时会

15、将乐谱的符号从codel输出到显示部分,并判断乐谱是高音还是低音,再从highl端口输出去显示.在ToneTaba模块的设计中tone的计算很重要,tone是根据产生该音阶频率所对应的分频比获得的.此值是通过查表和计算所到,查表我们可以知道每个乐谱符号的频率,然后计算出要得到该乐谱的频率所需的分频系数.例如音符1的发音,通过查表得它的频率是785HZ左右,我们要计算tone的值可由公式:音符频率=振荡频率/(16#7FF#-tone的值)振荡频率是经过分频之后得到的,在此是1MHZ,由公式可计算出tone的值为:773.为了进一步了解ToneTaba模块的工作原理,可假定一些参数进行仿真.设它

16、的输入乐谱为: 3 3 3 3 5 5 5 2 1 1 3 12 15 3 则ToneTaba模块的工作时序仿真图如图2.3所示,程序见附录.图2.3 ToneTaba模块的工作时序仿真图2.4 Speakera模块的原理 模块Speakera中的主要电路是一个数控分频器,它由一个初值可预置的加法计数器和两个分频器构成.数控分频器的功能就是当输入端给定不同的输入时,将对输入的时钟信号有不同的分频比, Speakera模块中的数控分频器就是用计数值可并行预置的加法计数器设计完成的,方法是将计数溢出位与预置数加载输入信号相接即可.当模块Speakera由端口tone获得一个十进制数后,将以此值为计

17、数器的预置数,对端口CLK12MHZ输入的频率进行分频,之后将输出再进行2分频,将脉冲展宽,以使扬声器有足够功率发音,最后由SPKOUT向扬声器输出发声. Speakera模块的工作时序仿真图如图2.4所示,程序见附录.注:为了能清晰的看到输入与输出的关系,第一次分频系数设的是2,第二次分频系数设的是5,第三次是2.图2.4 Speakera模块的工作时序仿真图第三节 FPGA的基本特点1)采用FPGA设计ASIC电路(专用集成电路),用户不需要投片生产,就能得到合用的芯片。 2)FPGA可做其它全定制或半定制ASIC电路的中试样片。 3)FPGA内部有丰富的触发器和IO引脚。 4)FPGA是

18、ASIC电路中设计周期最短、开发费用最低、风险最小的器件之一。 5) FPGA采用高速CHMOS工艺,功耗低,可以与CMOS、TTL电平兼容。 可以说,FPGA芯片是小批量系统提高系统集成度、可靠性的最佳选择之一。 FPGA是由存放在片内RAM中的程序来设置其工作状态的,因此,工作时需要对片内的RAM进行编程。用户可以根据不同的配置模式,采用不同的编程方式。 加电时,FPGA芯片将EPROM中数据读入片内编程RAM中,配置完成后,FPGA进入工作状态。掉电后,FPGA恢复成白片,内部逻辑关系消失,因此,FPGA能够反复使用。FPGA的编程无须专用的FPGA编程器,只须用通用的EPROM、PRO

19、M编程器即可。当需要修改FPGA功能时,只需换一片EPROM即可。这样,同一片FPGA,不同的编程数据,可以产生不同的电路功能。因此,FPGA的使用非常灵活第四节 FPGA基本结构FPGA具有掩膜可编程门阵列的通用结构,它由逻辑功能块排成阵列组成,并由可编程的互连资源连接这些逻辑功能块来实现不同的设计。 下面以Xilinx公司的FPGA为例,分析其结构特点。FPGA一般由三种可编程电路和一个用于存放编程数据的静态存储器SRAM组成。这三种可编程电路是:可编程逻辑块(Configurable Logic Block,CLB)、输入/输出模块(I/O Block,IOB)和互连资源(Interco

20、nnect Resource,IR)。FPGA的基本结构如图1.19所示,可编程逻辑块(CLB)是实现逻辑功能的基本单元,它们通常规则地排列成一个阵列,散布于整个芯片;可编程输入/输出模块(IOB)主要完成芯片上的逻辑与外部封装脚的接口,它通常排列在芯片的四周;可编程互连资源(IR)包括各种长度的连线线段和一些可编程连接开关,它们将各个CLB之间或CLB、IOB之间以及IOB之间连接起来,构成特定功能的电路。FPGA的功能由逻辑结构的配置数据决定。工作时,这些配置数据存放在片内的SRAM或熔丝图上。基于SRAM的FPGA器件,在工作前需要从芯片外部加载配置数据,配置数据可以存储在片外的EPRO

21、M或其他存储体上。用户可以控制加载过程,在现场修改器件的逻辑功能,即所谓的现场编程。第三章 单元电路设计 .第一节 顶层模块(top)的设计 VHDL采用的是自顶向下的设计方式,顶层模块由乐曲自动演奏(automusic),音调发生器(tone)和数控分频器(speaker)三个模块组成。图2-1-1即是顶层设计原理图。其中乐曲演奏部分又包括了键盘编码。设置一个自动演奏/键盘输入切换auto,即当auto=0时,选择自动演奏音乐存储器里面的乐曲,auto=1时,选择由键盘输入的信号,再对其进行编码,输出的都是八位二进制数,对应音调发生器的输入。 图2-1-1 顶层设计原理图第二节 自动演奏模块

22、(automusic)的设计 为了实现扩展部分的设计,便需要多加上一个音乐存储模块,该模块的作用是产生8位发声控制输入index,auto为0或1时可以选择自动演奏或者键盘输入,如果auto为0,则而由存储在此模块中的8位二进制数来作为发声控制输入,由此便可自动演奏乐曲。此模块的VHDL语言中包括两个进程,首先是对基准脉冲进行分频得到4Hz的脉冲,作为第二个进程的时钟信号,它的目的是控制每个音阶之间的停顿时间,此处便是1/4=0.25s,第二个进程是音乐的存储,可根据需要编写不同的乐曲。第三节 音调发生器(tone)模块的设计音调发生器的作用是产生获得音阶的分频预置值。当8位发声控制输入ind

23、ex中的某一位为高电平时,则对应某一音阶的数值将以端口tone输出,作为获得该音阶的分频预置值,该值作为数控分频器的输入,来对4MHz的脉冲进行分频,由此得到每个音阶相应的频率,例如输入index=00000010,即对应的按键是2,产生的分频系数便是6809;由code输出对应该音阶简谱的显示数码;由high输出指示音阶高8度的显示,低电平有效。第四节 数控分频模块(speaker)的设计数控分频模块的目的是对基准脉冲分频,得到1,2,3,4,5,6,7七个音符对应频率。该模块的VHDL描述中包含了三个进程。首先对32MHz的基准脉冲进行分频得到8MHz的脉冲,然后按照tone1输入的分频系

24、数对4MHz的脉冲再次分频,得到的便是所需要的频率。而第三个进程的作用是在音调输出时再进行二分频,将脉冲展宽,以使扬声器有足够功率发音。第四章 PS2键盘控制电子琴程序第一节 VHDL硬件描述语言简介PLD的软件已发展得相当完善,利用VHDL硬件描述语言来实现程序的编制,这样硬件的功能描述可以完全在软件上实现。VHDL是用于逻辑设计的硬件描述语言,成为IEEE标准。它作为描述硬件电路的语言,有以下特点:(1) VHDL的宽范围描述能力使它成为高层次设计的核心,将设计人员的工作重心提高到了系统功能的实现与调试,而花较少的精力于物理实现。(2) VHDL可以用简洁明确的代码描述来进行复杂控制逻辑的

25、设计,灵活且方便,而且也便于设计结果的交流、保存和重用。(3)VHDL的设计不依赖于特定的器件,同一个HDL原码可以综合成FPGA或ASIC,方便了工艺的转换。(4)VHDL是一个标准语言,为众多的EDA厂商支持,而且设计出来的电路大多数并行运行,因此移植性好且速度快。采用VHDL语言设计复杂数字电路的方法具有很多优点,其语言的设计技术齐全、方法灵活、支持广泛。它可以支持自顶向下(Top Down)和基于库(Library_Based)的设计方法,而且还支持同步电路、异步电路、FPGA以及其他随机电路的设计,其范围很广,语言的语法比较严格,给阅读和使用都带来了极大的好处。第二节 软件设计本设计

26、采用Xilinx公司的EDA软件系统Foundation Series ISE 4.2i来完成。采用自顶向下的设计方法。图3.2.1为其软件流程图。软件设计采用结构化程序设计方法,功能模块各自独立,实际上在设计中将键盘输入和乐曲存储放在了一个自动演奏模块中,软件设计的核心部分是数控分频器,键盘输入和乐曲储存都是提供给它相应的分频比。对输入的基准时钟进行多次分频,最终输出的就是想得到的音阶的频率。VHDL描述语言和仿真图详见附录。21第五章 结论 本设计利用硬件描述语言VHDL实现了电子琴的自动演奏和键盘输入发音的简易功能,经过编程,综合,仿真,下载,调试,电路板制作,最终做出成品,测试情况良好

27、,能够准确实现音阶的发音功能,可根据需要更改程序从而实现不同乐曲的存储。在设计过程,由于对音乐知识不够熟悉,所以没有实现电子琴那么完美的音乐。在本系统设计调试过程中,软件和硬件都出现了一些小错误。例如在焊接电路时,由于不够细心,把FPG的插槽错焊成排针。在软硬件结合调试时,自动弹奏音乐出现了噪音现象,经过仔细检查所有程序,发现了问题出现在分频模块的编写上,最终把这问题解决了。 第六章 参考文献1 潘松 黄继业.EDA技术与VHDLM.北京:清华大学2004,1 (2):347-292 潘松 黄继业. EDA技术实用教程(第三版)M.北京:科学出版社,2006.3 求是科技编著.PLD/FPGA

28、应用开发技术与工程实践M. 北京:人们邮电出版社,2005.4 黄正谨,徐坚,章小丽等.CPLD系统设计技术入门与应用【M】. 北京:电子工业出版社.2002. 1第七章 附录 与利用微处理器(CPU或MCU)来实现乐曲演奏相比,以纯硬件完成乐曲演奏电路的逻辑要复杂得多,如果不借助于功能强大的EDA工具和硬件描述语言,仅凭传统的数字逻辑技术,即使最简单的演奏电路也难以实现。如何使用EDA工具设计电子系统是人们普遍关心的问题,本设计在美国ALTERA公司MAX + plus的EDA软件平台上,使用层次化设计方法,实现了乐曲发生器的设计。乐曲选取梁祝中化蝶部分,其简谱如图1所示。1、系统结构描述

29、1)本设计完全用VHDL语言实现的主系统由顶层文件SONGER.VHD和三个底层模块组成,有TONETABA.VHD,NOTETABS.VHD和SPCAKERA.VHD2)源代码1.顶层文件1.SONGER.VHD. -顶层文件LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY SONGER IS PORT(CLK12MHZ:IN STD_LOGIC; CLK8HZ:IN STD_LOGIC; CODE1:OUT INTEGER RANGE 0 TO 15; HIGH1:OUT STD_LOGIC; SPKOUT: OUT STD_LOGIC);EN

30、D ENTITY SONGER;ARCHITECTURE one OF SONGER IS COMPONENT NOTETABS PORT(CLK:IN STD_LOGIC; TONEINDEX:OUT INTEGER RANGE 0 TO 15); END COMPONENT; COMPONENT TONETABA PORT( INDEX: IN INTEGER RANGE 0 TO 15; CODE: OUT INTEGER RANGE 0 TO 15; HIGH:OUT STD_LOGIC; TONE:OUT INTEGER RANGE 0 TO 16#7FF#); END COMPON

31、ENT; COMPONENT SPEAKERA PORT( CLK: IN STD_LOGIC; TONE:IN INTEGER RANGE 0 TO 16#7FF#; SPKS: OUT STD_LOGIC); END COMPONENT; SIGNAL TONE:INTEGER RANGE 0 TO 16#7FF#; SIGNAL TONEINDEX:INTEGER RANGE 0 TO 15;BEGINU1:NOTETABS PORT MAP(CLK=CLK8HZ,TONEINDEX=TONEINDEX);U2:TONETABA PORT MAP(INDEX=TONEINDEX,TONE

32、=TONE,CODE=CODE1,HIGH=HIGH1);U3:SPEAKERA PORT MAP(CLK=CLK12MHZ,TONE=TONE,SPKS=SPKOUT);END; 2) 底层文件 1.TONETABA.VHD 用来查询音调频率LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY TONETABA IS PORT(INDEX: IN INTEGER RANGE 0 TO 15; CODE:OUT INTEGER RANGE 0 TO 15; -定义错的输出引脚 HIGH:OUT STD_LOGIC; -定义high输出引脚 TONE:O

33、UT INTEGER RANGE 0 TO 16#7FF#); -定义tone输出引脚END TONETABA;ARCHITECTURE one OF TONETABA ISBEGIN SEARCH:PROCESS(INDEX) BEGIN CASE INDEX IS -此项用来检索音调的频率,高八度和低八度 共十六个音符 WHEN 0 =TONE=2047;CODE=0;HIGHTONE=773;CODE=1;HIGHTONE=912;CODE=2;HIGHTONE =1036;CODE=3;HIGHTONE =1116;CODE=4;HIGHTONE =1197;CODE=5;HIGHTO

34、NE =1290;CODE=6;HIGHTONE =1372;CODE=7;HIGHTONE =1410;CODE=1;HIGHTONE =1480;CODE=2;HIGHTONE =1542;CODE=3;HIGHTONE =1590;CODE=4;HIGHTONE =1622;CODE=5;HIGHTONE =1668;CODE=6;HIGHTONE =1692;CODE=7;HIGHTONE =1728;CODE=1;HIGH NULL; END CASE; END PROCESS;END; 2. SPEAKERA.VHD - 用来分频 LIBRARY IEEE;USE IEEE.STD

35、_LOGIC_1164.ALL;ENTITY SPEAKERA IS PORT(CLK:IN STD_LOGIC; TONE:IN INTEGER RANGE 0 TO 16#7FF#; SPKS:OUT STD_LOGIC);END SPEAKERA;ARCHITECTURE behav OF SPEAKERA IS SIGNAL PRECLK,FULLSPKS:STD_LOGIC; BEGINDIVIDECLK:PROCESS(CLK) VARIABLE COUNT4:INTEGER RANGE 0 TO 15; BEGIN PRECLK11 THEN PRECLK=1;COUNT4:=0

36、; ELSIF CLKEVENT AND CLK=1 THEN COUNT4:=COUNT4+1; END IF; END PROCESS;GENSPKS:PROCESS(PRECLK,TONE) VARIABLE COUNT11:INTEGER RANGE 0 TO 16#7FF#; BEGINIF PRECLKEVENT AND PRECLK=1 THEN IF COUNT11=16#7FF# THEN COUNT11:=TONE;FULLSPKS=1; ELSE COUNT11:=COUNT11+1;FULLSPKS=0; END IF;END IF;END PROCESS;DELAYS

37、PKS:PROCESS(FULLSPKS) VARIABLE COUNT2:STD_LOGIC; BEGIN IF FULLSPKSEVENT AND FULLSPKS=1 THEN COUNT2:=NOT COUNT2; IF COUNT2=1 THEN SPKS=1; ELSE SPKS=0; END IF; END IF;END PROCESS;END behav;3. NOTETAB.VHD -用来存谱 LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY NOTETABS IS PORT( CLK:IN STD_LOGIC; TONEINDE

38、X:OUT INTEGER RANGE 0 TO 15);END NOTETABS;ARCHITECTURE one OF NOTETABS IS SIGNAL COUNTER:INTEGER RANGE 0 TO 138;BEGIN CNT8:PROCESS(CLK)BEGIN IF COUNTER=39 THEN COUNTER=0; ELSIF(CLKEVENT AND CLK=1)THEN COUNTERtoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindexto

39、neindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextonei

40、ndextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneinde

41、xtoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindexto

42、neindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindextoneindexNULL; END CASE; END PROCESS;END;三系统以及各个模块的仿真波形 1.顶层模块songer.vhd 2.底层模块toneba.vhd3.底层模块notetabs.vhd表1 GW48-CK开发系统工作模式:3接口名称类型(输入/输出)引脚号说明Clk12mhz方波1分频系统时钟high高电平25高音显示speakout方波3扬声器输出

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。