DDS信号发生器基本知识

DDS信号发生器基本知识

《DDS信号发生器基本知识》由会员分享,可在线阅读,更多相关《DDS信号发生器基本知识(14页珍藏版)》请在装配图网上搜索。

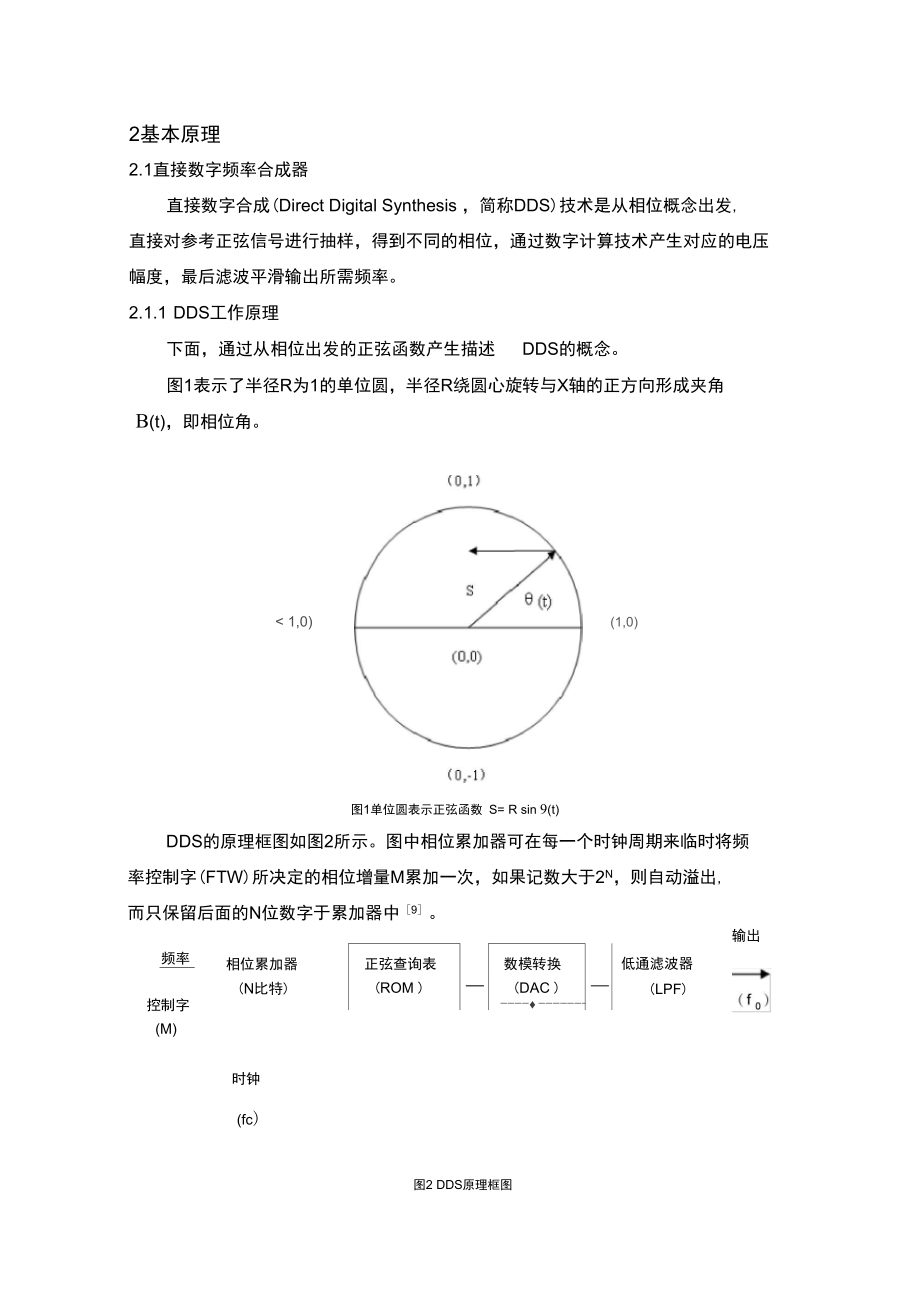

1、* *2基本原理2.1直接数字频率合成器直接数字合成(Direct Digital Synthesis ,简称DDS)技术是从相位概念出发, 直接对参考正弦信号进行抽样,得到不同的相位,通过数字计算技术产生对应的电压 幅度,最后滤波平滑输出所需频率。2.1.1 DDS工作原理下面,通过从相位出发的正弦函数产生描述DDS的概念。图1表示了半径R为1的单位圆,半径R绕圆心旋转与X轴的正方向形成夹角 B(t),即相位角。 1,0)(1,0)图1单位圆表示正弦函数 S= R sin 9(t)DDS的原理框图如图2所示。图中相位累加器可在每一个时钟周期来临时将频 率控制字(FTW)所决定的相位增量M累加

2、一次,如果记数大于2N,则自动溢出, 而只保留后面的N位数字于累加器中9。频率相位累加器(N比特)控制字正弦查询表数模转换(ROM )A(DAC )低通滤波器(LPF)输出(M)时钟(fc)DDS的数学模型可归结为:在每一个时钟周期 Tc内,频率控制字M与N比特 相位累加器累加一次,并同时对2n取模运算,得到的和(以N位二进制数表示)作 为相位值,以二进制代码的形式去查询正弦函数表 ROM,将相位信息转变成相应的 数字量化正弦幅度值,ROM输出的数字正弦波序列再经数模转换器转变为阶梯模拟 信号,最后通过低通滤波器平滑后得到一个纯净的正弦模拟信号。由于ROM表的规模有限,相位累加器一般仅取高位作

3、为寻址地址送入正弦查询 表获得波形幅度值。正弦查询表中以二进制数形式存入用系统时钟对正弦信号进行采 样所得的样值点,可见只需改变查询表内容就可实现不同的波形输出。2.1.2 DDS的结构DDS的基本结构包括相位累加器、正弦查询表(ROM )、数模转换器(DAC) 和低通滤波器(LPF),其中从频率控制字到波形查询表实现由数字频率值输入生成 相应频率的数字波形,其工作过程为:确定频率控制字M ;在时钟脉冲f c的控制下,该频率控制字累加至相位累加器生成实时数字相位值;将相位值寻址ROM转换成正弦表中相应的数字幅码。模块DAC实现将数字幅度值高速且线性地转变为模拟幅度值,DDS产生的混叠干扰由DA

4、C之后的低通滤波器滤除7。相位累加器相位累加器是DDS最基本的组成部分,用于实现相位的累加并存储其累加结果。 若当前相位累加器的值为工n,经过一个时钟周期后变为工n 1,则满足艺n 1 =乙)+M各为一等差数列,不难得出:工n= nM+艺 其中艺为相位累加器的初始相位值。正弦查询表(ROM )DDS查询表所存储的数据是每一个相位所对应的二进制数字正弦幅值,在每一 个时钟周期内,相位累加器输出序列的高 m位对其进行寻址,最后的输出为该相位 相对应的二进制正弦幅值序列。数模转换器(DAC)数模转换器的作用是将数字形式的波形幅值转换成所要求合成频率的模拟形式信号。DAC有电压和电流输出两种,其输出的

5、信号并不能真正连续可变,而是以其 绝对分辨率为最小单位的,所以其输出实际上是一个阶梯模拟信号。2.1.3 DDS的优点正由于DDS采用全数字技术,从概念到结构都有很大的突破,所以它具有其他 频率合成所无法比拟的优越性。 频率分辨率高。若时钟频率不变,DDS频率分辨率仅由相位累加器位数来决定,也就是理论上的值越大,就可以得到足够高的频率分辨率。目前,大多数DDS的分辨率在1Hz数量级,许多都小于1mHz甚至更小,这是其他频率合成器很难做 到的。 工作频带较宽。根据 Nyquist定律,只要输出信号的最高频率分辨率分量小 于或等于Jk/2就可以实现。而实际当中由于受到低通滤波器设计以及杂散分布的影

6、 响限制,仅能做到40% f clk左右。 超高速频率转换时间。DDS是一个开环系统,无任何反馈环节,这种结构使 得DDS的频率转换时间极短。DDS的频率转换时间可达到纳秒数量级, 比使用其它 的频率合成方法都要小几个数量级。 相位变化连续。改变DDS输出频率,实际上改变的是每一个时钟周期的相位增量,相位函数的曲线是连续的,只是在改变频率的瞬间其频率发生了突变,因而保持了信号相位的连续性10 o 具有任意输出波形的能力。只要ROM中所存的幅值满足并且严格遵守Nyquist定律,即可得到输出波形。例如三角波、正弦波和矩形波。 具有调制能力。由于DDS是相位控制系统,这样也就有利于各种调制功能。

7、2.2波形产生分析频率 控制 字图3正弦波产生框图相位累加器为32位累加器,输出为0(2 32 -1 ),作为正弦查询表的地址输入 端。正弦表中存放一个周期的正弦波内的232个点的数据,输出fo为一正弦波,其频率由频率控制字进行调节,输出频率:f out =f elk /2 N FTW最小频率分辨率:minelk 12其中N为相位累加器的位数,FTW为频率步进控制字,feik为时钟频率,输出 信号频率主要取决于频率控制字 FTW。当FTW增大时,仁址可以不断增加,综合考虑Nyquist采样定理,最高输出频率应小于fut/2。根据实验所得,实际工作频率应小于f clk /311由于本论文只要求设

8、计出最高为 1MHz的信号,根据DA及FPAG的速度,可 以很容易地满足设计需要。本例中选用 32M的CLK时钟,在输出最高1MHz的信 号时,波形在一个周期内仍有 32个点,能够完整描述出波形。f min =f clk /2 N =32 X106/2 32 =0.00745058所以可以实现1Hz步进,当输出1Hz时,频率控制字FTW=1/f min =134.217728。由于频率控制字是由NIOS系统提供的,考虑到浮点运算所占资源太多,所以把浮点 运算改为定点运算。则当输出其他任意频率 fout时Nios内部算法为:FTW=f out X134+f out X21/100+f out X

9、77/10000+f out X28/10000003总体设计近年来现场可编程门阵列(FPGA)得到了迅速的发展和广泛的应用,其资源容 量、工作频率以及集成度都得到了极大的提高,使得利用FPGA实现某些专用数字集 成电路得到了大家的关注,而基于 FPGA实现的DDS信号发生器则更有发展前途和 研究的意义12。3.1设计的要求根据我们所学的知识储备,对本次信号发生器的设计提出了以下要求: 信号发生器能产生正弦波、方波和三角波三种周期性波形; 输出信号频率在10Hz1MHz范围内可调,输出信号频率稳定度优于10 3 ; 在1k负载条件下,输出正弦波信号的电压峰-峰值Vopp在05V范围内可 调;

10、输出信号波形无明显失真;3.2方案比较及选择方案一:采用模拟锁相环实现。模拟锁相环技术是一项比较成熟的技术。应用模拟锁相环,可将基准频率倍频, 或分频得到所需的频率,且调节精度可以做到相当高、稳定性也比较好。但模拟锁相 环模拟电路复杂,不易调节,成本较高,并且频率调节不便且调节范围小,输出波形 的毛刺较多,得不到满意的效果13。方案二:采用直接数字频率合成,用单片机作为核心控制部件,能达到较高的要 求,实现各种波形输出,但受限于运算位数和运算速度, 产生的波形往往达不到满意 效果,并且频率可调范围小,很难得到较高频率,并且单片机的引脚少,存储容量少, 这就导致了外围电路复杂。方案三:采用直接数

11、字频率合成,用FPGA器件作为核心控制部件,精度高稳定 性好,得到波形平滑,特别是由于FPGA的高速度,能实现较高频率的波形。 控制上 更方便,可得到较宽频率范围的波形输出,步进小,外围电路简单易实现。因此采用4 DDS信号发生器的实现4.1硬件电路的制作根据设计要求,本论文选用 EDA比赛套件中:EDA-SOPC核心板、LCD 1602、RS232&PS2及DDS_BOARD四个模块。电源采用5V直流电源及土 5V电源供电。各模块连接如图4所示:LCD 接口DA及10接口RS232&PS2模块PS/2小键盘RS&PS2接口FPGASDRAM电源图4各模块连接示意图各模块功能如下:一、由EDA

12、-SOPC核心板提供的FPGA及SDRAM为本系统的核心器件。主要 完成功能:1、采用DDS技术基于FPGA设计信号发生模块,产生要求的信号序列;2、利用SDRAM配合FPGA构成片上系统,建立NIOS控制系统,完成任务调 度及人机交互控制。核心板分别通过相关接口与其它三个功能模块相连。二、RS232&PS2 模块通过8-PIN 双排线与核心板的 PORT2CP接口相连。将PS2接口的数字小键盘连接到该模块的 PS/2接口上,实现按键输入功能。三、LCD1602模块通过16-PIN 双排线与核心板的 PORT12-LCD接口相连。将液晶LCD1602连接到该模块的液晶接口上,实现人机交互的显示

13、功能14。四、DDS模块分别通过14-PIN双排线与核心板的PORT14-DA接口相连及通 过16-PIN双排线与核心板的PORT16-IO接口相连。该模块实现两路 D/A,其中一 路产生信号,另一路实现信号幅度的调整,模块的 BNC接头直接输出信号。4.2硬件模块的介绍4.2.1 EDA-SOPC 核心板EDA-SOPC核心板主芯片使用了 Cyclone II系列芯片EP2C8Q208C8,具有8256 个逻辑单元(LE),可以满足更多、更大的系统需求;18个18*18位乘法器,可以实 现数字信号处理(DSP功能);2个增强型锁相环(PLLs),能够提供先进的时钟管理 能力,如频率合成、可编

14、程移相、外部时钟输出、可编程占空比、锁定检测、可编程 带宽、输入时钟扩频和支持高速差分输入输出时钟信号;具有 138个用户I/O,能够 满足大多数系统需求。使用了 1个16位SDRAM内存,组建成一个片外8Mbytes系统 内存电路;配备了 4Mbytes的Flash,用来保存用户数据、系统工程等;使用 EPCS4 作为配置芯片;丰富的外围设备,供用户进行高级设计12;选用大功率电源芯片来保障系统稳定工作。在此硬件平台上 SOPC系统频率达到110MHz,但建议使用的系 统频率为85MHz,这样会使系统能更稳定的运行。4.2.2 LCD1602 模块LCD1602模块是由液晶LCD1602为核

15、心,提供16 X2字符显示的电路模块。该模 块可通过16针接口连接到EDA-SOPC核心板上,使用方便。该模块电路指底板电路, 主要提供EDA-SOPC核心板与LCD1602液晶接口及液晶所需的负压调节及背光控制电路。该接口采用16针接口与核心板P0RT12-LCD接口相连。具体如下:VLM_5VVLM_5.3VI 1 MRLCM_D2 LCMXLLM_IJb LCM_EN JLM 時LTM_COM1345678910111213141516IQV_D1_ im LCM_1 巧 LCV_1J?I.CMRW I .CM K图5与EDA-SOPC核心板接口RS232&PS2模块由RS232电平转换

16、电路和PS2键盘接口电路两部分组成,用于讥)VDDS_1AVtJDS 5VVMS 3JV卩草键盘扩展等功能。.IN CSW RL r .-: (TwiFCSW R7 入端有两组? DA数据,完成RS232串口通信该模块可通过8针接口I , Hi4.2.4 DDS_BOARD噌2接口通信,可实现与计算机串口 口连接到 EDA顶sopc核心板上。16 1通信、10模块输 一路数据经DA转换后成作为信号输出,另一路数据经DA转换后成作为输出信号的幅 度调节。经合EDA SOPC核心板的DDS技术可实现任意波形,一定频率、一定幅度 范围的信号输出。该模块可分别通过14针和16针两条数据线连接到EDA

17、SOPCDDS_BOARD模块包括DA转换、驱动等电路组成。该423 RS232&PS2 模块核心板上与EDA-SOPC核心板接口,该接口采用 14针和16针两条数据线分别与核心板PORT10-DA和PORT12-IO接口相连。具体如下:图6与EDA-SOPC核心板接口5软件设计5.1设计的原理图信号发生器的原理图如附录所示,图中涉及到相位累加器、正弦波查询、波形输出等模块的设计,并由各个模块之间的连接构成满足产生正弦波的信号发生器。通过选择波形输出模块的波形选择端sei就可实现方波和三角波的产生,改变频率控制字 的大小就可实现调频,在时钟频率一定时,相位累加器的位数越大,频率调节就越精 细2

18、。相位累加器的输出端与波形输出模块的 10位地址输入端(addr9.O)相连, 正弦波查询表的输出端与波形输出模块的 10位数据输入端(qin9.0)相连。波形 输出模块的输出端(qout9.0)为正弦波的离散信号。5.2软件各模块设计5.2.1相位累加器设计xia ngleidi n31.0clkdout9.0in st3图7相位累加器模块示意图相位累加器如图7所示,32位的din31.0输入为相位累加器频率控制字输入 端,改变频率控制字,即可改变输出频率。 clk为时钟输入,本例中选用 32MHz dout9.0接正弦查询表的地址输入端,产生 10位的地址查询码。5.2.2正弦波查询表图8

19、正弦波查询模块示意图正弦查询表如图8所示,是由一个ROM模块构成,输入为10位地址,在时钟 的作用下,输出存储的正弦数据。本模块采用QuartusII软件定制的LPM_ROM模 块。正弦数据由Matlab生成,并以mif的文件格式存储后加载到 ROM模块中。文 件为 sin 10bit.mif。5.2.3波形输出模块图9波形输岀模块示意图波形输出模块如图9所示,10位地址输入端与相位累加器模块相连,10位数据 输入端与正弦查询表的ROM输出相连。sei为波形选择端。当选择端为0时,在时钟的作用下,该模块输出正弦查询表的ROM的数据;当选择端为1时,在时钟的作用下,输入数值小于 512时输出为0

20、,大于或等 于512时输出为最大值(1023),即输出占空比为50 %的方波;当选择端为2时,在时钟的作用下,输入数值小于 512时输出地址数据乘2, 大于或等于512时输出地址数据取反乘2,即输出三角波。当选择端为3时,在时钟的作用下,输出即等于输入的地址数据,即输出锯齿波。 由于DDS模块采用的是8位DA,因此输出端仅接qout的前8位。5.2.4 NIOS 模块本模块提供主控 CPU部分,由Quartus II软件定制,需加入 SDRAM、LCD、 RS232等控制器。对DDS部分的控制由PIO 口完成,均为输出口,包括频率控制字 输出口、波形选择输出口、幅度控制输出口。5.2.5 PL

21、L 模块本设计需要两个PLL模块,一个用于产生NIOS及SDRAM所需的时钟,另一 个用于DDS时钟,采用32MHz。锁相环(PLL: Phase-locked loops )是一种利 用反馈(Feedback )控制原理实现的频率及相位的同步技术,其作用是将电路输出 的时钟与其外部的参考时钟保持同步12。当参考时钟的频率或相位发生改变时,锁 相环会检测到这种变化,并且通过其内部的反馈系统来调节输出频率,直到两者重新同步,这种同步又称为“锁相” (Phase-locked ) 15。6仿真测试结果1、第一次sel的值设为0,其输出的波形是正弦波,从图10中可以看出,输出 的数据的变化规律是正弦

22、规律。际Mm it 4 B3 k汕100 hLHq 5壯:】注呼20上露沖3C曲gU料U. 325 皿图10正弦波的波形JVJLWLRTOTLRWnRmr二眶謔駆駆因据画卫回區巨回區匡匪;2、第二次sei的值设为1,其输出的波形是方波,从图11中仿真的结果可以看 出,输出的波形变化规律是按方波规律周期性变化的。14.8Q u心El导皿吓頤321.60 唧坠砂5那FdkJQlumniniinHiinMiiHHniHmnnnininniiuniiiin:HOD:DCJFFf0JFFEHEltHL/111 1lL1a i iiiiiiiiiiaiiii图11方波的波形3、第三次sei的值设为2,输出

23、为三角波,其仿真波形如下图12所示,输出波 形线性增大到最大后,再线性减小。VneYilii it S4 us 49】.讯匚50L38 m511 rrs521.8 us532J4 眄 542JB kr i |- | iM 63 otelk30BouwiRLrimwrjvTAmnnnnin11 13I(H倔)磁璽懑甌烦观須麗廳近駆阴 阴錮rsstiEl国id9 i图12三角波的波形7结论本论文是基于FPGA的DDS信号发生器。通过方案论证,采用直接数字频率合 成技术,经过硬件电路设计,将 DDS技术与FPGA相结合,输出正弦波、三角波和 方波。实现了波形的平滑、无毛刺,具有较高的频率分辨率,可实现快速的频率切换, 并且在改变时能够保持相位的连续、很容易实现频率、相位和幅度的数控调制16 o近年来FPGA得到了迅速的发展和广泛的应用,其资源容量、工作频率以及集成 度都得到了极大的提高,使得利用FPGA实现某些专用数字集成电路得到了大家的关 注,而基于FPGA实现的直接数字频率合成器则更具其优点, 有着灵活的接口和控制 方式、较短的转换时间、较宽的带宽、以及相位连续变化和频率分辨率较高等优点, 在电子、通信等领域,有着广泛的应用。附录

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。