EDA课后问题详解(适用于朱正伟《EDA技术及应用》)

EDA课后问题详解(适用于朱正伟《EDA技术及应用》)

《EDA课后问题详解(适用于朱正伟《EDA技术及应用》)》由会员分享,可在线阅读,更多相关《EDA课后问题详解(适用于朱正伟《EDA技术及应用》)(25页珍藏版)》请在装配图网上搜索。

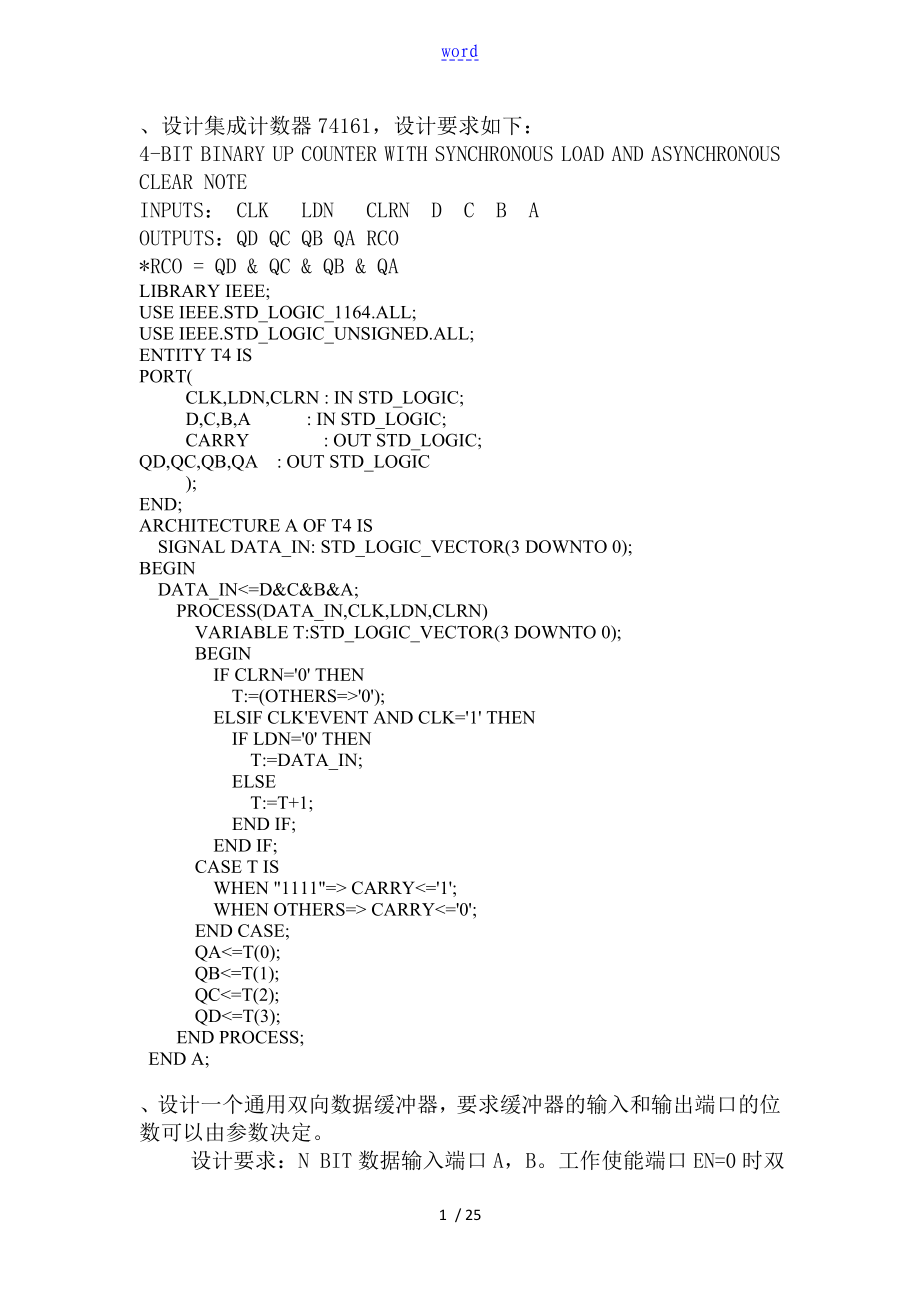

1、word、设计集成计数器74161,设计要求如下:4-BIT BINARY UP COUNTER WITH SYNCHRONOUS LOAD AND ASYNCHRONOUS CLEAR NOTEINPUTS:CLKLDNCLRNDCBAOUTPUTS:QDQCQBQARCO*RCO = QD & QC & QB & QA LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY T4 ISPORT( CLK,LDN,CLRN : IN STD_LOGIC; D,C,B,A : IN STD_

2、LOGIC; CARRY : OUT STD_LOGIC;QD,QC,QB,QA : OUT STD_LOGIC );END;ARCHITECTURE A OF T4 IS SIGNAL DATA_IN: STD_LOGIC_VECTOR(3 DOWNTO 0);BEGIN DATA_IN0); ELSIF CLKEVENT AND CLK=1 THEN IF LDN=0 THEN T:=DATA_IN; ELSE T:=T+1; END IF; END IF; CASE T IS WHEN 1111= CARRY CARRY=0; END CASE; QA=T(0); QB=T(1); QC

3、=T(2); QD=T(3); END PROCESS; END A;、设计一个通用双向数据缓冲器,要求缓冲器的输入和输出端口的位数可以由参数决定。设计要求:N BIT数据输入端口A,B。工作使能端口EN=0时双向总线缓冲器选通,DIR=1,如此A=B;反之B=A。LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY BIDIR ISGENERIC(N:INTEGER:=8); PORT(A,B :INOUTSTD_LOGIC_VECTOR(N-1 DOWNTO 0); EN,DIR:INSTD_LOGIC);END;ARCHITECTURE A OF

4、 BIDIR ISBEGIN PROCESS(EN,DIR) BEGIN IF EN=0 THEN AZ); BZ); ELSE IF DIR=1 THEN B=A; ELSE A=B; END IF; END IF;END PROCESS;END A;、用VHDL语言编程实现十进制计数器,要求该计数器具有异步复位、同步预置功能。LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY T_10_2 ISPORT( CLK,CLR : IN STD_LOGIC; COUNT : OUT STD_LOGIC );END;ARCHITECTURE A OF T

5、_10_2 IS SIGNAL T_10 : INTEGERRANGE 0 TO 10;BEGIN PROCESS(CLK,CLR) BEGIN IF CLR=1 THEN T_10=0; ELSIF CLKEVENT AND CLK=1 THEN T_10=T_10+1; IF T_10=9 THEN T_10=0; COUNT=1; ELSE COUNT=0; END IF; END IF; END PROCESS;END A;、设计实现一位全减器。行为描述: F_SUB4LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC

6、_UNSIGNED.ALL;ENTITY F_SUB4 ISPORT( A,B,CIN : IN STD_LOGIC; DIFF,COUT : OUT STD_LOGIC );END;ARCHITECTURE A OF F_SUB4 ISBEGIN DIFF=A XOR B XOR CIN; COUT=(NOT A AND B) OR (NOT A AND CIN) OR (B AND CIN);END A;数据流描述F_SUB1LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY F_S

7、UB1 ISPORT( A,B :IN STD_LOGIC; CIN :IN STD_LOGIC; DIFF,COUT : OUT STD_LOGIC );END;ARCHITECTURE A OF F_SUB1 ISSIGNAL S :STD_LOGIC_VECTOR(2 DOWNTO 0);BEGIN S DIFF=0;COUT DIFF=1;COUT DIFF=1;COUT DIFF=0;COUT DIFF=1;COUT DIFF=0;COUT DIFF=0;COUT DIFF=1;COUT DIFF=X;COUT=X; END CASE; END PROCESS;END A;数据流描述

8、F_SUB2LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY F_SUB2 ISPORT( A,B,CIN : IN STD_LOGIC; DIFF,COUT : OUT STD_LOGIC );END;ARCHITECTURE A OF F_SUB2 ISSIGNAL S :STD_LOGIC_VECTOR(2 DOWNTO 0);SIGNAL C :STD_LOGIC_VECTOR(1 DOWNTO 0);BEGIN S=CIN&A&B; DIFF=C(1); COUT=C(0);

9、 C=00 WHEN S=000 ELSE 11 WHEN S=001 ELSE 10 WHEN S=010 ELSE 00 WHEN S=011 ELSE 11 WHEN S=100 ELSE 01 WHEN S=101 ELSE 00 WHEN S=110 ELSE 11 ;END A;数据流描述F_SUB3LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY F_SUB3 ISPORT( A,B,CIN : IN STD_LOGIC; DIFF,COUT : OUT STD_LOGI

10、C );END;ARCHITECTURE A OF F_SUB3 ISSIGNAL S :STD_LOGIC_VECTOR(2 DOWNTO 0);SIGNAL C :STD_LOGIC_VECTOR(1 DOWNTO 0);BEGIN S=CIN&A&B; DIFF=C(1); COUT=C(0); WITH S SELECT C=00 WHEN 000, 11 WHEN 001, 10 WHEN 010, 00 WHEN 011, 11 WHEN 100, 01 WHEN 101, 00 WHEN 110, 11 WHEN OTHERS;END A;、阅读教材P181页,例5-55并回答如

11、下问题:1、该程序的功能是什么?2、请写出该程序所有端口的功能描述。、试描述一个十进制BCD码编码器,输出使能为低电平有效。LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY BIN_BCD ISPORT( BIN : IN INTEGERRANGE 0 TO 20; -ENA : IN STD_LOGIC; BCD_OUT : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) );END;ARCHITECTURE A OF BIN_BCD ISBEGINBINARY_BCD : BLOCKBEGINBCD_OUT =00000000

12、 WHEN BIN = 0 ELSE00000001 WHEN BIN = 1 ELSE00000010 WHEN BIN = 2 ELSE00000011 WHEN BIN = 3 ELSE00000100 WHEN BIN = 4 ELSE00000101 WHEN BIN = 5 ELSE00000110 WHEN BIN = 6 ELSE00000111 WHEN BIN = 7 ELSE00001000 WHEN BIN = 8 ELSE00001001 WHEN BIN = 9 ELSE00010000 WHEN BIN = 10 ELSE00010001 WHEN BIN = 1

13、1 ELSE00010010 WHEN BIN = 12 ELSE00010011 WHEN BIN = 13 ELSE00010100 WHEN BIN = 14 ELSE00010101 WHEN BIN = 15 ELSE00010110 WHEN BIN = 16 ELSE00010111 WHEN BIN = 17 ELSE00011000 WHEN BIN = 18 ELSE00011001 WHEN BIN = 19 ELSE00100000 WHEN BIN = 20 ELSE 00000000;END BLOCK;END A;、读教材P151页,例5-32的程序,并回答以下问

14、题:1请画出该程序所描述的电路结构图,要求标清楚每一个端口以与内部信号。串入/串出移位存放器、用VHDL语言设计一个能够实现任意整数进制的计数器。LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;-*ENTITY FREQDV_N IS GENERIC(N:INTEGER:=6); PORT( CLK :IN STD_LOGIC; CLK_DIV : OUT STD_LOGIC );END;ARCHITECTURE A OF FREQDV_N IS SIGNAL T : INTEGERRANGE 0 TO N;BEGIN PROCESS(CLK) BEGIN I

15、F RISING_EDGE(CLK) THEN IF T=0 THEN T=N-1; CLK_DIV=1; ELSE CLK_DIV=0; T=T-1; END IF; END IF; END PROCESS;END A;、设计一个序列信号发生器,要求能够循环输出序列“01101001。LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY RS_1 ISPORT( CP,S,R : IN STD_LOGIC; Q,NQ : OUT STD_LOGIC );END;ARCHITECTURE

16、A OF RS_1 ISSIGNAL S1,R1,Q1,NQ1:STD_LOGIC;BEGIN S1=S NAND CP; R1=R NAND CP; Q1=S1 NAND NQ1; NQ1=R1 NAND Q1; Q=Q1; NQ=NQ1;END A;、设计一个带复位端、置位端、CP下降沿触发的JK触发器。LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY JKFF ISPORT( J,K,RST,CLR : IN BIT; CLK : IN BIT; Q,NQ : OUT BIT )

17、;END;ARCHITECTURE A OF JKFF ISSIGNAL Q_S,NQ_S : BIT;BEGIN PROCESS(J,K,RST,CLR,CLK) BEGIN IF RST=1 THEN Q_S=1; NQ_S=0; ELSIF CLKEVENT AND CLK=0 THEN IF CLR=1 THEN Q_S=0; NQ_S=1; ELSIF J=0 AND K=1 THEN Q_S=0; NQ_S=1; ELSIF J=1 AND K=0 THEN Q_S=1; NQ_S=0; ELSIF J=1 AND K=1 THEN Q_S=NOT Q_S; NQ_S=NOT NQ

18、_S; END IF; ELSE NULL; END IF; Q=Q_S; NQ=NQ_S;END PROCESS;END A;、用VHDL语句描述一个三态输出的双4选一的数据选择器,其地址信号共用,且各有一个低电平有效的使能端。LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY DUAL_MUX_41 ISPORT( A,B,C,D : IN STD_LOGIC; ENA_N,ENB_N : IN STD_LOGIC; S : IN STD_LOGIC_VECTOR(1 DOWNTO 0); OUTA,OUTB : OUT STD_LOGIC );

19、END;ARCHITECTURE A OF DUAL_MUX_41 IS SIGNAL P,Q : STD_LOGIC_VECTOR(2 DOWNTO 0);BEGIN P=ENA_N & S; Q=ENB_N & S; WITH P SELECT OUTA=A WHEN 000, B WHEN 001, C WHEN 010, D WHEN 011, Z WHEN OTHERS; WITH Q SELECT OUTB=A WHEN 000, B WHEN 001, C WHEN 010, D WHEN 011, Z WHEN OTHERS; END A;、用并行信号赋值语句实现38译码器。L

20、IBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY DECODER38 IS PORT(A,B,C,G1,G1A,A2B:IN STD_LOGIC; Q:OUT STD_LOGIC_VECTOR(7 DOWNTO 0); END DECODER38; ARCHITECTURE BEHAVE38 OF DECODER38 IS SIGNAL INDA: STD_LOGIC_VECTOR(2 DOWNTO 0); BEGIN INDAQQQQQQQQQ=XXXXXXXX; END CASE; ELSE Q=11111111; END IF; END P

21、ROCESS;END BEHAVE38;、用并行信号赋值语句实现8选一数据选择器,要求有工作使能端。LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY MUX8 IS PORT(D0,D1,D2,D3,D4,D5,D6,D7:IN STD_LOGIC_VECTOR(7 DOWNTO 0); S0,S1,S2:IN STD_LOGIC; Q:OUT STD_LOGIC_VECTOR(7 DOWNTO 0); END MUX8;ARCHITECTURE BEHAVE OF MUX8 IS SIGNAL S: STD_LOGIC_VECTOR(2 DO

22、WNTO 0);BEGIN S =S2&S1&S0; WITH S SECLECT D =D0 WHEN 000, D1 WHEN 001, D2 WHEN 010, D3 WHEN 011, D4 WHEN 100, D5 WHEN 101, D6 WHEN 110, D7 WHEN 111,XWHEN OTHERS;END BEHAVE;、用VHDL语言设计实现输出占空比为50%的1000分频器。LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY DIV_1000 ISPORT( CLK ,CLR: IN STD_LOGIC; DIV : OUT

23、 STD_LOGIC );END;ARCHITECTURE A OF DIV_1000 ISSIGNAL Q : STD_LOGIC;BEGIN DIV=Q; PROCESS(CLK,CLR) VARIABLE T : INTEGERRANGE 0 TO 499; BEGIN IF CLR=1 THEN T:=0; Q=0; ELSIF RISING_EDGE(CLK) THEN IF T=499 THEN T:=0; Q=NOT Q; ELSE T:=T+1; END IF; END IF; END PROCESS;END A;、设计一个一位全减器。LIBRARY IEEE;USE IEEE

24、.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY F_SUB3 ISPORT( A,B,CIN : IN STD_LOGIC; DIFF,COUT : OUT STD_LOGIC );END;ARCHITECTURE A OF F_SUB3 ISSIGNAL S :STD_LOGIC_VECTOR(2 DOWNTO 0);SIGNAL C :STD_LOGIC_VECTOR(1 DOWNTO 0);BEGIN S=CIN&A&B; DIFF=C(1); COUT=C(0); WITH S SELECT C=00 WHEN 00

25、0, 11 WHEN 001, 10 WHEN 010, 00 WHEN 011, 11 WHEN 100, 01 WHEN 101, 00 WHEN 110, 11 WHEN OTHERS;END A;、用元件例化语句描述一个四位的全减器。LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY F_SUB4_1 ISPORT( A,B : IN STD_LOGIC_VECTOR(3 DOWNTO 0); CIN : IN STD_LOGIC; DIFF: OUT STD_LOGIC_VEC

26、TOR(3 DOWNTO 0); COUT: OUT STD_LOGIC );END;ARCHITECTURE A OF F_SUB4_1 ISPONENT F_SUB1 IS PORT( A,B,CIN : IN STD_LOGIC; DIFF,COUT : OUT STD_LOGIC ); END PONENT;SIGNAL C :STD_LOGIC_VECTOR(3 DOWNTO 0);BEGIN U1: F_SUB1 PORT MAP(A(0),B(0),CIN,DIFF(0),C(0); U2: F_SUB1 PORT MAP(A(1),B(1),C(0),DIFF(1),C(1);

27、 U3: F_SUB1 PORT MAP(A(2),B(2),C(1),DIFF(2),C(2); U4: F_SUB1 PORT MAP(A(3),B(3),C(2),DIFF(3),C(3); COUT=C(3);END A;、利用生成语句描述一个由N个一位全减器构成的N位减法器,N的默认值为4。LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY F_SUB4_2 ISGENERIC (N : INTEGER := 4);PORT( A,B : IN STD_LOGIC_VECTOR

28、(N-1 DOWNTO 0); CIN : IN STD_LOGIC; DIFF: OUT STD_LOGIC_VECTOR(N-1 DOWNTO 0); COUT: OUT STD_LOGIC );END;ARCHITECTURE A OF F_SUB4_2 ISPONENT F_SUB1 IS PORT( A,B,CIN : IN STD_LOGIC; DIFF,COUT : OUT STD_LOGIC ); END PONENT;SIGNAL C :STD_LOGIC_VECTOR(N DOWNTO 0);BEGIN C(0)=CIN; N1: FOR I IN 0 TO N-1 GEN

29、ERATE U1: F_SUB1 PORT MAP(A(I),B(I),C(I),DIFF(I),C(I+1); END GENERATE; COUT=C(N);END A;、设计一个模为60、具有异步复位、同步置数功能的8421码计数器。LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY COUNT_60 ISPORT( CLK ,CLR,PST: IN STD_LOGIC; A : IN STD_LOGIC_VECTOR(5 DOWNTO 0); Q : OUT STD_LOGIC_

30、VECTOR(5 DOWNTO 0); CO: OUT STD_LOGIC );END;ARCHITECTURE A OF COUNT_60 ISSIGNAL T: STD_LOGIC_VECTOR(5 DOWNTO 0);BEGIN Q=T; PROCESS(CLK,CLR,PST,A) BEGIN IF CLR=1 THEN T0); CO=0; ELSIF RISING_EDGE(CLK) THEN IF PST=1 THEN T=A; ELSIF T=59 THEN T0); CO=1; ELSE T=T+1; CO6,M=10) PORT MAP(A=TRIGGER_IN,CLK=C

31、LK,Y=MONO_OUT);END A;10.2、设计实现一个83优先编码器。LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY MONO_TRIGGER IS -非可重复触发单稳态触发器GENERIC(N:INTEGER:=5; -单稳态定时参数 M:INTEGER:=10); -定义定时参数取值X围PORT( A,CLK: IN STD_LOGIC; Y : OUT STD_LOGIC );END;ARCHITECTURE A OF MONO_TRIGGER ISTYPESTATE

32、 IS(ST0,ST1,ST2);SIGNAL CURRENT_STATE,NEXT_STATE : STATE;SIGNAL Q:STD_LOGIC;BEGIN REG:PROCESS(A,CLK) BEGIN IF CLKEVENT AND CLK=1 THEN CURRENT_STATE IF A=0 THEN NEXT_STATE=ST0; Y=0; ELSE NEXT_STATE IF Q=1 THEN NEXT_STATE=ST2; Y=0; ELSE NEXT_STATE=ST1; Y IF A=1 THEN NEXT_STATE=ST2; Y=0; ELSE NEXT_STAT

33、E=ST0; Y NEXT_STATE=ST0; END CASE; END PROCESS; AUX_COUNT:PROCESS(CURRENT_STATE,CLK) VARIABLE COUNT : INTEGERRANGE 0 TO M; BEGIN IF CLKEVENT AND CLK=1 THEN IF CURRENT_STATE/=ST1 THEN COUNT:=N; ELSE COUNT:=COUNT-1; END IF; END IF; IF COUNT=0 THEN Q=1; ELSE Q=0; END IF; END PROCESS;END A;10-19LIBRARY

34、IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY CODE_PAN ISPORT( X,RST,CLK : IN STD_LOGIC; Y : OUT STD_LOGIC );END;ARCHITECTURE A OF CODE_PAN ISSIGNAL Q :STD_LOGIC_VECTOR(6 DOWNTO 0);BEGIN PROCESS(CLK,X,RST) BEGIN IF RST=1 THEN Q0); ELSIF CLKEVENT AND CLK=1 THEN Q(0)=X; Q(1)=Q(0); Q(2)=Q(1); Q(3)=Q(2); Q(4)

35、=Q(3); Q(5)=Q(4); Q(6)=Q(5); END IF; END PROCESS; WITH Q SELECT Y=1 WHEN 1110010, 0 WHEN OTHERS;END A; 8-3优先编码器(when-else实现):LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY CODER ISPORE( D:IN STD_LOGIC_VECTOR(7 DOWNTO 0); OUTPUT:OUT STD_LOGIC_VECTOR(2 DOWNTO 0) );END CODER;ARCHITECTURE ART1 ISBEGIN

36、OUTPUT=000 WHEN D(7)=0 ELSE 001 WHEN D(6)=0 ELSE 010 WHEN D(5)=0 ELSE 011 WHEN D(4)=0 ELSE 100 WHEN D(3)=0 ELSE 101 WHEN D(2)=0 ELSE 110 WHEN D(1)=0 ELSE 111;END ART1;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY MAX4_1 ISPORT(A,B,C,D,S1,S2 : IN STD_LOGIC; Y : OUT STD_LOGIC);END ENTITY MAX4_1;ARCH

37、ITECTURE HF1 OF MAX4_1 ISSIGNAL SS : STD_LOGIC_VECTOR (0 TO 1);BEGINSS Y Y Y Y NULL;END CASE;END PROCESS;END HF1;3.6设计一个7人表决电路,参加表决者7人,同意为1,不同意为0,同意者过半如此表决通过,绿指示灯亮;表决不通过如此红指示灯亮。设计思路:根据7人表决电路设计要求,7人中至少有4个通过才可以表决通过,故可以在程序中设置一个变量TEMP,使其在表决电路中遇1如此加1,遇0如此加0设计中1表示通过,0表示不通过。当TEMP=4时,表示表决通过,当TEMPOUTPUTOUTPU

38、T=1; END CASE ; END PROCESS; END BEHAVE;4-7给出1位全减器的VHDL描述,要求:首先设计1位半减器,然后用例化语句将它们连接起来。设X为被减数,Y为减数,DIFF是输出差(DIFF=X-Y),SUB_OUT是借位输出(SUB_OUT=1,XY),SUB_IN是借位输入。(1.1):实现1位半减器H_SUBER(DIFF=X-Y;S_OUT=1,XY)LIBRARY IEEE; -半减器描述(1):布尔方程描述方法 USE IEEE.STD_LOGIC_1164.ALL; ENTITY H_SUBER IS PORT( X,Y: IN STD_LOGIC

39、; DIFF,S_OUT: OUT STD_LOGIC); END ENTITY H_SUBER; ARCHITECTURE HS1 OF H_SUBER IS BEGIN DIFF = X XOR (NOT Y); S_OUT XIN,Y=YIN, DIFF=A, S_OUT=B); U2:H_SUBERPORT MAP(X=A, Y=SUB_IN, DIFF=DIFF_OUT,S_OUT=C); SUB_OUT = C OR B;END ARCHITECTURE FS1;二进制全加器,元件声明与元件例化PONENT,PORT MAP/或门LIBRARY IEEE; ;USE IEEE.ST

40、D_LOGIC_1164.ALL;ENTITY OR2A ISPORT(A,B : IN STD_LOGIC; C : OUT STD_LOGIC);END OR2A;ARCHITECTURE ART1 OF OR2A ISBEGIN C=A OR B;END ART1;/半加器;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY H_ADDER IS PORT(A,B : IN STD_LOGIC; CO,SO: OUT STD_LOGIC);END H_ADDER;ARCHITECTURE ART2 OF H_ADDER ISBEGIN SO = A XOR B; CO = A AND B;END ART2;1位二进制全加器顶层设计:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164。ALL;ENTITY F_ADDER ISPORT(AIN,BIN,CIN : IN STD_LOGIC; COUT,SUM : OUT STD_LOGIC);END F_ADDER;ARCHITECTURE ART3 OF F_ADDER ISPONENT H_ADDER /元件声明; PORT(A,B : IN STD_LOGIC; CO,SO

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。