数电详解PPT课件

数电详解PPT课件

《数电详解PPT课件》由会员分享,可在线阅读,更多相关《数电详解PPT课件(51页珍藏版)》请在装配图网上搜索。

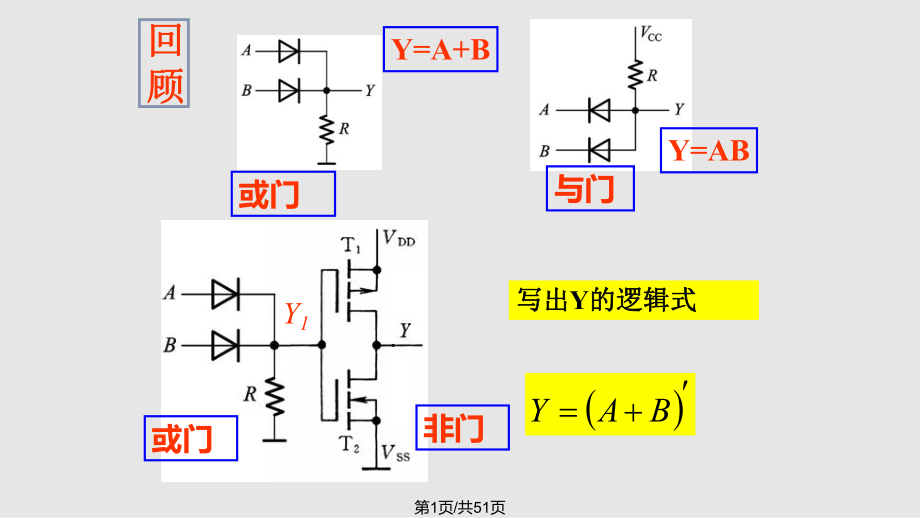

1、回回顾顾写出写出Y的逻辑式的逻辑式与门或门或门非门Y1Y=A+BY=ABBAY第1页/共51页P沟道增强型沟道增强型场效应管场效应管N 沟道增强沟道增强型场效应管型场效应管MOS 管导通。管导通。 MOS 管导通。管导通。)(thGSiUU 当:)(thGSiUU 当:DSBGUiiDDSBGUiiD第2页/共51页DSBGUiiDDSBGUiiD第3页/共51页VDDST1DT2vivo3.3.3 静态输入特性和输出特性静态输入特性和输出特性P83vi的范围在0.7VDD+0.7一、输入特性一、输入特性-输入电压与输入电流的关系输入电压与输入电流的关系第4页/共51页二、输出特性二、输出特性

2、输出电压和输出电流的关系,输出电压和输出电流的关系,包括包括输出为低电平输出输出为低电平输出特性和输出为高电平输出特性特性和输出为高电平输出特性1.低电平输出特性低电平输出特性 在输入为高电平时,即在输入为高电平时,即 vIVIHVDD时,此时时,此时T1截止,截止, T2导通,电流从负载注入导通,电流从负载注入T2,输出电压输出电压VOL随电流增加而提随电流增加而提高。高。图图3.3.17 输出为低电平时的电路输出为低电平时的电路第5页/共51页其特性曲线如图其特性曲线如图3.3.18所所示示3.3.3 CMOS 非门静态输入和输出特性非门静态输入和输出特性实际上是实际上是T2管漏极电流管漏

3、极电流iD和漏源电压和漏源电压vDS之间的关系之间的关系图图3.3.18 输出为低电平时的输出特性输出为低电平时的输出特性第6页/共51页2.高电平输出特性高电平输出特性 在输入为低电平,即在输入为低电平,即 vIVIL0时,此时时,此时T1导通,导通, T2截止,如图截止,如图3.3.18所示,电流从所示,电流从T1管流出到负载,输管流出到负载,输出电压出电压VOHVDDIOHRON1随电流增加而下降。随电流增加而下降。图图3.3.18 输出为高电平时的电路输出为高电平时的电路电流的实际方向与所电流的实际方向与所设方向相反设方向相反第7页/共51页其特性曲线如图其特性曲线如图3.3.19所所

4、示示3.3.3 CMOS 反相器的静态输入和输出特性反相器的静态输入和输出特性图图3.3.19 输出为高电平时的输出特性输出为高电平时的输出特性高电平输出特性也和管高电平输出特性也和管子开启电压有关子开启电压有关,T1导导通时通时vGS1越负,导通电越负,导通电阻越小,阻越小,VOH电压也就电压也就下降的越少。下降的越少。第8页/共51页3.3.4 CMOS反相器的动态反相器的动态特性特性一、传输延迟时间一、传输延迟时间tPHL和和tPLH 前面的输入输出特性为静态特性,没有考虑电路前面的输入输出特性为静态特性,没有考虑电路转换状态时的延迟,动态特性要考虑传输延迟时间。转换状态时的延迟,动态特

5、性要考虑传输延迟时间。 由于由于MOS管的寄生电容和负载电容的存在,使得管的寄生电容和负载电容的存在,使得输出电压的变化滞后输入电压的变化,将输出电压变输出电压的变化滞后输入电压的变化,将输出电压变化迟后输入电压变化的时间称为传输延迟时间。化迟后输入电压变化的时间称为传输延迟时间。tPHL输出由高电平跳变为低电平时的传输延迟时间输出由高电平跳变为低电平时的传输延迟时间tPLH输出由低电平跳变为高电平时的传输延迟时间输出由低电平跳变为高电平时的传输延迟时间tpd平均传输延迟时间,平均传输延迟时间,tpd( tPHL tPLH)/ 2CMOS电路电路tPHL tPLH第9页/共51页图图3.3.2

6、0为为CMOS非门的输出输入波形。非门的输出输入波形。3.3.4 CMOS反相器的动态特性反相器的动态特性3.3.20 CMOS反相器的输入输出波形反相器的输入输出波形tPHL输入电压前沿上升到幅值的输入电压前沿上升到幅值的50与输出后沿下与输出后沿下降到幅值的降到幅值的50之间所需时间。之间所需时间。tPLH输入电压后沿下降到幅值的输入电压后沿下降到幅值的50与输出前沿上升与输出前沿上升到幅值的到幅值的50之间所需时间。之间所需时间。第10页/共51页3.3.5 其他类型的其他类型的CMOS逻辑门逻辑门(P91)1.CMOS与非门与非门 如图如图3.3.21所示,所示,T1、 T3为两个并联

7、的为两个并联的PMOS, T2、 T4为两为两个串联的个串联的NMOS*A、B有一个为有一个为“0”时,时,T2、 T4至少有一至少有一个截止,个截止, T1、 T3至少至少有一个导通,故输出有一个导通,故输出为高电平,为高电平,Y1图图3.3.21 CMOS与非门与非门一、其他逻辑功能的一、其他逻辑功能的CMOS门电路门电路第11页/共51页故:故:)( ABY*A、B同时为同时为“1”时,时,T2、 T4同时导通,同时导通, T1、 T3同时截止,故输出为同时截止,故输出为低电平,低电平,Y0图图3.3.21 CMOS与非门与非门3.3.5 其他类型的其他类型的CMOS逻辑门逻辑门第12页

8、/共51页如图所示,如图所示,T1、 T3为两个串为两个串联的联的PMOS, T2、 T4为两个为两个并联的并联的NMOS)(BAY2. 2. 或非门:或非门:A、B有一个为有一个为“1”时,时,T2、 T4至少有一个导通,至少有一个导通, T1、 T3至少有一个截止,故输出为至少有一个截止,故输出为低电平,低电平,Y0A、B同时为同时为“0”时,时,T2、 T4同时截止,同时截止, T1、 T3同时导同时导通故输出为高电平,通故输出为高电平,Y1故:故:3.3.5其他类型的其他类型的CMOS逻辑门逻辑门图图3.3.28 CMOS或非门或非门第13页/共51页3.3.带缓冲级的带缓冲级的CMO

9、SCMOS门电门电路路3.3.5其他类型的其他类型的CMOS逻辑门逻辑门上面电路存在的问题:上面电路存在的问题:(以与非门为例)(以与非门为例)输出电阻输出电阻RO受输入状态受输入状态的影响;的影响;ONONOONONOONONONOONONONORRRBARRRBARRRRBARRRRBA3131420, 11, 021/0, 021, 1则则则则第14页/共51页输出的高低电平受输入输出的高低电平受输入端数目的影响端数目的影响3.3.5其他类型的其他类型的CMOS逻辑门逻辑门 输入端数目愈多,输输入端数目愈多,输出为低电平时串联的导通电出为低电平时串联的导通电阻越多,低电平阻越多,低电平V

10、OL越高;越高;输出为高电平时,并联电阻输出为高电平时,并联电阻也多,输出高电平也多,输出高电平VOH也提也提高高 输入状态不同对电压传输特性有影响,使输入状态不同对电压传输特性有影响,使T2、T4达达到开启电压时,输入电压到开启电压时,输入电压vI不同不同第15页/共51页 改进电路均采用带缓冲级的结构,如图改进电路均采用带缓冲级的结构,如图3.3.23为带缓冲级的为带缓冲级的CMOS与非门电路与非门电路与非门缓冲器或非门图图3.3.23 带缓冲级的与非门带缓冲级的与非门或非门缓冲器与非门 第16页/共51页输出输出为为)()( ABBAF3.3.5 其他类型的其他类型的CMOS逻辑门逻辑门

11、图图3.3.23 带缓冲级的与非门带缓冲级的与非门带缓冲级的带缓冲级的CMOS门电路其输出电阻、输出高低电平门电路其输出电阻、输出高低电平均不受输入端状态的影响,电压传输特性更陡。均不受输入端状态的影响,电压传输特性更陡。第17页/共51页线与逻辑线与逻辑Y=Y1Y201第18页/共51页二、漏极开路输出的门电路(二、漏极开路输出的门电路(OD门)门) 为了满足输出电平的变换,输出大负载电流,以及为了满足输出电平的变换,输出大负载电流,以及实现实现“线与线与”功能,将功能,将CMOS门电路的输出级做成漏门电路的输出级做成漏极开路的形式,称为极开路的形式,称为漏极开路输出的门电路,简称漏极开路输

12、出的门电路,简称OD(OpenDrain Output)门)门 图图3.3.24为为OD输出与非门输出与非门74HC03电路结构图,其与电路结构图,其与非门和非门都是非门和非门都是CMOS逻辑门,输逻辑门,输出管为漏极开路的出管为漏极开路的NMOS门门图图3.3.24 OD输出与非门输出与非门74HC03电路结构图电路结构图OD门门1.结构和符号结构和符号第19页/共51页图图3.3.25所示为所示为OD门的逻辑符门的逻辑符号号2.工作原理工作原理 在使用在使用OD门时,一定要将门时,一定要将输出端通过电阻(叫做上拉电输出端通过电阻(叫做上拉电阻)接到电源上,如图阻)接到电源上,如图3.3.2

13、6所所示示OD门门第20页/共51页当当A、B有一个为低电平,则有一个为低电平,则TN 截止,输出截止,输出voVDD2,为高电平;当,为高电平;当A、B同时为高电平,则同时为高电平,则TN 导导通,输出通,输出vo0,为低电平。故输出输入的逻辑关,为低电平。故输出输入的逻辑关系为系为3.3.5 其他类型的其他类型的CMOS逻辑门逻辑门)( ABF由此可见,输出高电平可以改变,故可作电平转换由此可见,输出高电平可以改变,故可作电平转换第21页/共51页3.“线与线与”的实现的实现(重点内容重点内容) 普通的普通的CMOS逻辑门输出端逻辑门输出端不能并联使用不能并联使用,但,但OD门可以将输出端

14、直接相接,即实现线与逻辑,其电路门可以将输出端直接相接,即实现线与逻辑,其电路如图如图3.3.27所示所示图图3.3.27 线与逻辑电路的接法线与逻辑电路的接法第22页/共51页其工作原理为:其工作原理为:3.3.5 其他类型的其他类型的CMOS逻辑门逻辑门图图3.3.27 线与逻辑电路的接法线与逻辑电路的接法当当Y1、 Y2有一个为低电平时,则为低电平;只有有一个为低电平时,则为低电平;只有Y1、 Y2同时为高电平,两个输出管同时截止,输出为高电同时为高电平,两个输出管同时截止,输出为高电平,平,Y和和Y1、 Y2为与的关系为与的关系第23页/共51页输出端逻辑式为输出端逻辑式为3.3.5

15、其他类型的其他类型的CMOS逻辑门逻辑门)CDAB()(CD)AB(21YYY故故OD门的线与实现了门的线与实现了与或与或非的逻辑功能。非的逻辑功能。4.上拉电阻上拉电阻RL的计算的计算 在使用在使用OD门做线与时,一定外接上拉电阻门做线与时,一定外接上拉电阻RL。但。但RL的大小会影响驱动门输出电平的大小。的大小会影响驱动门输出电平的大小。 RL上的压降不上的压降不能太大,否则高电平会低于标准值;能太大,否则高电平会低于标准值;RL上的压降不能太上的压降不能太小,否则低电平会高于标准值。故小,否则低电平会高于标准值。故R L的的 取值要合适。取值要合适。第24页/共51页4.上拉电阻上拉电阻

16、RL的计的计算算P95 设有设有n 个个OD门门的输出端并联使用,的输出端并联使用,负载为负载为CMOS与非门与非门的输入端。的输入端。 输出为高输出为高电平电平 当所有的当所有的OD门门输出管截止输出为输出管截止输出为高电平时,其电流高电平时,其电流的方向如图所示。的方向如图所示。IOH、IIL是保护二极管和寄生二极管的反向漏电流形成是保护二极管和寄生二极管的反向漏电流形成第25页/共51页(min)(OHIHOHLDDVmInIRV IHOHOHDDLmInIVVR (min)(max) 若若OD门输出管门输出管截止时的漏电流为截止时的漏电流为IOH,负载门输入为高负载门输入为高电平时的输

17、入电流为电平时的输入电流为IIH,n为并联为并联OD门(驱动门(驱动门)的个数,门)的个数,m为负载门输入高电为负载门输入高电平电流的个数,所以:平电流的个数,所以:第26页/共51页 OD门输出为低电平门输出为低电平 当只有一个当只有一个OD门输门输出管导通时,其电流的出管导通时,其电流的实际流向如图实际流向如图3.3.29所示。所示。其中其中IIL是每个负载门低是每个负载门低电平输入电流的绝对值;电平输入电流的绝对值;IOLmax是是OD门最大允许门最大允许的负载电流。,则的负载电流。,则max(max)(OLILLOLDDIImRVV ILOLOLDDLImIVVR max(max)(m

18、in)mm 第27页/共51页5.OD门的特点:门的特点:6.OD门的应用门的应用通过改变通过改变VDD2的值,来改变输出的值,来改变输出高电平高电平VOH的大小;的大小;OD门的输出管设计尺寸较大,门的输出管设计尺寸较大,可以承受很大的电流和电压,故可以承受很大的电流和电压,故可以可以直接驱动小型继电器直接驱动小型继电器。实现与或非逻辑实现与或非逻辑)()()(21 CDABCDABYYY第28页/共51页电平转换电平转换 由于由于OD门的高电平可以通过外加电源改变,故它门的高电平可以通过外加电源改变,故它可作为电平转换电路。一般可作为电平转换电路。一般CMOS与非门的电平与非门的电平0 1

19、2V,而而TTL门为门为0 3.6V。若需要转换逻辑电平,只要将负。若需要转换逻辑电平,只要将负载电阻接到载电阻接到5V电源即可,其电路如图电源即可,其电路如图3.3.30所示所示第29页/共51页实现数据采集实现数据采集 如图如图3.3.31所示所示,可实现母线(总线)的数据的接可实现母线(总线)的数据的接收和传送收和传送 可利用选通信号可利用选通信号SA SC来实现对不同来实现对不同通道数据的采集,并通道数据的采集,并输送到母线上。接收输送到母线上。接收时,利用选通信号时,利用选通信号SD SG来实现数据从来实现数据从不同通道输出。不同通道输出。第30页/共51页【例例】试为电路中的外接电

20、试为电路中的外接电阻阻RL选定合适的阻值。已知选定合适的阻值。已知G1、G2为为OD与非门与非门74HC03,输出管截止时的漏电流为输出管截止时的漏电流为IOHmax5A,输出管导通时,输出管导通时允许的最大负载电流为允许的最大负载电流为IOLmax5.2mA。G3、G4和和G5均为均为74HC00系列与非门,它们的系列与非门,它们的低电平输入电流和高电平输低电平输入电流和高电平输入电流为入电流为1A。,要求。,要求OD门门的高电平:的高电平:VOH4.4V,低电,低电平:平:VOL0.33V. 第31页/共51页解:驱动管输出为高电平解:驱动管输出为高电平时时K9 . 0109102 . 5

21、33. 05ImIVVR63IL(max)OL(max)OLDDminL)(K6 .31101910524 . 45mInIVVR66IHOHOHminDDmaxL)(驱动管输出为低电平时驱动管输出为低电平时则可取则可取RL10k第32页/共51页下图为下图为CMOS传输门的电路图及逻辑符号。传输门的电路图及逻辑符号。三、三、 CMOS传输门传输门-又称为模拟电子开关又称为模拟电子开关其中其中T1为为NMOS管,管, T2为为PMOS管,管,C和和C 为一对互补为一对互补控制信号控制信号1.电路结构及逻辑符号电路结构及逻辑符号第33页/共51页2.工作原理工作原理 若若CMOS传输门的一端接输

22、入电压传输门的一端接输入电压vI,另一端接负,另一端接负载电阻载电阻RL,如图,如图3.3.34所示。所示。图图3.3.34 传输门的工作电路传输门的工作电路设设RL RON, VIH VDD, VIL0。C的高低电平为的高低电平为VDD和和0。(1)C0, C 1 无论无论vI在在0 VDD之间之间如何变化,如何变化, T1和和T2同时截同时截止,输入和输出断开,传输止,输入和输出断开,传输门截止(为高组态),门截止(为高组态),输出输出vo010VDD第34页/共51页(2)C1, C 0图图3.3.35 CMOS的工作状态的工作状态0 vI VDD-VGS(th)N|VGS(th)P|

23、vI RTG.2. 由于由于MOS管的导通内阻和输入电压有关,为了减小管的导通内阻和输入电压有关,为了减小vI对对RTG的影响,改进电路的影响,改进电路74HC4066四双向模拟开关,四双向模拟开关,RTG=30,而且,而且vI变化变化RTG不变不变第39页/共51页 其电路如图其电路如图3.3.38所示,这是三态反相器,也称为所示,这是三态反相器,也称为输出缓冲器,输出的状态不仅有高电平、低电平,还有输出缓冲器,输出的状态不仅有高电平、低电平,还有第三态高阻态第三态高阻态图图3.3.38 CMOS三态门的电路及符号三态门的电路及符号01011101010高组态AY四、三态输出的四、三态输出的

24、CMOS门电路门电路第40页/共51页其工作原理为其工作原理为)(高阻时,时,ZYNEAYNE10其中其中EN 为使能端,为使能端,且低电平有效,即且低电平有效,即EN 0,YA 低电平有效低电平有效CMOS三态门形式有多种,它也可以在三态门形式有多种,它也可以在CMOS反相器反相器基础上加控制电路构成,基础上加控制电路构成,第41页/共51页当当EN 0时,时,T1、T4导通,导通,输出为输出为Y A 图图3.3.39为另一种为另一种CMOS三三态非门,使能端(控制端)态非门,使能端(控制端)也是低电平有效也是低电平有效当当EN 1时,时,T1、T4截止,截止,输出为输出为Y Z(高阻态)(

25、高阻态)第42页/共51页图图3.3.40所示电路也是一种所示电路也是一种CMOS三态非门三态非门当当EN1时,时,T 2导通,导通,Y A;当当EN0时,时, T 2、T1截止,输出为截止,输出为Y Z(高阻态)。这种三态门使能端(高阻态)。这种三态门使能端是高电平有效。是高电平有效。第43页/共51页CMOS门电路如图所示,试分析电路的逻辑功能门电路如图所示,试分析电路的逻辑功能解:当解:当C0时,时, C 1,传输门为高,传输门为高阻态,故输出阻态,故输出YZ故这是由故这是由CMOS或非或非门和门和CMOS传输门构传输门构成的成的三态或非门三态或非门传输门传输门当当C1时,时,C 0,传

26、输门为开启,输出传输门为开启,输出Y(AB) 第44页/共51页解:(解:(a) YA例:由例:由CMOS传输门构成的电路如图传输门构成的电路如图3.3.42(a)、)、(b)、()、(c)所示,试写出各电路的输出函数的)所示,试写出各电路的输出函数的表达式。表达式。第45页/共51页(b)(b)输出、输入真值表为输出、输入真值表为ABY2000011110001输出逻辑式为输出逻辑式为ABY 第46页/共51页其输出逻辑式为其输出逻辑式为)(BAY注:为了避免传输门关闭时注:为了避免传输门关闭时出现高阻态,可以在输出端出现高阻态,可以在输出端通过大电阻接地;也可以输通过大电阻接地;也可以输出

27、端通过电阻接电源。这样出端通过电阻接电源。这样输出端均会有确定的值。输出端均会有确定的值。(C)其输出输入真值表为其输出输入真值表为第47页/共51页例例3.3.4 电路如图电路如图3.3.43所示。试分析其逻辑所示。试分析其逻辑功能功能解:当解:当EN 1时,传输门截止,输出为时,传输门截止,输出为YZ(高阻态)(高阻态)当当EN 0时,传输门开启,时,传输门开启,CMOS反相器的输出通过反相器的输出通过传输门到达输出,使得传输门到达输出,使得YA ,故为三态输出的反相器。,故为三态输出的反相器。第48页/共51页a. a. 总线结构总线结构这样只要分时控制各三态门这样只要分时控制各三态门的

28、的E(E )端,就能把各个门)端,就能把各个门的数据输入信号按要求依次的数据输入信号按要求依次送到总线,进行数据传输。送到总线,进行数据传输。但注意使能端不能同时为但注意使能端不能同时为“1”三态门的应用三态门的应用它可以实现线与的功能,即它可以实现线与的功能,即输出端可以并联。如图输出端可以并联。如图3.3.44所示所示3.3.5 其他类型的其他类型的CMOS逻辑门逻辑门第49页/共51页电路如图电路如图2.3.45所示,则所示,则b. 数据的双向传输数据的双向传输3.3.5 其他类型的其他类型的CMOS逻辑门逻辑门当当EN1时,三态门时,三态门G1输输出为出为D o, G2输出为高阻输出为高阻态;态;当当EN0时,三态门时,三态门G1输出为高阻态,输出为高阻态, G2输输出为出为D 1 Do3.3.6 CMOS电路的正确使用(自学)电路的正确使用(自学)P101 3.4 *其他类型的其他类型的MOS集成电路(自学)集成电路(自学)第50页/共51页感谢您的观看。第51页/共51页

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。