Verilog-HDL数字设计与综合-夏宇闻译第二版课后题答案

Verilog-HDL数字设计与综合-夏宇闻译第二版课后题答案

《Verilog-HDL数字设计与综合-夏宇闻译第二版课后题答案》由会员分享,可在线阅读,更多相关《Verilog-HDL数字设计与综合-夏宇闻译第二版课后题答案(7页珍藏版)》请在装配图网上搜索。

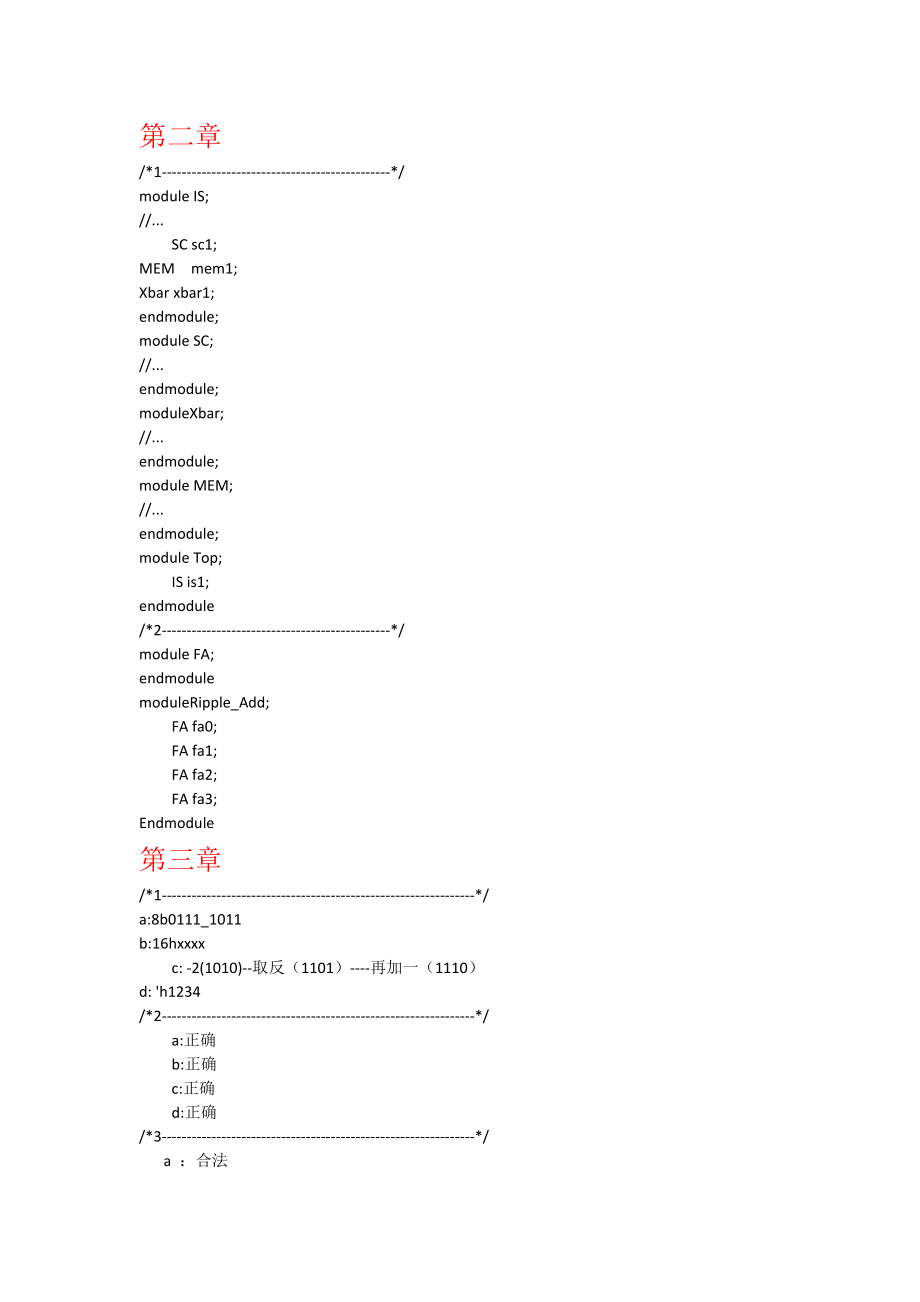

1、第二章/*1-*/module IS;/.SC sc1;MEM mem1;Xbar xbar1;endmodule;module SC;/.endmodule;moduleXbar;/.endmodule;module MEM;/.endmodule;module Top;IS is1;endmodule/*2-*/module FA;endmodulemoduleRipple_Add;FA fa0;FA fa1;FA fa2;FA fa3;Endmodule第三章/*1-*/a:8b0111_1011b:16hxxxxc: -2(1010)-取反(1101)-再加一(1110)d: h123

2、4/*2-*/a:正确b:正确c:正确d:正确/*3-*/ a :合法 b :合法 c :不合法,含有$ 为延时含义 d :标识符组成:字母数字下划线。/*4-*/a: wire 7:0 a_in;b: reg 31:0 c: integer count;d: time snap_shot;e: integer delays20;f: reg 63:0 mem256;g: parameter cach_size=256;/*5-*/a : 1010b: 10c : 400第四章/*1-*/模块的基本组成部分有哪些?哪几个部分必须出现?模块定义已关键字module开始,模块名,端口列表,端口声明

3、和可选的参数声明出现在其他部分的前面,endmodule必须为最后一条语句1)wire。reg和其他类型的变量的声明2)数据流语句(assign,连续赋值语句)3)低层模块实例4)always和initial块,所有的行为语句都在这些块中5) 任务和函数。其中module和模块名和endmodule是必不可少的。/*2-*/一个不与外界环境交互的模块是否有端口?模块定义中是否有端口列表?不与外界交互即没有端口列表,在没有端口的情况下端口列表也是不存在的。/*3-*/moduleshift_reg(reg_in3:0 , clock , reg_out3:0 );input 3:0 reg_in

4、;input clock;output 3:0 reg_out;/.endmodule;/*4-*/connect in ordermodule stimulus();reg 3:0 REG_IN;wire 3:0 REG_OUT;reg CLK;shift_regsr1(REG_IN,CLK,REG_OUT);endmodule/*5-*/connect by namemodule stimulus();reg 3:0 REG_IN;wire 3:0 REG_OUT;reg CLK;shift_regsr1(.clock(CLK) ,.reg_in(REG_IN) , .reg_out(RE

5、G_OUT) );endmodule/*6-*/stimulus.REG_INstimulus.CLK;stimulus.REG_OUT;/*7-*/stimulus.sr1;stimulus.sr1.clock;stimulus.sr1.reg_in;stimulus.sr1.reg_out;第五章/*1-*/利用双输入的nand门设计自己的与或非门。/my_andmodulemy_and(out , in1,in2);input in1,in2;output out;endmodule/my_notmodulemy_not(out , in1);input in1;output out;n

6、and(out , in1 ,in1 );endmodule/my_andmodulemy_or(out ,in1 ,in2);wire t;nand(t,in1,in2);nand(out,t,t);/endmodule/*2-*/使用上题中完成的my_or,my_and,my_not构造一个双/输入的xor门,其功能是计算z=xy+xy/*3-*/全加器module sum(a,b,c_in,sum,c_out);inputa,b,c_in;outputsum,c_out;wire y1,y2,y3,y4;wire x1,x2,x3;or(sum,y1,y2,y3,y4);and(y1,a

7、,b,c_in);and(y2,x1,b,x3);and(y3,x1,x2,c_in);and(y4,a,x2,x3);not(x1,a);not(x2,b);not(x3,c);wire j1,j2,j3;or(c_out,j1,j2,j3);and(j1,a,b);and(j2,b,c_in);and(j3,a,c_in);endmodule/*4-*/带有延时的SR锁存器module SR(reset , q ,set , qbar);inputreset,set;outputq,qbar;wire line1,line2;nor( line2 , reset ,line1 );nor(

8、 line1, set ,line2 );endmodule/*-ISE中一个端口如何接多根线?*/*5-*/module select(out,in1,in2,s);input in1,in2,s;output out;/3为上升延迟,4为下降延时,5为关断延迟。bufif1 #(1:2:3,3:4:5,5:6:7) b2(out,in1,s);bufif0 #(1:2:3,3:4:5,5:6:7) b1(out,in2,s);endmodule/*-*/第六章/*1-*/全减器/输入 :x,y,z(前面的借位)/输出:差和借位module sub(x,y,z,D,B);inputx,y,z

9、;output D,B;wire y0,y1,y2,y3;wire j1,j2,j0;/非门not(j0,x);not(j1,y);not(j2,z);and(y0,j0,j1,j2);and(y1,j0,y,j2);and(y2,x,j1,j2);and(y3,x,y,z);or(D,y0,y1,y2,y3);/Bwire a1,a0,a2;and(a0 , j0 ,y);and( a1, j0, z);and( a2, y , z);or(B,a1,a0,a2);endmodule/激励模块:module stimulus;/initial 从仿真0时刻开始,而且只执行一次,若程序中有若干

10、个initial块,则并发执行。rega,b,c;wired,e;regi;sub sub(a,b,c,d,e);initialfor(i=1 ;i0;) begin#5 ;a=1;b=1;c=0;#5;a=1;b=0;c=0;endendmodule/*2-*/大小比较器modulecmp(A ,B ,A_gt_B , A_lt_B,A_eq_B);input 3:0 A,3:0 B;outputA_gt_B , A_lt_B , A_eq_B ;endmodule/*3 -*/modulesyn_counter(clear,clock,count_enable,Q);inputclear,

11、clock,count_enable;output 3:0 Q;wire 3:0 Q;wire b1,b2,b3;nand(b1,count_enable,Q1);nand(b2,b1,Q2);nand(b3,b2,Q3);jk jk1(count_enable,count_enable,clear,clock,Q0,);jk jk2(b1,b1,clear,clock,Q1,);jk jk3(b2,b2,clear,clock,Q2,);jk jk4(b3,b3,clear,clock,Q3,);endmodulemodulejk(J,K,clear,clock,q,qbar);inputJ

12、,K,clear,clock;outputq,qbar;wirea,y,c,b,ybar,cbar,d;not (cbar,clock);nand a1(a,qbar,J,clock,clear);nand a2(b,clock,K,q);nand a3(y,a,ybar);nand a4(ybar,y,clear,b);nand a5(c,y,cbar);nand a6(d,cbar,ybar);nand a7(q,c,qbar);nand a8(qbar,q,clear,d);endmodule第七章/*1-*/reg oscillate=0;initialbeginforever#30 oscillate=oscillate;end/*2-*/initialclock=0;alwaysbegin#30 clock=1;#10 clock=0;end/*3 -*/执行时刻:0,10,15,35.最终结果:a=0,b=1,c=0;d=3b010;/*4-*/执行时刻:0,10,5,20.最终结果:a=0,b=1,c=0;d=3b010;/*5 -*/a,b,c,d: 0 ,1,1,0/每个initial中的语句是串行执行的。/*6 -*/ d=0;

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。