可编程逻辑器件设计实验报告

可编程逻辑器件设计实验报告

《可编程逻辑器件设计实验报告》由会员分享,可在线阅读,更多相关《可编程逻辑器件设计实验报告(43页珍藏版)》请在装配图网上搜索。

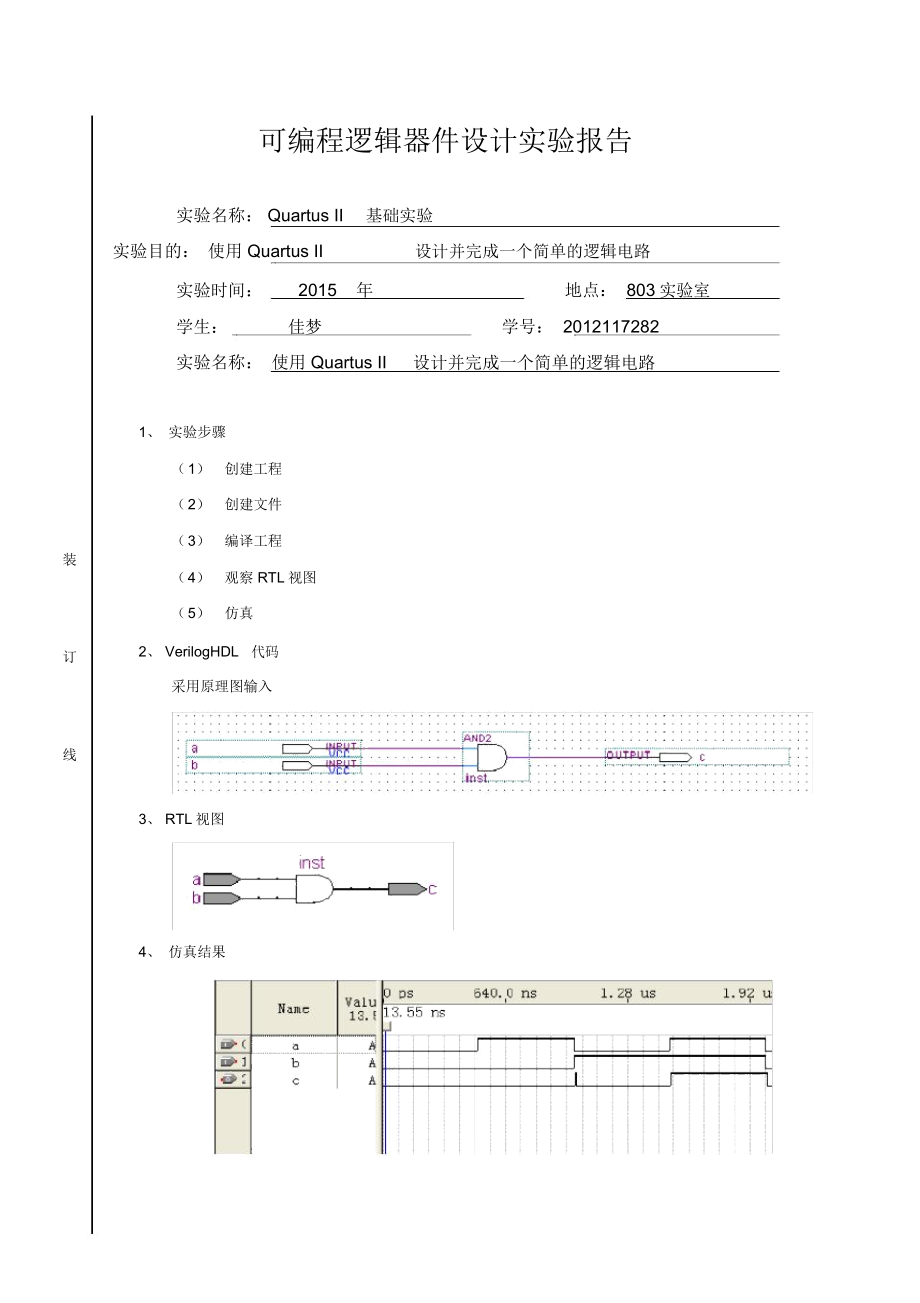

1、可编程逻辑器件设计实验报告实验名称: Quartus II基础实验实验目的: 使用 Quartus II设计并完成一个简单的逻辑电路实验时间:2015 年地点: 803实验室学生:佳梦学号: 2012117282实验名称: 使用 Quartus II设计并完成一个简单的逻辑电路1、 实验步骤( 1) 创建工程( 2) 创建文件( 3) 编译工程装( 4) 观察 RTL视图( 5) 仿真订2、 VerilogHDL代码采用原理图输入线3、 RTL视图4、 仿真结果可编程逻辑器件设计实验报告实验名称: 第二部分: VerilogHDL 基础实验实验目的: 掌握 Quartus II软件的基本使用方

2、法,完成基本时序电路设计实验时间:2015年地点:803 实验室学生:佳梦学号:2012117282实验名称: 简单 D 触发器1、实验步骤( 1) 创建工程( 2) 创建文件( 3) 编译工程( 4) 观察 RTL视图装(5) 仿真2、 VerilogHDL代码module _DFF (clk,d,q);订input clk,d;output q;reg q;always (posedge clk)线beginq=d;endendmodule3、 RTL视图qreg0dclkPREqDQENACLR4、仿真结果可编程逻辑器件设计实验报告实验名称: 第二部分: VerilogHDL 基础实验实

3、验目的: 掌握 Quartus II软件的基本使用方法,完成基本时序电路设计实验时间:2015年地点:803 实验室学生:佳梦学号:2012117282实验名称: 同步置数的D触发器1、 实验步骤创建工程、创建文件、编译工程、观察RTL视图、仿真2、VerilogHDL代码装订线module CFQ (clk,d,load,q);input clk,d,load;output q;reg q;always(posedge clk)beginif(!load)q=1;elseq=d;endendmodule3、 RTL 视图loadqreg010PREDQqd1q0ENAclkCLR4、仿真结果

4、可编程逻辑器件设计实验报告实验名称: 第二部分: VerilogHDL 基础实验实验目的: 掌握 Quartus II软件的基本使用方法,完成基本时序电路设计实验时间:2015 年地点:803 实验室学生:佳梦学号:2012117282实验名称: 同步置数异步清零的D触发器1、实验步骤创建工程、创建文件、编译工程、观察RTL视图、仿真2、 VerilogHDL代码module _DFf (clk,d,load,rest,q);input clk,d,load,rest;output q;装reg q;always(posedge clk or negedge rest)beginif(!res

5、t)订q=0;else if (!load)q=1;else线q=d;endendmodule3、 RTL 视图loadqreg010PREqd1DQq0ENAclkCLRrest4、仿真结果可编程逻辑器件设计实验报告实验名称: 第二部分: VerilogHDL 基础实验实验目的: 掌握 Quartus II软件的基本使用方法,完成基本时序电路设计实验时间:2015年地点:803 实验室学生:佳梦实验名称: 带 Q_n输出的学号:D触发器20121172821、实验步骤创建工程、创建文件、编译工程、观察RTL视图、仿真2、 VerilogHDL代码装订module d_q(in,clk,q,s

6、et,a,reset,q_n);input clk,in,set,a,reset;output reg q,q_n;always(posedge clk,negedge reset)beginq_n=q;if(!reset)q=0;else if(!set)q=a;else线q=in;end3、 RTL 视图4、仿真结果可编程逻辑器件设计实验报告实验名称: 第二部分: VerilogHDL 基础实验实验目的: 掌握 Quartus II软件的基本使用方法,完成基本时序电路设计实验时间:2015年地点:803 实验室学生:佳梦学号:2012117282实验名称:4 选 1 数据选择器1、实验步骤

7、创建工程、创建文件、编译工程、观察RTL视图、仿真2、 VerilogHDL 代码module mux4_1 (in0,in1,in2,in3,s0,s1,out);inputs0,s1;inputin0,in1,in2,in3;装output out;reg out;always(in0,in1,in2,in3,s0,s1)begin订case(s0,s1)2b00:out=in0;2b01:out=in1;2b10:out=in2;线2b11:out=in3;default:out=1bz;endcaseendendmodule3、 RTL 视图Mux0s01.0sSEL1in3OUTou

8、tin2DATA3.0in1in0MUX4、仿真结果可编程逻辑器件设计实验报告实验名称: 第二部分: VerilogHDL 基础实验实验目的: 掌握 Quartus II软件的基本使用方法,完成基本时序电路设计实验时间:2015年地点:803 实验室学生:佳梦学号:2012117282实验名称:6 选 1 数据选择器1、实验步骤创建工程、创建文件、编译工程、观察RTL视图、仿真2、 VerilogHDL代码装订线module mux6_1 (in0,in1,in2,in3,in4,in5,s0,s1,s2,out);input s0,s1,s2;input in0,in1,in2,in3,in

9、4,in5;output out;reg out;always(in0,in1,in2,in3,in4,in5,s0,s1,s2)begincase(s0,s1,s2)3b000:out=in0;3b001:out=in1;3b010:out=in2;3b011:out=in3;3b100:out=in4;3b101:out=in5;default:out=1bz;endcaseendendmodule3、 RTL 视图Mux0s0s1SEL2.0s22 h0 -in5in4in3in2in1in0OUTDATA7.0MUXMux1SEL2.0OUTout18 h3F -DATA7.0outI

10、O_BUF (TRI)MUX4、仿真结果可编程逻辑器件设计实验报告实验名称: 第二部分: VerilogHDL 基础实验实验目的: 掌握 Quartus II软件的基本使用方法,完成基本时序电路设计实验时间:2015 年地点:803 实验室学生:佳梦学号:2012117282实验名称: 38 译码器( assign 语句实现)1、实验步骤创建工程、创建文件、编译工程、观察RTL视图、仿真2、 VerilogHDL代码module as_38(a,q);input 2:0 a;output 7:0 q;装parameter m=8b00000001;assign q=(ma);endmodule

11、3、 RTL 视图订线4、仿真结果可编程逻辑器件设计实验报告实验名称: 第二部分: VerilogHDL 基础实验实验目的: 掌握 Quartus II软件的基本使用方法,完成基本时序电路设计实验时间:2015 年地点:803 实验室学生:佳梦学号:2012117282实验名称: 38 译码器( always 语句实现)1、实验步骤创建工程、创建文件、编译工程、观察RTL视图、仿真2、 VerilogHDL代码module yima3_8(in0,in1,in2,out);input in0,in1,in2;output 7:0 out;装reg 7:0 out;always(in0,in1,

12、in2,out)begincase(in2,in1,in0)订3b000:out=8b00000001;3b001:out=8b00000010;3b010:out=8b00000100;3b011:out=8b00001000;线3b100:out=8b00010000;3b101:out=8b00100001;3b110:out=8b01000001;3b111:out=8b10000001;default:out=2bz;endcaseendendmodule3、 RTL 视图Decoder0in2in1IN2.0OUT7.0WideOr0out7.0in0DECODER4、仿真结果可编

13、程逻辑器件设计实验报告实验名称: 第三部分: VerilogHDL 中级实验实验目的: 加深理解,熟练操作实验时间:2015年地点:803 实验室学生:佳梦学号:2012117282实验名称: 设计一个模 10 计数器(异步清零,同步置数)1、实验步骤创建工程、创建文件、编译工程、观察RTL视图、仿真2、 VerilogHDL代码装订线module m10(clk,set,reset,qout,data,cout);input clk,set,reset;input 3:0 data;output reg 3:0 qout;output reg cout;always(posedge clk,

14、negedge reset)beginif(!reset)beginqout=0;cout=0;endelse if(set=0)beginqout=data;cout=0;endelse if(qout9)beginqout=qout+1;cout=0;endelsebeginqout=0;cout=1;endendendmodule3、 RTL 视图4、仿真结果可编程逻辑器件设计实验报告实验名称: 第三部分: VerilogHDL 中级实验实验目的: 加深理解,熟练操作实验时间:2015年地点:803 实验室学生:佳梦实验名称: 设计一个模学号: 2012117282 60 计数器(异步清

15、零,同步置数)1、实验步骤创建工程、创建文件、编译工程、观察RTL视图、仿真2、 VerilogHDL代码装订线module m_60(clk,load,reset,a,cnt,cout);input clk,load,reset;input 5:0 a;output cout;output 5:0t;reg 5:0t;reg cout;always(posedge clk or negedge reset)beginif(!reset)t=6b00_0000;else if(load)t=a;elsebeginif(cnt6d59)begint=cnt+1;cout=0;endelsebeg

16、incout=1;t=6b00_0000;endendendendmodule3、 RTL 视图cnt4reg0PREDQclkcnt5.0ENAAdd0CLRSELA5.06 h00 -DATAAreset6 h01 -+OUT0B5.0DATABcnt3reg0PREADDERDQMUX21ENACLRcnt2reg0PREDQENACLRcnt1reg0PREDQENACLRcnt0reg0PREDQENACLRa5.0load4、仿真结果cnt11.6SELcnt5reg0DATAAPREDQOUT0DATABENAcnt5.0MUX21CLRLessThan0A5.0coutreg0

17、B5.00PRE6 h3B -DQcout1LESS_THANcout0ENACLR可编程逻辑器件设计实验报告实验名称: 第三部分: VerilogHDL 中级实验实验目的: 加深理解,熟练操作实验时间:2015 年地点:803 实验室学生:佳梦学号:2012117282实验名称: 设计一个 BCD码计数器1、实验步骤创建工程、创建文件、编译工程、观察RTL视图、仿真2、 VerilogHDL 代码module add_sub(ina,inb,sum1,sum2);input 3:0 ina;input 3:0 inb;装output 4:0 sum1;output 4:0 sum2;reg

18、4:0 sum1;reg 4:0 sum2;订always(ina,inb)beginsum1=ina-inb;线sum2=ina+inb;endendmodule3、 RTL 视图1 h0 -Add1A4.0ina3.0B4.0+1 h0 -inb3.0ADDER1 h0 -Add01 h1 -A5.0B5.0+1 h0 -ADDER1 h1 -4、仿真结果sum24.0sum14.0可编程逻辑器件设计实验报告实验名称: 第三部分: VerilogHDL 中级实验实验目的: 加深理解,熟练操作实验时间:2015 年地点:803 实验室学生:佳梦学号:2012117282实验名称: 设计一个

19、4bit 加减计数器1、实验步骤创建工程、创建文件、编译工程、观察RTL视图、仿真2、 VerilogHDL 代码module add_bcd (a,clk,en,load,reset,out,cout);input 3:0 a;input clk,en,load,reset;装output 3:0 out;output cout;reg 3:0 out;reg cout;订always( posedge clk or negedge reset)beginif (!reset)out=4b0000;线else if(!load)out=a;else if(!en)out=out+1;else

20、out=out-1;endendmodule3、 RTL 视图out2reg0PREDQclkENACLRresetout1reg0PREDQENACLRout0reg0PREDQENACLRa3.0enload4、仿真结果Add11 h1 -A4.0B4.0+5 h1D -ADDERAdd0A3.0B3.0+4 h1 -ADDERout3.0out7.4SELSELout3reg00coutDATAAPREOUT0DATAADDATABOUT0QDATABout3.0ENAMUX21MUX21CLR可编程逻辑器件设计实验报告实验名称: 第三部分: VerilogHDL 中级实验实验目的: 加

21、深理解,熟练操作实验时间:2015 年地点:803 实验室学生:佳梦学号:2012117282实验名称: 设计一个 2、4、8 分频器1、实验步骤创建工程、创建文件、编译工程、观察RTL视图、仿真2、 VerilogHDL代码module div2_4_8(clk,clk_2,clk_4,clk_8);input clk;output clk_2,clk_4,clk_8;装reg clk_2,clk_4,clk_8;always(posedge clk)beginclk_2=clk_2;订endalways(posedge clk_2)beginclk_4=clk_4;线endalways(p

22、osedge clk_4)beginclk_8=clk_8;endendmodule3、 RTL 视图clk_8reg0clk_4reg0PREclk_2reg0PREDQclk_8DQPREclkDQENAENACLRENACLRCLRclk_4clk_24、仿真结果可编程逻辑器件设计实验报告实验名称: 第三部分: VerilogHDL 中级实验实验目的: 加深理解,熟练操作实验时间:2015 年地点:803 实验室学生:佳梦学号:2012117282实验名称: 设计一个 2N分频器1、实验步骤创建工程、创建文件、编译工程、观察2、 VerilogHDL代码module div_14(clk

23、,out);input clk;output out;装reg out;reg 2:0 temp;always(posedge clk)begin订if(temp3d6)temp=temp+1b1;elsebegin线out=out; temp=0;endendendmodule3、 RTL 视图temp2.0Add0SELA2.03 h0 -DATAA+B2.0OUT0DATAB3 h1 -ADDERMUX21RTL视图、仿真outreg0temp2.0Less Than0PREoutDQPREA2.0DQB2.0ENA3 h6 -ENACLRCLRLESS_THANclk4、仿真结果可编程

24、逻辑器件设计实验报告实验名称: 第三部分: VerilogHDL 中级实验实验目的: 加深理解,熟练操作实验时间:2015 年地点:803 实验室学生:佳梦学号:2012117282实验名称: 设计一个 M+N分频器1、实验步骤创建工程、创建文件、编译工程、观察RTL视图、仿真2、 VerilogHDL代码装订线module div5_7 (clk,out);input clk;output out;reg out;reg 3:0 cout1;reg 3:0 cout2;always (posedge clk)beginif (cout14d11)begincout1=cout1+1;if (

25、cout1=4b0100)out=out;endelsebegincout1=0;out=out;endendendmodule3、 RTL 视图cout13.0Add0SELA3.04 h0 -DATAA+OUT0B3.0DATAB4 h1 -ADDERLessThan0MUX21A3.0B3.04 hB -LESS_THANclk4、仿真结果cout13.0Equal0PREA3.0DQ=outreg0B3.04 h4 -0PREoutENA0DQEQUAL1CLR1out1ENAout0CLR可编程逻辑器件设计实验报告实验名称: 第三部分: VerilogHDL 中级实验实验目的: 加深

26、理解,熟练操作实验时间:2015 年地点:803 实验室学生:佳梦学号:2012117282实验名称: 设计一个 17 分频器1、实验步骤创建工程、创建文件、编译工程、观察RTL视图、仿真2、 VerilogHDL代码装订线module div_17(clk,out);input clk;output wire out;reg out1,out2;reg 4:0 temp1;reg 4:0 temp2;assign out=out1|out2;always (posedge clk )beginif(temp14d9)temp1=temp1+1;elsebegintemp1=0;out1=ou

27、t1;endendalways (negedge clk)beginif(temp24d9)temp2=temp2+1;elsebegintemp2=0;out2=out2;endendendmodule3、 RTL视图Add0A4.05 h00 -B4.0+5 h01 -ADDERAdd1A4.05 h00 -B4.0+5 h01 -ADDERtemp14.0SELDATAAOUT0DATABMUX21temp24.0SELDATAAOUT0DATABMUX21temp14.0PREDQENACLRtemp24.0PREDQENACLRLessThan0A4.0B4.05 h09 -LESS

28、_THANLessThan1A4.0B4.05 h09 -LESS_THANout1PREout0DQoutENACLRout2PREDQENACLRclk4、仿真结果可编程逻辑器件设计实验报告实验名称: 第四部分: ModuleSim 基础仿真实验实验目的: 编写一个测试文件实验时间:2015 年地点:803 实验室学生:佳梦学号:2012117282实验名称: 对 1 位全加器的仿真1、实验步骤创建工程、创建文件、编译工程、观察RTL视图、仿真2、 VerilogHDL 代码module full_add(a,b,cin,sum,cout);input a,b,cin;output sum

29、,cout;装assign sum=abcin;assign cout=(a&b)|(b&cin)|(cin&a);endmodule3、软件测试代码订timescale 1ns/1nsmodule full_add_tb;reg a,b,cin;wire sum,cout;线parameter delay=100;full_add u1 (a,b,cin,sum,cout);initialbegina=0;b=0;cin=0;#delay a=1;b=0;cin=0;#delay a=0;b=1;cin=0;#delay a=1;b=1;cin=0;#delay a=0;b=0;cin=1;

30、#delay a=1;b=0;cin=1;#delay a=0;b=1;cin=1;#delay a=1;b=1;cin=1;#delay;endendmodule4、仿真结果可编程逻辑器件设计实验报告实验名称: 第四部分: ModuleSim 基础仿真实验实验目的: 编写一个测试文件实验时间:2015年地点:803 实验室学生:佳梦学号:2012117282实验名称: 编写一个测试文件,完成对四选一数据选择器的仿真1、实验步骤创建工程、创建文件、编译工程、观察RTL视图、仿真2、 VerilogHDL代码装订线module mux4_1 (in0,in1,in2,in3,s0,s1,out)

31、;input s0,s1;input in0,in1,in2,in3;output out;reg out;always(in0,in1,in2,in3,s0,s1)begincase(s0,s1)2b00:out=in0;2b01:out=in1;2b10:out=in2;2b11:out=in3;default:out=1bz;endcaseendendmodule3、软件测试代码timescale 1ns/1nsmodule sjxz_t;reg s0,s1,in0,in1,in2,in3;mux4_1 u1(in0,in1,in2,in3,s0,s1,out);initialbegin

32、#100 in0=1;in1=1;in2=1;in3=1;s0=0;s1=0;#100 in0=1;in1=1;in2=1;in3=1;s0=1;s1=0;#100 in0=1;in1=1;in2=1;in3=1;s0=0;s1=1;#100 in0=1;in1=1;in2=1;in3=1;s0=1;s1=1;endendmodule4、仿真结果可编程逻辑器件设计实验报告实验名称: 第四部分: ModuleSim 基础仿真实验实验目的: 编写一个测试文件实验时间:2015年地点:803 实验室学生:佳梦学号:实验名称: 编写一个测试文件,完成对模201211728260 计数器的仿真1、实验步

33、骤创建工程、创建文件、编译工程、观察RTL视图、仿真2、 VerilogHDL代码装订线module m_60(clk,load,reset,a,cnt,cout);input clk,load,reset;input 5:0 a;output cout;output 5:0t;reg 5:0t;reg cout;always(posedge clk or negedge reset)beginif(!reset)t=6b00_0000;else if(load)t=a;elsebeginif(cnt6d59)begint=cnt+1;cout=0;endelsebegincout=1;t=6

34、b00_0000;endendendendmodule3、软件测试代码timescale 1ns/1nsmodule sjxz_t;reg s0,s1,in0,in1,in2,in3;mux4_1 u1(in0,in1,in2,in3,s0,s1,out);initialbegin#100 in0=1;in1=1;in2=1;in3=1;s0=0;s1=0;#100 in0=1;in1=1;in2=1;in3=1;s0=1;s1=0;#100 in0=1;in1=1;in2=1;in3=1;s0=0;s1=1;#100 in0=1;in1=1;in2=1;in3=1;s0=1;s1=1;end

35、endmodule4、仿真结果可编程逻辑器件设计实验报告实验名称: 第四部分: ModuleSim 基础仿真实验实验目的: 编写一个测试文件实验时间:2015年地点:803 实验室学生:佳梦学号:2012117282实验名称: 编写一个测试文件,完成对模60BCD码计数器的仿真1、实验步骤创建工程、创建文件、编译工程、观察RTL视图、仿真2、 VerilogHDL代码装订线module bcdm_60(clk,qout,a,reset,load);input clk,reset,load;input 7:0 a;output reg 7:0 qout;always(posedge clk or

36、 negedge reset)beginif(!reset)qout=8b0000_0000;else if(load)qout=a;else if(qout3:09)qout=qout+1;else if(qout7:45)beginqout7:4=qout7:4+1;qout3:0=4b0000;endelse qout7:0=8b0000_0000;endendmodule3、软件测试代码timescale 1ns/1nsmodule bcdm_60t;reg clk,reset,load;reg 7:0 a;wire 7:0 qout;parameter delay=100;integ

37、er i;bcdm_60 u1(clk,qout,a,reset,load);initialbeginclk=0;reset=0;#delay clk=clk;reset=1;#delay clk=clk;reset=0;#delay clk=clk;reset=0;#delay clk=clk;reset=1;for(i=0;i200;i=i+1)#delay clk=clk;#delay;endendmodule4、仿真结果可编程逻辑器件设计实验报告实验名称: 第四部分: ModuleSim 基础仿真实验实验目的: 编写一个测试文件实验时间:2015年地点:803 实验室学生:佳梦学号:实验名称: 编写一个测试文件,完成对加20121172824b

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。