采用SAR结构的8通道12位ADC设计

采用SAR结构的8通道12位ADC设计

《采用SAR结构的8通道12位ADC设计》由会员分享,可在线阅读,更多相关《采用SAR结构的8通道12位ADC设计(4页珍藏版)》请在装配图网上搜索。

1、采用SAR结构的8通道12位ADC设计引言ADC是模拟系统与数字系统接口的关键部件,长期以来一直被广泛应用于通信、军事及消费电子等领域, 随着计算机和通信产业的迅猛发展,ADC在便携式设备上的应用发展迅速,正逐步向高速、高精度和低功耗的方向发展。目前市场上占统治地位的 ADC的类型主要包括:逐次逼近型(SAR、-型、 流水线型。工-型可以实现很高的分辨率,流水线型可以保证很高的采样速率,这两种体系结构都是为了满足某种特定需求的纵向市场而设计的。SAR ADC是采样速率低于5MSPS的中高分辨率应用的常见结构,由于其实质上采用的是二进制搜索算法,内部电路可以运 行在几MHz采样速率主要由逐次逼近

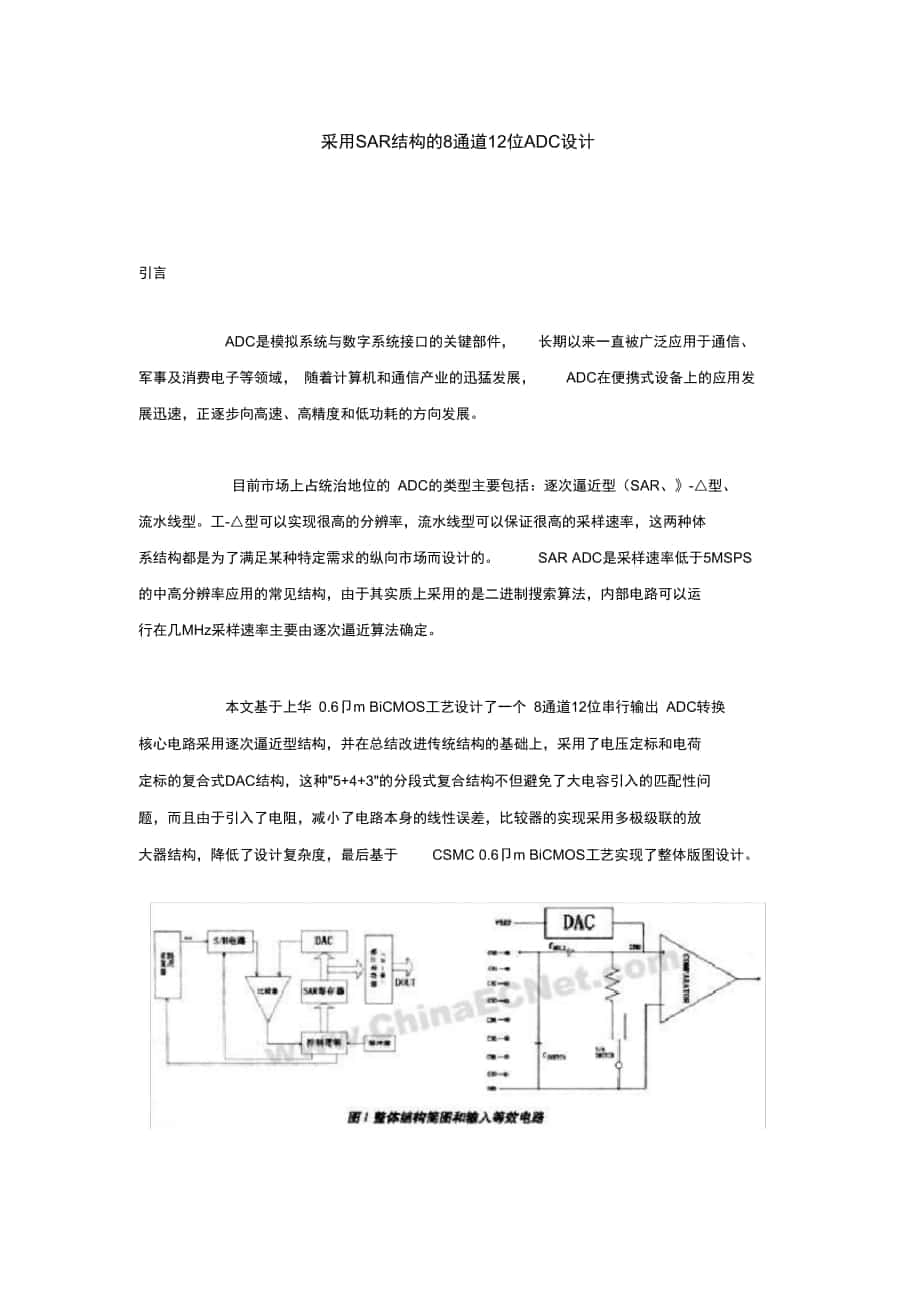

2、算法确定。本文基于上华 0.6卩m BiCMOS工艺设计了一个 8通道12位串行输出 ADC转换核心电路采用逐次逼近型结构,并在总结改进传统结构的基础上,采用了电压定标和电荷定标的复合式DAC结构,这种5+4+3的分段式复合结构不但避免了大电容引入的匹配性问题,而且由于引入了电阻,减小了电路本身的线性误差,比较器的实现采用多极级联的放大器结构,降低了设计复杂度,最后基于CSMC 0.6卩m BiCMOS工艺实现了整体版图设计。系统结构SAR ADC电路结构主要包含五个部分,采样保持电路,比较器、 DAC逐次逼近寄存器和逻辑控制单元,转换中的逐次逼近是按对分原理,由控制逻辑电路完成的,其工 作过

3、程如下:启动后,控制逻辑电路首先把逐次逼近寄存器的最高位置1,其他位置 0,将其存储到逐次逼近寄存器,然后经数模转换后得到一个电压值(大小约为满量程输出的一半)。这个电压值在比较器中与输入信号进行比较,比较器的输出反馈到DAC并在下一次比较前对其进行修正。即输入信号的抽样值与DAC的初始输出值相减,余差被比较器量化,量化值再来指导控制逻辑是增加还是减少DAC的输出,然后,再次从输入抽样值中减去这个新的DAC输出值。不断重复这个过程,直至完成最后一位数字的实现,由此可见,这种 数据的转变始终处于逻辑控制电路的时钟驱动之下,逐次逼近寄存器不断进行比较和移位 操作,直到完成最低有效位(LSB)的转换

4、,这时逐次逼近寄存器的各位值均已确定,转换 操作完成。由于本设计针对的是串行多路通道转换技术,所以本文在SAR ADC基本结构的基础上,在模拟输入的前端加入多路复用模块,并在输出后端加入并串转换电路。为实现信号的快速精确转换,SAR ADC中重要部件是采样保持电路,比较器和DAC等效输入电路如图1所示,在获取数据期间,被选信道作为输入给电容CHOLD充电,获得时间结束后,T/H开关打开,电荷维持在CHOLDh作为信号样本,与DAC中产生的模拟 信号进行比较,将比较结果输入并 /串输出寄存器,在三态总线控制下输出数字位。电路设计与实现采样/保持电路的性能高低限定了整个 ADC的速度和精度,在设计

5、中采用双差 分底板采样技术,双差分结构以获得优良的AC性能,另外底板采样技术的应用也极大的减少了电荷注入、时钟馈通以及有限带宽所造成的误差。优化了整体性能。其中比较器的实 现采用 3 个放大级联结构,这样不仅极大的提高了增益,而且减小了比较器的设计难度, 提高了电路性能,下面重点讲述DAC的设计与实现。SAR ADC的速度和分辨率主要受反馈电路中DAC的速度、分辨率和线性的限制,精确设计DAC是本次设计的重点和关键,传统的SAR ADC多采用简单的电阻分压式或电容电荷型结构来实现,电阻分压式转换器的优点是只需要用到一种电阻,容易保证制造精度, 即使电阻出现较大的误差,也不会出现非单调性。但 n

6、 位二进制输入的电阻分压式数模转 换器需要 2n 个分压电阻以及同样数量的模拟开关,所以随着位数的增加,其所需元器件的 数量会呈几何级数增加,这是它的缺点,单独用这种结构来做一个DAC的情况比较少见,但是它却在8位以下的SAR ADC中常用到,电容电荷型 DAC的优点是精度较高,但缺点是 面积大,对寄生电容敏感,而且还需要相连时钟,增加了设计制造的复杂度。本文设计的DAC采用复合结构,由于本芯片是一个12位精度的ADC要求DAC也要达到 12位精度,而且对于位数较高的转换器,从芯片面积和性能方面综合考虑,组合结构较单一结构优势显著,因而本文采用5+3+4复合结构实现,即高 5位MSB采用电容网

7、络实现,中间3位采用电子网络,而低 4位LSB仍用电容网络实现,这样设计避免了不同 结构实现上的不足,结合了各自的优点,较好的实现电路设计目标。此DAC的优点是具有一定的单调性。因为电阻串本质上是单调的,而且 3个数字位只有一种阻值的电阻,不存 在电阻失配问题,电阻串不需要预充电,转换速度比电容阵列的转换速度快,但芯片占用 面积较大, 电容网络最多只需满足 5位数字位对应的电容精度要求便可实现 1 2位转换匹配, 所以在分配每段位数时,本文在芯片面积和转换速度之间进行了折中考虑,单独对DAC进行仿真得到其建立时间仅为12ns。设计仿真根据电路功能及指标要求,在Cade nee环境下用Hspic

8、e对电路进行仿真,通过控制逻辑精确控制,最后实现 12位数字的转换结果,图 2 为选择第 8通道对 2.5V 电压 进行转换的输出波形,实现了模拟信号到数字信号的正确转换,12位ADO的工作温度范围为-55 C -125 C,访问条件为 VDD=5.0V, VSS=0V VREF=4.096V, VAGND=0,最后基于 CSMC 0.6卩m BiCMOS工艺完成了版图设计,面积为 2.5 x 2.2mm26.al.a*rt-te 心以rrjL 2TL伽Mu厲?篥賈通遇科宅颅进厅着揍的廉缶遊形结语本文基于CSMC 0.6卩m BiCMOS工艺设计实现了一个 12位串行输出 ADC采用 电压定标和电荷定标组合式数模转换器技术,比较器的实现采用多极级联放大器形式,通 过合理的时序控制,实现了较好的性能,转换速率为7.5卩s,正常工作电流2.8mA,增益误差小于2LSB,线性误差小于1个LSB,最后版图面积为2.5 X 2.2mm2此转换器对于消费 电子、汽车电子及便携式产品等方面应用是具有较好性价比的选择。

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。