Verilog流水灯实验报告

Verilog流水灯实验报告

《Verilog流水灯实验报告》由会员分享,可在线阅读,更多相关《Verilog流水灯实验报告(6页珍藏版)》请在装配图网上搜索。

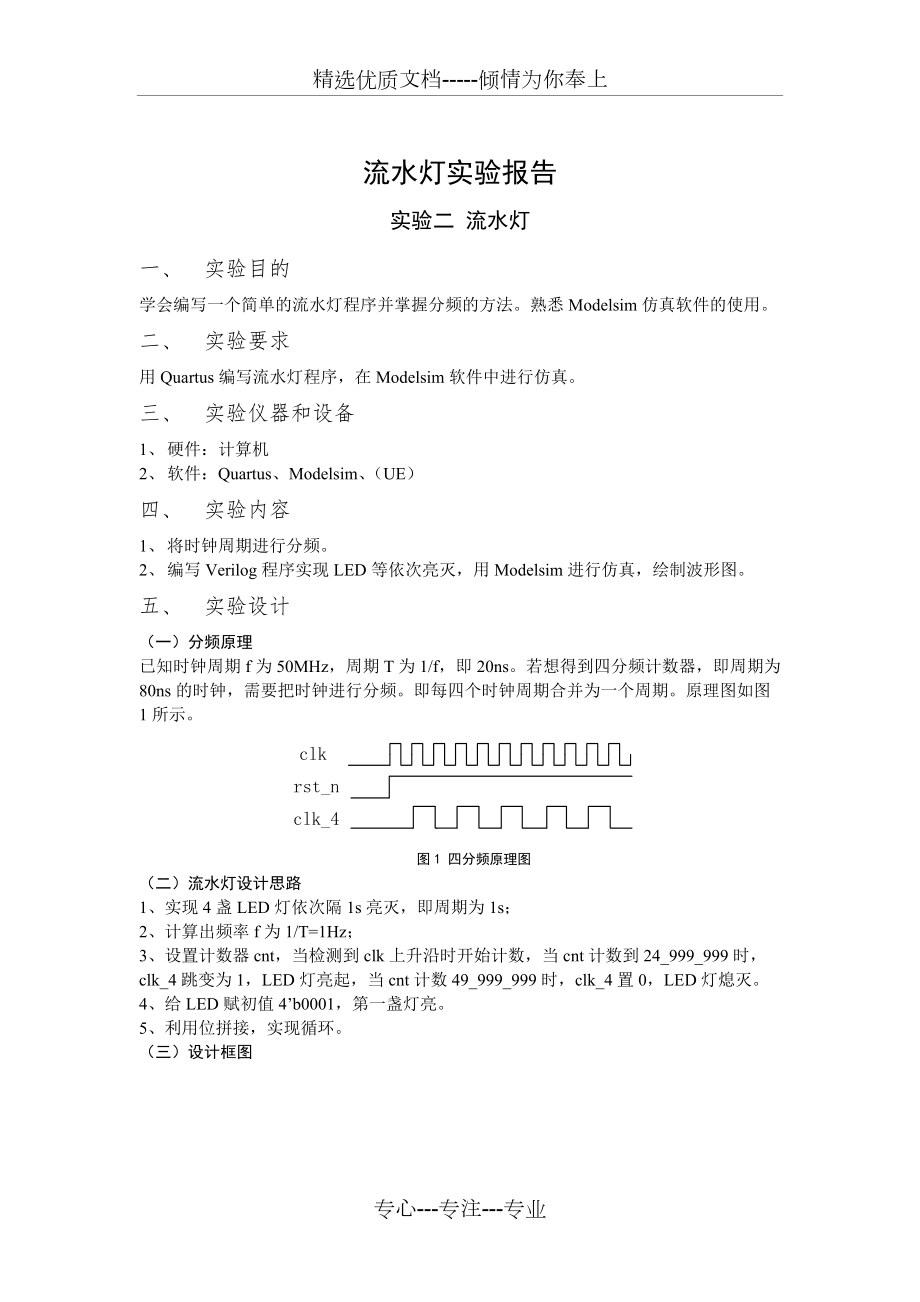

1、精选优质文档-倾情为你奉上流水灯实验报告实验二 流水灯一、 实验目的学会编写一个简单的流水灯程序并掌握分频的方法。熟悉Modelsim仿真软件的使用。二、 实验要求用Quartus编写流水灯程序,在Modelsim软件中进行仿真。三、 实验仪器和设备1、 硬件:计算机2、 软件:Quartus、Modelsim、(UE)四、 实验内容1、 将时钟周期进行分频。2、 编写Verilog程序实现LED等依次亮灭,用Modelsim进行仿真,绘制波形图。五、 实验设计(一)分频原理已知时钟周期f为50MHz,周期T为1/f,即20ns。若想得到四分频计数器,即周期为80ns的时钟,需要把时钟进行分频

2、。即每四个时钟周期合并为一个周期。原理图如图1所示。图1 四分频原理图(二)流水灯设计思路1、实现4盏LED灯依次隔1s亮灭,即周期为1s;2、计算出频率f为1/T=1Hz;3、设置计数器cnt,当检测到clk上升沿时开始计数,当cnt计数到24_999_999时,clk_4跳变为1,LED灯亮起,当cnt计数49_999_999时,clk_4置0,LED灯熄灭。4、给LED赋初值4b0001,第一盏灯亮。5、利用位拼接,实现循环。(三)设计框图图2 设计基本框图(四)位拼接的用法若输入a=4b1010,b=3b101,c=4b0101,想要使输出d=5b10001用位拼接,符号“ ”:d=b

3、2:1,c1,a2:1即把b的低12位10,c的低1位0,a的低12位01拼接起来,得到10 0 01。流水灯4b00014b00104b01004b1000相当于把低三位左移,并最高位放在最低位。用位拼接可写为:led=led2:0, led3; 低三位 最高位六、 实验方法和步骤(一)时钟分频1、 编写分频程序。2、 编写测试程序。3、 进行仿真,波形如图3所示。图3 分频仿真结果(二)流水灯1、编写分频程序。3、 编写测试程序。3、进行仿真,为了节约时间和方便观察波形,将计数器值分别改为24、49跳转。波形如图4所示。图4流水灯仿真结果七、 实验参考程序(一) 时钟分频1、程序文件mod

4、ule div_clk(/模块名与文件名一致。定义端口列表,inputwireclk,/输入线型inputwirerst_n,output regclk_4/输出定义为寄存器型);reg3:0cnt;/中括号定义位宽,定义中间变量cntalways(posedge clk)if(rst_n=0)cnt=0;/复位为0,计数器也为0else if(cnt=3)/当计数器=3时清零(可用else if)cnt=0;elsecnt=cnt+1;/计数器自加1always(posedge clk)if(rst_n=0)clk_4=0;/复位为0.clk_4为0else if(cnt=1)clk_4=1

5、;/当计数器为1时,时钟跳变为1else if(cnt=3)clk_4=0;/当计数器为3时,时钟跳变为0endmodule2、测试文件timescale1ns/1nsmodule tb_div_clk();regclk;regrst_n;wire clk_4;initialbeginclk=0;rst_n=0;#100rst_n=1;endalways#5clk=clk;div_clk div_clk_inst(.clk(clk),.rst_n(rst_n),.clk_4(clk_4);endmodule(二) 流水灯1、 程序文件module LSD(/模块名与文件名一致。定义端口列表,i

6、nputwireclk,/输入线型inputwirerst_n,outputreg3:0led);reg25:0cnt;/中括号定义位宽,定义中间变量cntregclk_4;always(posedge clk)if(rst_n=0)cnt=0;/复位为0,计数器也为0else if(cnt=49_999_999)/当计数器=时清零(可用else if)cnt=0;elsecnt=cnt+1;/计数器自加1always(posedge clk or negedge clk)/异步复位if(rst_n=0)clk_4=0;/复位为0.clk_4为0else if(cnt=24_999_999)c

7、lk_4=1;/当计数器为时,时钟跳变为1else if(cnt=49_999_999)clk_4=0;/当计数器为时,时钟跳变为0elseclk_4=clk_4;always(posedge clk_4 or negedge clk_4)if(rst_n=0)led=4b0001;elseled=led2:0,led3;/位拼接endmodule2、 测试文件timescale1ns/1nsmodule LSD();regclk;regrst_n;regcnt;wire led;initialbeginclk=0;rst_n=0;#100rst_n=1;endalways#5clk=clk;

8、LSD LSD_inst(.clk(clk),.rst_n(rst_n),.led(led);endmodule八、 实验小结1、 做实验要养成良好的习惯,每次做实验时,都要建立一个新的文件夹存放实验所需的程序文件,为仿真时添加文件做准备,也方便以后的查找和使用。2、 写程序前要想清楚电路实现原理,根据所学数电知识对各个元器件进行控制。3、 写程序时注意排版美观整洁,同时注意添加注释。4、 注意程序中模块名要和文件名一致,否则程序报错,无法编译通过。5、 仿真时,可以选择不同的进制。在想要更改的地方右键,选择【Radix】,其中【Binary】为二进制。如图5所示。图5更改进制6、 在流水灯仿真时,LED灯的波形一开始是错误的,因为程序中只检测了上升沿always(posedge clk),加上下降沿检测always(posedge clk or negedge clk),即可解决问题,成功绘制波形图。专心-专注-专业

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。