常用时序分析报告SDC

常用时序分析报告SDC

《常用时序分析报告SDC》由会员分享,可在线阅读,更多相关《常用时序分析报告SDC(52页珍藏版)》请在装配图网上搜索。

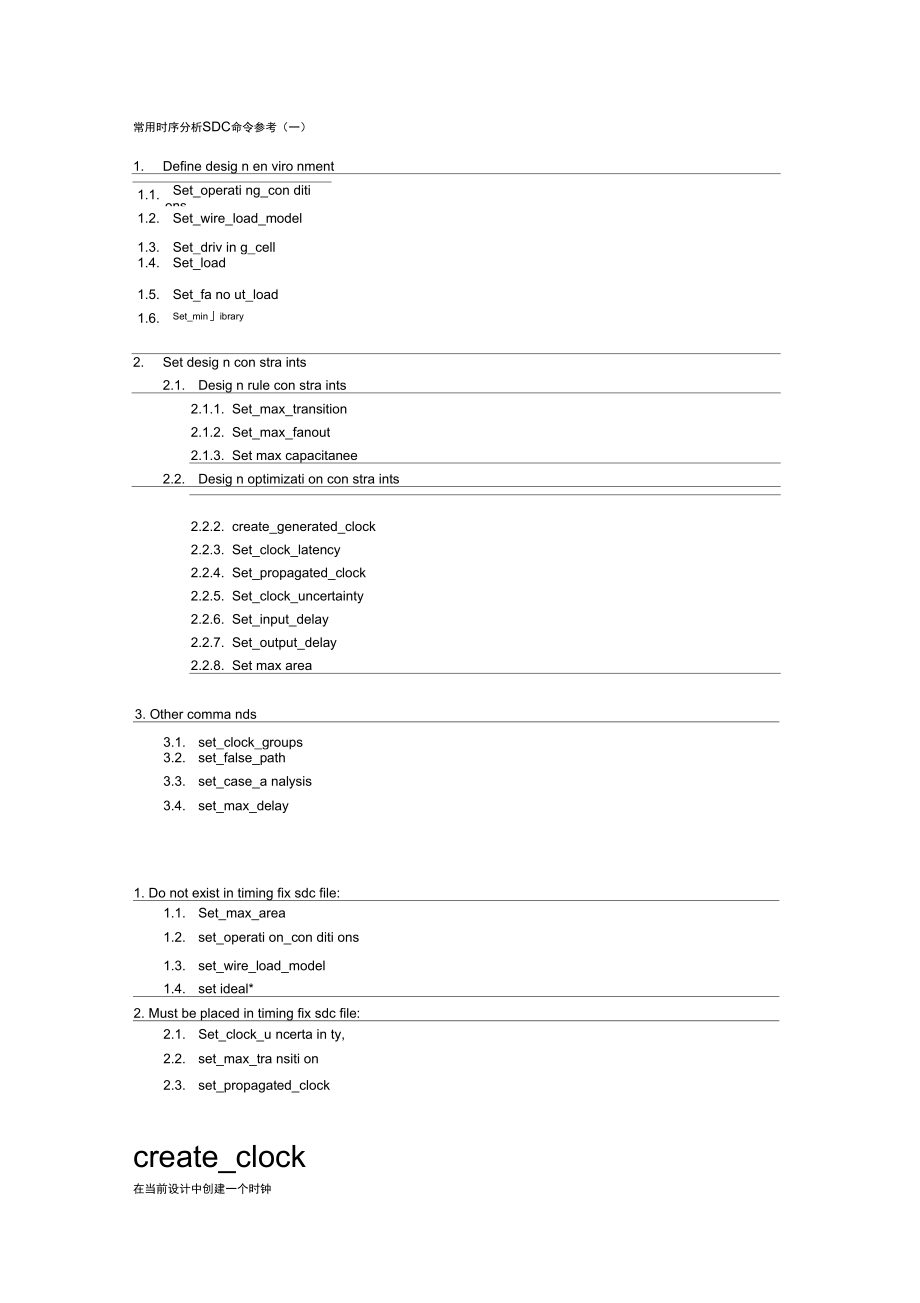

1、常用时序分析SDC命令参考(一)1. Define desig n en viro nment1.1.Set_operati ng_con diti ons1.2.Set_wire_load_model1.3.Set_driv in g_cell1.4.Set_load1.5.Set_fa no ut_load1.6.Set_minibrary2. Set desig n con stra ints2.1. Desig n rule con stra ints2.1.1. Set_max_transition2.1.2. Set_max_fanout2.1.3. Set max capacit

2、anee2.2. Desig n optimizati on con stra ints2.2.2. create_generated_clock2.2.3. Set_clock_latency2.2.4. Set_propagated_clock2.2.5. Set_clock_uncertainty2.2.6. Set_input_delay2.2.7. Set_output_delay2.2.8. Set max area3. Other comma nds3.1.set_clock_groups3.2.set_false_path3.3.set_case_a nalysis3.4.se

3、t_max_delay1. Do not exist in timing fix sdc file:1.1.Set_max_area1.2.set_operati on_con diti ons1.3.set_wire_load_model1.4.set ideal*2. Must be placed in timing fix sdc file:2.1.Set_clock_u ncerta in ty,2.2.set_max_tra nsiti on2.3.set_propagated_clockcreate_clock在当前设计中创建一个时钟语法:status create_clock -

4、n ame clock_ name -addsource_ojbects -period period_value -waveform edge_list数据类型:clock_ name字符source_objects列表period_value浮点edge_list列表参数:-n ameclock_ name指定时钟名称。如果你不使用该选项,时钟名称将会与第一个时钟源在source_objects指定的一样。如果你没有使用souce_objects ,你就必须使用本选项,它会创建一个与端口或接脚无关的虚拟时钟。本选项与source_objects一起使用可以为时钟增加一个描述性的名称。如果你

5、使用-add选项,你必须使用-name选项,并且要为有相同源的时钟分配不同的名 称。(注解:-name如果省略,就必须要指定创建时钟的节点。这也是默认的做法。不指定时钟创建节点的意思就是指创建一个虚拟时钟。如果既指定了时钟节点,有写了-name选项,这个-name可以认为是一个 alias。)(疑难点:虚拟时钟,-add选项)-add指明是否将该时钟加到已存在的时钟中或将其覆盖。使用本选项抓取有相同源不同波形, 进行同时分析的复合时钟。你使用该选项时,必须使用-name选项。定义在相同源接脚或端口的复合时钟相比一个单一时钟,会导致更长的运行时间和更高的存占用。因为时序综合引擎必须搜索所有开始(

6、launch)和截取(capture)组合的可能性。使用set_false_path命令限制不期望的组合。该选项在默认为关闭,除非复合时钟分析的相关变量 timing_enable_multiple_clocks_pre_reg被设为 true。(疑难点:timing_enable_multiple_clocks_per_reg, -add)(注意,这是 create_clock命令,它也是有-add选项的。)(举一个简单的例子,对于一个输入时钟端口,你创建了两个时钟。第二个时钟创建的 时候使用了 -add选项。则,看timing路径的时候,就会发现clk1和clk2互相检查的情况。这种情况是

7、不真实的。需要使用false path把它们进行设置。这属于两时钟物理互斥的畴。)source_objects指定应用于时钟的接脚或端口的列表。如果你没有使用本选项,你必须使用-nameclock_ name,它会创建一个与接脚或端口无关的虚拟时钟。如果你指定的时钟已经在接脚上了,旧的时钟会被取代,除非你增加-add选项。-period period_value以库时间单位指定时钟波形的周期-waveformedge_list以库时间单位指定整个时间周期中时钟的上升或下降沿时间。列表中第一个时间是上升转换,通常第一个上升转换在时间零点之后。这里增加次数必须是偶数,并且它们假定为交替的上升和下降

8、时间。数值上,为一个完整时钟周期。如果-waveform edge_list没有设定,但有 -period period_value ,默认情况,波形假定为一个0.0上升沿和一个 period_value/2 下降沿。(疑难点:通过-waveform 把波形给画岀来。但是, -period 是必须要写的。也就是说, 你可以只使用-period 指定一个时钟周期。默认是50%占空比,且先1后0。如果想创建占空比不是50%的时钟,就要通过-waveform来描述了,第一个上升的位置在什么时刻, 下降的位置在什么时刻。)(和create_generate_clock中的-edge选项很容易混淆!)描

9、述:create_clock命令在当前设计中创建一个时钟。该命令在当前设计中定义指定的source_objects作为时钟源。一个接脚或端口可以成为一个单时钟源。如果source_objects 没有指定,但clock_name给定,一个虚拟时钟会被创建。一个虚拟时钟可以被创建,代表一个片 外时钟用于描述输入或输岀延迟。更多关于输入和输岀延迟的信息,可以阅读set_i nput_delay和口 set_oupt_delay参考。时钟影响到时钟网络的属性,比如dont_touch_network,fix_hold 和propagated_clock 。使用create_clock在已存在的时钟上

10、会覆盖时钟上已有的属性。create_clock也同时定义时钟波形。时钟允许每个周期多脉冲形式。建立和保持路径延迟是从时钟波形路径的起点到终点自动衍生的。 fix_hold 属性(用 set_fix_hold 设定)指导 compile 修复时钟保持(hold) 错误。默认状态,时钟对应一组路径。该组与时钟相关的终点用于估算函数的计算。要将时钟从分配的组中删除,使用 group_path命令分配时钟到另一个组或默认路径组。更多的信息可参考 group_path 命令帮助。新的时钟有理想时序,不能通过时钟网络传播延迟。使用set_propagated_clock 命令让时钟能够进行延迟传播。要添

11、加偏差(skew)和不确定因素(uncertainty )到理想波形中,使用set_clock_latency 或 set_clock_uncertainty命令。显示当前设计中所有时钟源信息,使用report_clock 命令。得到时钟源列表,使用get_clocks命令。返回所有与特定时钟相关的序列单元,使用all_registers命令。取消create_clock ,使用 remove_clock 命令。多条件多模式支持:该命令仅使用当前方案中的信息。例:【不规则占空比】在端口 PHI1创建时钟周期为 10, 上升在5.0,下降在9.5.create_clock “ PHI1 ” pe

12、riod 10 waveform 5.0 9.5【特殊】在端口 PHI2创建时钟周期为 10,下降在5,上升在10create_clock“PHI2-period 10- waveform 10 15【周期多脉冲】在接脚u12/Z创建时钟CLK,周期25,下降在0.0,上升在5.0,下降在 10.0,上升在 15.0create_clock“ u13/Z”-name “ CLK- period 25-waveform 5 10 15 25【典型,但是是一个虚拟时钟】创建一个虚拟时钟 PHI2,周期10,上升在0.0,下降在5.0create_clock - name PHI2”- period

13、 10- waveform 0.0 5.0【更为复杂】创建多源复合波形时钟create_clock - name “ clk2 ”- period 10-clkge n1/Z clkge n2/Z clkge n3/Z(注解:相当于在三个端子上都创建了同一个形态的时钟。这个时钟具有周期10,在0时刻上升,在2时刻下降,在4时刻上升,在 6时刻下降。在10时刻上升. 也就是说,10时刻的 动作,等同于0时刻。后面的话就是周期的复制了。)更多:all_clocks, all_registers, check_ti ming, compile, curre nt_desig n, get_clock

14、s, group_path, remove_clock, reset_desig n, set_clock_late ncy, set_clock_u ncerta in ty, set_do nt_touch_ network, set_fix_hold, set_max_delay, set_output_delay, set_propagated_clockcreate_ge nerated_clock创建一个生成时钟语法:stri ng create_ge nerated_clock-n ame clock_ name-addsource_objects-source master_p

15、 in-divide_by divide_factor | multiply_by multiply_factor-duty_cycle perce nt-in vert-pre in vert-edges edge_list-dege_shift dege_shift_list-comb in ati on al数据类型:clock_ name字符source_objects列表master_p in列表clock字符divide_factor整数multiply_factor整数perce nt浮点edge_list列表edge_shift_list列表参数:-n ame clock_ n

16、ame-source 设定的指定生成时钟的名称。如果你不使用本选项,时钟接受与第一个时钟的 名称相同的名称。如果你使用-add选项,你必须使用-name选项,相同的名称。-add 指定是否增加这个时钟到已经存在的时钟中或将其覆盖。使用本选项去截取相同源的复 合时钟。理想状态,一个生成时钟必须设定为每个时钟扇岀的源接脚。如果你使用该选 项,必须同时使用-n ame选项。定义相同源接脚或端口的复合时钟,会增加运行时间和需要更多的存,因为时序综合引 擎搜索启动与截取组合的所有可能。使用set_false_path取消不希望有的组合。默认状态,忽略该选项,除非将timing_enable_multip

17、le_clock_per_reg变量设为true 打开复合时钟分析.source_objects指定一组端口或接脚定义为要产生的生成时钟源-source master_p in指定主时钟接脚,可以是一个主时钟源接脚或被主时钟驱动的一个接脚,并且是驱动生 成时钟定义的接脚。主接脚的时钟波形用于驱动生成时钟波形。-master_clock clock如果多个时钟扇入这个主接脚,指定主时钟用于这个生成时钟。-divider_by divide_factor指定频率被除数。如果divide factor为2,生成时钟周期是主时钟周期的两倍。-multiply_by multiply_factor指定频

18、率倍数。如果 multiply_factor 为3,则生成时钟周期为原先的三分之一。-duty_cycle perce nt指定倍频使用时的占空比。允许 0-100之间的数值。占空比是高电平脉冲宽度。-in vert反转生成时钟信号,不管主接脚上,源时钟反应或判断(sense)是单因素决定(unate)还是非单因素决定(non-un ate)(遇到倍频时)。-prei nvert创建一个生成时钟基于反转的时钟信号,仅当主接脚源时钟有非单因素决定反应,或生成时钟不被反转,仅当该选项没有被指明时。-invert与-prei nvert不同之处在于,-in vert先创建生成时钟后反转信号,而pre

19、i nvert是先反转信号,再创建生成时钟。-edges edge_list指定正整数列表,代表形成生成时钟沿的源时钟沿。沿解释为交替变化的上升和下降沿,并且每个沿不小于它之前的沿。沿的数值必须是不小于3的奇数,用来创建一个完整的生成时钟的波形。第一个沿必须大于或等于1。比如,1代表第一个源边沿,2代表第二个源边沿,依次类推。-edge_shift edge_shitf_list指定浮点数列表代表偏移量,指定的沿经过变化产生最终的生成时钟波形,单位与库时 钟单位相同。指定的沿偏移量必须等于沿指定的数值。数值可以为正或负。正数表示延 后,负的表示提前。比如, 1代表相应的沿被延后了 1个时间单位

20、。-comb in ati onal指定源滞后路径,作用于某个类型的生成时钟,其包含主时钟传播组合路径上的逻辑。 源滞后路径不会通过序列单元的时钟接脚,透明锁存器数据接脚,或其他生成时钟的源 接脚。描述:create_ge nerated_clock命令在当前设计中创建一个生成时钟。该命令定义一个对象列表作为当前设计生成时钟源。你可以指定接脚或端口作为生成时钟对象。命令同时指定被生成时钟源。使用该命令的优势在于,无论何时主时钟发生改变,生成时钟也同时发生改变。生成时钟可以进行变频处理,降低频率时使用-divide_by 选项,增加频率时使用 -multiply_by选项,沿派生使用-edge选

21、项。另外,频率在除或乘时也可以用-invert 选项进行反转。沿派生时钟的沿偏移使用-edge_shift 选项。-edge_shift 使用在对沿的故意偏移,而非时钟滞后。如 果生成时钟使用 divide_factor 是2的幕,主时钟上升沿被用来决定生成时钟的沿。如果 divider_factor 不是2的幕,则是从对主时钟沿尺寸改变得来。对已有的 generated_clock使用 create_generated_clock,会覆盖已有的 generated_clock属性。gen erated_clock 在时序分析时被扩展为真实的时钟。以下命令能够引用gen erated_cloc

22、k:set_clock_late ncyset_clock_u ncerta intyset_propagated_clockset_clock_tra nsiti on显示有关生成时钟的信息使用report_clock 命令。多条件多模式支持:该命令仅使用当前方案中的信息。例:创建频率-divide_by 2的生成时钟create_generated_clock- divide_by 2- source CLK get_pins foo创建频率-divide_by3的生成时钟。主时钟周期为 30,主波形为24 36,则生成时钟周期为90,波形为72 108create_gneraged_cl

23、ock - divide_by 3- source CLK get_pins div3/Q创建频率-multiply_by 2的生成时钟,占空比为60%。create_generated_clock- multiply_by 2- duty_cycle 60- source CLK get_pins fool创建频率-multiply_by3的生成时钟,占空比不变。如果主时钟周期为30,主波形为24 36,生成周期为10,波形为8 12create_gnerated_clock - multiply_by 3- source CLK get_pins div3/Q创建生成时钟沿为主时钟的1,3

24、,5沿。如果主时钟周期为30 ,波形24 36,生成时钟周期为60 ,波形为24 54create_generated_clock- edges 1 3 5- source CLK get_pints foo2与上个例子相似,但沿偏移1个单位。如果主周期为30,主波形为24 36,生成时钟周期为60 , 波形为25 55create_generated_clock- edges 1 3 5- edge_shift 1 1 1- source CLK get_pinsfoo2创建一个反转时钟create_generated_clock- divider_by 2- invert更多check_t

25、i ming, create_clock, get_ge nerated_clocks, remove_ge nerated_clock,report_clock, set_clock_late ncy, set_clock_u nertain ty, set_propagated_clock, timi ng_e nable_multiple_clocks_per_regset_clock_groups指定设计中,时钟组互相排斥或彼此异步。因此,这些时钟之间的路径不会在时序分析时被考虑。语法:Boolea n set_clock_groups-physically_exclusive|-lo

26、gically_exclusive|-as yn chr onous-allow_paths-n ame n ame-group clock_list参数:-physicall_exclusive指定时钟组在物理上彼此排斥。物理排斥时钟不能同时存在在实际物理设计中。比如多个时钟定义在同一个源接脚。-physical_exclusive, -logically_exclusive和-as yn chro nous选项是相互排斥的,你只能选择其中一个。-logicall_exclusive两个时钟排斥类型,一个是物理排斥,另一个是逻辑排斥。逻辑排斥的例子比如MUX多路选择。但如果存在物理路径,就不

27、推荐对多路选择时钟进行排斥设定。-physically_exclusive, -logically_exclusive和口 -as yn chro nous选项是互相排斥的,你只能选择其中一个。-asynchr onous指定时钟组是彼此异步的。两个时钟是异步的如果它们彼此之间没有相位关系。信号完 整性分析使用一个无限到达窗口给干扰源,除非所有到达窗口的受噪声干扰的连线和干 扰源的连线由同步时钟控制。-physically_exclusive, -logically_exclusive和-as yn chro nous选项是互相排斥的,你只能选择其中一个。-allow_paths允许在指定的时

28、钟组之间进行时序分析。如果这一选项没有被使用,在时钟之间的时序 分析会被禁止。该选项仅可以用于异步时钟组。-n ame n ame指定被创建时钟组的名称。每个命令只能指定一个唯一的名称,这些名称指明指定时钟 组的排斥或异步关系,并且这个名称之后也便于对时钟组定义的删除。默认情况下,命 令创建一个唯一的名称。-group clock_list指定一个时钟列表。你可以多次使用-group选项在一条执行命令中。每个-group循环设定一组时钟,与其他所有时钟组是排斥或异步关系。如果仅有一个组被指定,这意味着该组与其他所有时 钟是排斥或异步的。包含其他时钟的另一个组也同时会产生。无论何时一个新的时钟被

29、 创建,它会自动地加入到这个组。给clock_list替换上你希望的列表。描述:指定设计中的时钟组彼此排斥或异步。这些时钟之间的时序路径在时序分析时不会被考虑,除非使用-allow_paths 选项。一条set_clock_groups执行命令不能对同一时钟定义多次,但可以多次使用该命令把它加入到多个分组中。两个不同类型的互斥时钟在简单时序分析时不会视为不同。然而,信号完整性分析会在时序窗口视逻辑排斥时钟为异步。物理排斥时钟不会被时序窗口分析所考虑。这些排斥或异步时钟之间的路径不会在时序分析时被搜索,除非使用-allow_path 设定。这类似于在时间之间设定禁止路径(false path)。

30、因此你无需人为的再次设定禁止路径。如果一个在两个排斥或异步时钟之间禁止路径已经设定,那么set_clock_groups产生的禁止路径会将其覆盖。其他不会受影响。当时钟彼此异步,在时序窗口重叠分析时,串扰分析忽略之间的时序关系。这一情形也可称为无限窗口重叠。对于同步时钟没有无限窗口重叠,结果会变得乐观。所以当时钟不彼此同步时, 使用 set_clock_groups - asynchronous 是十分重要的。当一些排斥或异步时钟组被定义时,一个生成时钟和它的主时钟默认不在同一分组中。如果有必要,你必须明确地将他们让在一起。如果多个时钟组关系为相同成对时钟而定义,物理排斥有最高优先级,其次是异

31、步和逻辑排斥。取消set_clock_groups 设定,使用remove_clock_groups 命令。报告设计中的时钟分组,使用 report_clock命令力廿-groups 选项。多条件多模式支持: 该命令从当前方案中读取信息例:定义两个异步时钟域set_clock_groups - asynchronous- name g1 - group CLK1 - group CLK2定义一个名为CLK1的时钟作为与其他时钟异步的时钟set_clock_groups- asynchronous- group CLK1显示同时分析多个时钟每个寄存器而无需手工设定禁止路径。假设有两对相互排斥的时

32、钟被复用:CLK1 和 CLK2,CLK3 和 CLK4每对时钟被不同的信号选择,你必须执行两次来同时分析四个时钟:set_clock_groups - logically_exclusive- group CLK1 - group CLK2set_clock_groups - logically _excluseive- group CLK3 - group CLK4如果每对由相同信号选择,则只要一条命令:set_clock_groups - logically_exclusive- group CLK1 CLK3 - group CLK2 CLK4定义 CLK1和CLK2作为物理排斥set

33、_clock_groups physically_exclusive-group CLK1 - group CLK2更多:remove clock groups, report clock, set false path, create clock,create_ge nerated_clockset_false_path删除特殊路径时序约束语法:int set_false_path-rise | -fall -setup | -hold-from from_list| -rise_from rise_fromist|fall_from fall_fromist-through through

34、_list -rise_through rise_through_list -fall_through fall_through_list-to to_list| -rise_to rise_to_list| -fall_to fall_to_list-reset_path数据类型:fromistrise_fromist fall_fromistthroughistrise_through_listfall_throughist列表列表列表列表列表列表to_list列表rise_to_list列表fall_to_list列表参数:-rise标识上升延迟禁止,以路径的终点作为衡量依据。如果你没有

35、指定-rise 或-fall ,上升或下降时序都标识为禁止。-fall标识下降延迟禁止,以路径的终点作为衡量依据。如果你没有指定-rise 或-fall ,上升或下降时序都标识为禁止。-setup标识建立(最大)路径为禁止。-setup取消指定路径的建立检查。如果你没有指定-setup 或-hold,建立和保持都标识为禁止。-hold标识保持(最小)路径为禁止。-hold取消指定路径的保持检查。如果你没有指定-setup或-hold,建立和保持都标识为禁止。-from fromis指定禁止路径的起点(时钟、端口、接脚或单元)。如果你没有指定一个from_list ,所有终点在to_list的路

36、径都被设为禁止。from_list可以包含时钟、接脚或端口。如果你指定一个时钟,所有起点与指定时钟相关的路径都会有影响。如果你指定一个部接脚,接脚必须是一个路径的起点(比如一个触发器的时钟接脚)。如果一个单元被指定,起 点在单元上的路径也会被影响到。-rise_from rise_from_list与-from选项相同,除了通过路径上指定的对象时,必须是上升状态。如果一个时钟对 象被指定,这个选项选择由相同时钟驱动的起点,但仅在时钟源由时钟上升沿启动的路 径考虑沿时钟路径的任意逻辑反转。你仅能使用-from,-rise_from 和-fall_from 中的一个选项。-fall_from fa

37、ll_fromist与-from选项相同,除了通过路径上指定的对象时,必须是下降状态。如果一个时钟对象被指定,这个选项选择由相同时钟驱动的起点,但仅在时钟源由时钟下降沿启动的路径考虑沿时钟路径的任意逻辑反转。你仅能使用-from,-rise_from 和-fall_from 中的一个选项。-through through_list当前设计路径通过点(端口、接脚或子单元名称)的列表。禁止路径仅为通过路径的点 在throught_list列表中。如果不止一个对象,你必须使用引号或花括号。如果你多次使用-through选项,禁止路径设定应用给那些路径通过在每个给定的按顺序排列的 through_li

38、st列表中的一个成员。也就是说,路径必须首先通过第一个through_list中的一个成员,接着通过第二个列表的一个成员,像这样依次通过每个指定列表。如果 你使用了 -through 选项组合-from或-to选项,禁止路径仅当-from 或-to条件被满足, 并且-through条件也被满足时有效。-rise_through rise_through_list与-through选项相同,但,仅作用于上升转变发生在指定对象的路径。你可以在一条命令中多次使用-rise_through 选项,就你-through 选项一样。-fall_through fall_throughist与-throug

39、h选项相同,但,仅作用于下降转变发生在指定对象的路径。你可以在一条命令中多次使用-fall_through 选项,就你-through 选项一样。-to to_list指定禁止路径的结束点(时钟、端口、接脚或单元)。如果你没有指定一个列表,所有 起点设定在from_list 中的路径都被设定为禁止。to_list 可以包含时钟、接脚或端口 如果你设定一个时钟,所有与时钟相关的终点都会被考虑。如果你设定一个部接脚,接 脚必须是一个路径的终点(比如一个触发器的数据接脚)。如果你指定一个单元,终点 在单元上的路径会有影响。-rise_to rise_t oist与-to选项相同,但仅应用于终点为上升

40、状态的路径。如果指定的是一个时钟对象,该 选项选择由相同时钟驱动的终点,但只有被时钟源上升沿截取的路径,考虑沿时钟路径 的任意逻辑反转。你仅能使用-to、-rise_to 和-fall_to中的一个选项。-fall_to fall_to_list与-to选项相同,但仅应用于终点为下降状态的路径。如果指定的是一个时钟对象,该 选项选择由相同时钟驱动的终点,但只有被时钟源下降沿截取的路径,考虑沿时钟路径 的任意逻辑反转。你仅能使用-to、-rise_to 和-fall_to中的一个选项。-reset_path删除已存在的点到点,除了指定路径上的信息。仅相同上升/下降或建立/保持的信息被复位。这与在

41、 set false path岀现之前,使用reset path命令带类似参数的效果一样。描述:set_false_path 可以禁止最大延迟(建如你所知,删除特定路径的时序约束不影响电路控制 立)检查和最小延迟(保持)检查。set_false_path命令禁止从路径起点、途径点到终点的时序。路径起点是输入端口或寄存器时钟接脚。路径途径点可以是单元、接脚或端口。路径终点是寄存器的数据接脚或输出端口。要禁止当前设计中一个特定单元的时序,使用set_disable_timi ng。这会从单元时序图上删除特定的时序弧。如此,路径上经过这些弧的路径就无法通过了。set_false_path命令仍然允许

42、通过这些路径,只不过它们的时序约束被删除了。set_false_path是一个点到点的时序排除命令。这就意味着对于一个或更多时序路径,它帮助重写了默认单周期时序关系。其他点到点时序排除命令包括set_max_delay、set_min_delay 和set_multicycle_path 。如果一个路径满足多时序排除,以下规则协助决定哪个排除产生作用。与-from相关的规则与-rise_from 和-fall_from 有相同的应用,与 -through 和-to上升和下降选项类似。1. 两个group_path命令可能彼此冲突。但一个group_path自身排除不会与另一个类型的 排除相冲突

43、。所剩下的规则应用到两个group_path排除或两个非 group_path排除。如果两个排除都是set_false_path。它们没有冲突。如果一个排除是set_max_delay,另一个是 set_min_delay ,它们没有冲突。女口果一个排除是set_multicycle_path - hold,另一个是 set_multicycle_path -setup,它们没有冲突。如果一个排除是如果一个排除是如果一个排除是如果一个排除有如果一个排除有如果一个排除有如果一个排除有如果一个排除有2.3.4.5.6.7.8.9.10.11.12.13.set_false_pathset_max_

44、delayset_min_delay,其他的不是,那么,,其他的不是,那么,其他的不是,那么,set_false_path set_max_delay set_min_delay优先。优先。优先。排除附加限制性约束则优先。对于-from pin 或-from cell,其他的不是,那么,前者优先。-to pin 或-to cell,其他的不是,那么,前者优先。-through poi nts,其他的不是,那么,前者优先。-from clock,其他的不是,那么,前者优先。-to clock,其他的不是,那么,前者优先。set_max_delay 和口 set_multicycle_pathse

45、tup ,有更低值的约束。对于set_min_delay 和set_multicycle_path - load有更高值的约束。取消 set_false_path 的影响,使用 reset_path 或 reset_design 使用report_timing_requirements列岀设计中点到时点排除路径。多条件多模式支持:该命令仅使用当前方案的信息例:删除从ff12到ff34的时序约束set_false_path - from ff12- to ff34删除通过u14/z到ff29/Reset ,并且在终点为上升状态路径的时序约束set_false_path - rise -throu

46、gh u14 /Z- to ff29/Reset取消终点由时钟 PHI1驱动的保持检查(最小延迟时序)。触发器和锁存器由时钟PHI1驱动的都要考虑建立时间冲突,但不考虑保持时间冲突。set_false_path - hold - to get_clocks PHI1删除首次通过 u1 /Z或u2/Z,又通u5/Z或u6/Z所有路径的时序约束set_false_path-through u1/Z u2/Z- through u5/Z u6/Z取消通过u14/Z到达ff29/Reset 上升时序路径-to ff29/Resetset_false_path - rise_through u14/Z更

47、多:curre nt_desig n, reset_desig n, reset_path, set_disable_ti ming, set_max_delay.set_min_delay, set_multicycle_path set_case_a nalysis指定一个端口或接脚是在一个常数逻辑值1或0。或者被认为有上升或下降转变。语法:stri ng set_case_a nalysisvalueport_or_pi nist数据类型:port_or_pi nist列表参数:value指定常数逻辑值或转变,并赋值给接脚或端口。有效的常数值是0或1,zero或one有效的转变值是ris

48、ing 、falling 、rise和fall 。port_or_pi n_list案例分析的端口或接脚。命令执行非反向常数传播。描述:指定一个端口或接脚在常数逻辑值1或0.案例分析是一种方法,指定一个给定的模式,而无需改变网表结构。对于当前时序分析进程,你可以指定一些信号在常数值或仅某一种转变去做验证。但你指定案例分析为常数值时, 常数值通过网络进行传播,只要通过逻辑的控制值是常数值。比如,如果你指定一个 NAND】的一个输入为常数 0,它被传播到 NAND勺输岀,现在就被认为是 逻辑常数1。这个被传播的常数值,本身通过这个信号被传播到所有单元的驱动。转变的案例分析事件中,给定的接脚或端口仅

49、在时序分析时考虑指定的转变。其他转变为禁止。所有分析命令使用案例分析信号,包含排除路径侦测算法使用report_timing 命令带-true选项和-justify选项。你可使用案例分析(除模式命令外)完整地指定设计的模式。比如,你使用set_mode命令指定一个设计有TESTMOD的实例化模型,在时序分析时被禁止。另外,如果一个TESTMOD信号存在 在设计中,它可以被指定为常数逻辑值, 如此所有测试逻辑由 TESTMOD信号控制的都会被禁止。多条件多模式支持:该命令仅使用当前方案的信息例:指定名为IN1的端口为常数,逻辑值为0set_case_a nalysis 0 IN1指定如何关闭引用

50、单元的TESTM OD模式。并将TEST_PORT端口设为常数,逻辑值为0.remove_mode TESTMODE U1/U2set_case_a nalysis 0 TEST_PORT指定接脚U1/U2/A仅考虑上升转变。下降转变对于这些接脚无效set_case_a nalysisrising U1/U2/A更多:remove_case_a nalysis, report_a nalysis, set_modeset_operat ing_con diti ons定义当前设计的控制条件语法:Int set_operat ing_con diti ons-a nalysis_type bc_

51、wc | on_ chip_variatio n-min min_con diti on-max max_c on diti on-minibrary minib-max_library max_lib-min _phys min_proc-max_phys max_proc-library lib-object_list objectscon diti on数据类型:min_con diti on列表max_c on dit on歹列表objects列表con diti on歹歹表参数:-an alysis_typebc_wc | on _chip_variatio n设定分析的类型。两个选

52、项只能选择其中一个。使用bc_wc或on_chip_variation切换设计到min_max模式。bc_wc值设定最小(快)最大(慢)控制条件是两个极端的控制条 件。在bc_wc分析,用最大的控制条件分析SETUP用最小控制条件分析HOLD。on_chip_variation分析分别有最小和最大控制条件表示片上最大偏差的上下限。对所有 最大延迟的路径运用最大控制条件,对所有最小延迟的路径运用最小控制条件。-min min_con diti on指定用于最小延迟分析的控制条件。如果没有指定,工具默认使用最大控制条件。-min必须与-max同时使用。-max max_c on diti on指定

53、用于最大延迟分析的控制条件。-minibrary minib指定用于最短延迟分析,并包含有控制条件定义的库。可以是一个库的名称或集合。如 果是集合,工具将选择集合中首个满足条件的库。-max_library max_lib指定用于最大延迟分析,并包含控制条件定义的库。可以是一个库的名称或集合。如果 是集合,工具将选择集合中首个满足条件的库。-min _phys min_proc指定工艺资源名称搜索相匹配的电阻和电容值,用于最小延迟分析。该选项必须与 -max_phys 一起使用。-max_phys max_proc指定工艺资源名称搜索相匹配的电阻和电容值,用于最大延迟分析。该选项必须与 -mi

54、n_phys 一起使用。-library lib指定包含控制条件定义的库,用于最小和最大延迟分析。可以是一个库的名称或集合。 如果是集合,工具将选择集合中首个包含控制条件的库。-object_list objects指定要设置控制条件的单元或端口。如果没有指定,默认为整个设计。该选项支持子单 元或子模块。Con diti on指定有环境特征定义的条件,在最小最大延迟分析时使用。描述:该命令设定控制条件或环境特征,据此对当前设计进行时序或布局的优化。控制条件必须定义在.lib或link_library包含的任一库中。 当前设计的local_link_library 会被加到link_librar

55、y的开 头,查找时优先于link_library。库搜索顺序依次为:1. lib2. localin k_library3. lin k_library如果没有为设计设定控制条件,compile命令寻找库中首个库的控制条件作为初始值。如果库中没有控制条件定义,控制条件将不会被使用。使用-object_list选项将取代来自于设计或更高层次设计上的设定。使用report_design命令可以查看当前设计控制条件设定和库信息。使用report_lib命令可以查看指定库控制条件设定。多条件多模式支持:该命令仅使用当前方案的信息例:operating_conditions( “ BCCOM” ) pr

56、ocess : 0.6 ;temperature : 20 ;voltage : 5.25 ;tree_type :“ best_case_tree ”;控制条件的名称是BCCOM,参数定义为:process浮点数代表半导体工艺特征temperature浮点数代表环境设定的温度voltage浮点数定义环境设定中电压围的上限,下限为0.0tree_type环境互连模型。compile命令使用互连模式选择互连延迟的计算公式。三个有效模型:?best_case_tree,假设连线延迟为 0? worst_case_tree,使用集中(总) RC模型?balanced_tree,所有负载均匀分摊线电阻

57、当工艺因素,控制温度和控制电压与标称值有偏差,compile使用线性模型补偿偏差的带来的影响,模拟为单元延迟,输入负载,输出驱动等值。包含有控制条件定义的库中有标称值设计的定 义。以下例子设定控制条件为WCIND,如果link_library是my_lib.db,并且设计没有local_link_library设定。my_lib.db 的库为 my_lib_core。set_operat ing_con ditio ns WCIND控制条件 WCIND在库” my_lib_core ”中查找。使用other_lib_core.db库中BCIND值用于最小延迟分析,WCIND用于最大延迟分析。o

58、ther_lib_core.db 的库名称为 other_lib_coreset_operat ing_con diti ons min BCIND max WCIND library other_lib_core删除当前控制条件设定set_operat ing_con diti ons更多:compile, report_lib, reset_desig n, set_localin k_library, li nk_libraryset_wire_load_model为设计、端口、当前设计中层次化单元设定wire_load_attach_ name属性,选择一个连线模型用于连线电容的计算。

59、语法:status set_wire_load_model-n ame model_ name-library lib-mi n_maxobject_list数据类型:model_ name 字符object_list 集合参数:-n ame model_ name指定连线负载模型的名称。该模型必须是已定义的。这个选项必须使用。-library lib指定包含模型的库。可以是一个库的名称或集合。如果是集合,工具将选择集合中首个满足条件的库。-min指定仅用于最小延迟分析的模型。你不能用-min选项设定一个不同的模型或最小模块尺寸。因为对于这些参数,无论最大最小延迟分析都使用相同的值。-max指

60、定仅用于最大延迟分析的模型。任何用于最小延迟分析的模型集都没有影响。object_list指定将被设定连线负载模型的端口、设计或单元的列表。连线负载模型默认设定给当前 设计。描述:该命令设置 wire_load_attach_name属性给特定的端口,设计或对象列表中单元或当前设计,用 于连线电容的计算。如果没有任何选项,模型将作用于顶层设计。-name选项是必须的。如果指定的是一个设计,将作用于整个设计中的所有连线。如果指定的是一个单元,存在在当前设计中。设定给单元的连线模型会取代设计赋值给单元的连线模型。你可以使用该命令设定端口外部连线负载模型,并且不受设计连线模型的影响。如果没有为设计指定连线模型,首个满足条件的连线模型将默认设定给设计。当auto_wire_load_selection 属性被打开,如果库有wire_load_selection表,当前设计的单元部分将自动搜索与wire_load_selection表相匹配的

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。