FPGA4位全加器的设计

FPGA4位全加器的设计

《FPGA4位全加器的设计》由会员分享,可在线阅读,更多相关《FPGA4位全加器的设计(5页珍藏版)》请在装配图网上搜索。

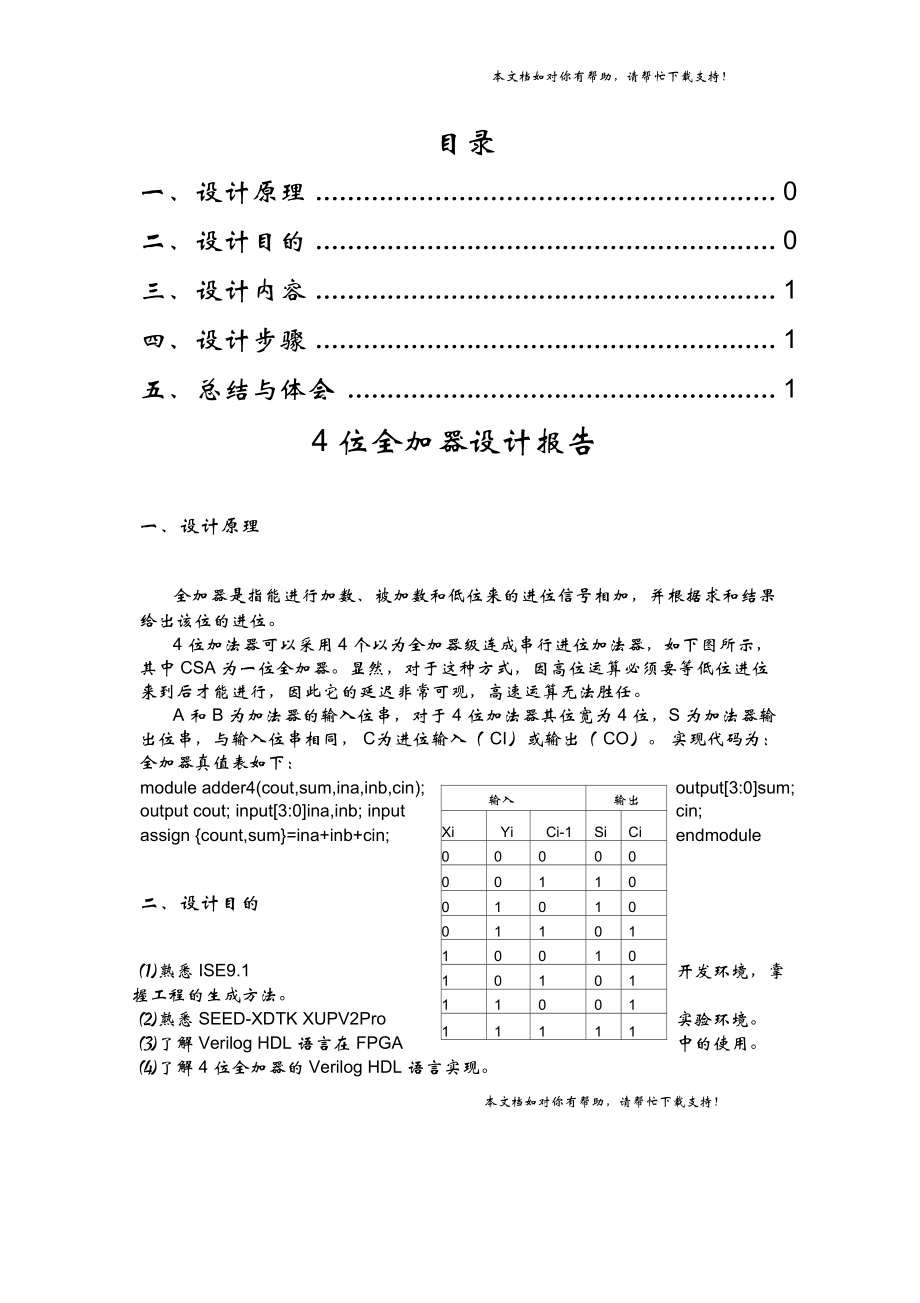

1、本文档如对你有帮助,请帮忙下载支持!目录一、设计原理 0二、设计目的 0三、设计内容 1四、设计步骤 1五、总结与体会 14 位全加器设计报告一、设计原理全加器是指能进行加数、被加数和低位来的进位信号相加,并根据求和结果 给出该位的进位。4 位加法器可以采用 4 个以为全加器级连成串行进位加法器,如下图所示, 其中 CSA 为一位全加器。显然,对于这种方式,因高位运算必须要等低位进位 来到后才能进行,因此它的延迟非常可观,高速运算无法胜任。A 和 B 为加法器的输入位串,对于 4 位加法器其位宽为 4 位,S 为加法器输 出位串,与输入位串相同, C为进位输入( CI)或输出( CO)。 实现

2、代码为: 全加器真值表如下:输入输出XiYiCi-1SiCi0000000110010100110110010101011100111111module adder4(cout,sum,ina,inb,cin); output3:0sum;output cout; input3:0ina,inb; input cin;assign count,sum=ina+inb+cin; endmodule二、设计目的熟悉 ISE9.1 开发环境,掌握工程的生成方法。熟悉 SEED-XDTK XUPV2Pro 实验环境。了解 Verilog HDL 语言在 FPGA 中的使用。了解 4 位全加器的 Ver

3、ilog HDL 语言实现。本文档如对你有帮助,请帮忙下载支持!三、设计内容用 Verilog HDL 语言设计 4 位全加器,进行功能仿真演示四、设计步骤1、创建工程及设计输入。在 E:目录下,新建名为 count8 的新工程。器件族类型( Device Family)选择“ Virtex2P” 器件型号( Device)选“ XC2VP30 ff896-7 ” 综合工具( Synthesis Tool)选“ XST(VHDL/Verilog) ” 仿真器( Simulator)选“ ISE Simulator” 下面一直 next 和确定。设计输入:在源代码窗口中单击右键,在弹出的菜单中选

4、择“ New Source”, 在弹出的对话框中选择“ Verilog Moudle”,在右端的“ File name”中输入源文件 名 adder4,下面各步单击“ Next ”按钮。在弹出的源代码编辑框内输入源代码并保存。2、功能仿真在 source窗口“ sources for”中选择“ Behavioral Simulation”。由“ Test Bench WaveForm”添加激励源。点击 Finish。出现波形激励编辑窗口。给 ina和inb 赋初始值。在 processes窗口中单击“ simulater behavioral model”即开始仿真,仿真结果 如下。从仿真的结

5、果可以看出, sum=ina+inb+cin。仿真结果正确。3、用 ChipScope 进行在线调试。生成 ChipScope 核。代码比较简单,这里只需要 ICON 和 VIO 两个核即可。 打开“ ChipScope pro core generato”r 首先是生成 ICON 核的过程。在 output netlist 位置指向 adder4 所在的路径,在 device family 里选 virtex2p 器件。由于只用了 VIO 核,所以 ICON 的控制端口数设置为 1。本文档如对你有帮助,请帮忙下载支持!之后就是就是一直确定就行, 直到出现生成新的核的界面。其次就是生成 VIO

6、 核的过程。 在输入输出端口设置过程中选定异步输入端口和异步输出端口。异步输入端口宽度根据 sum(4 位)、 cout(1 位)的总位数设定,异步输出端口根据 ina (4位)、inb(4 位)、cin(1位)的总位数设定。之后也是一直确定,这样 VIO 核也就生成了。添加 ICON 核与 VIO 核到工程。点击 “File Open”,在 adder4 所 在位 置 找到 icon_xst_example.v 和 vio_xst_example.v 文件并打开, 将 ICON 和 VIO 核的模块例化语句加到 adder4.v 相应的位置,并进行修改,最后得到的代码如下:module ad

7、der4(cout,sum);output3:0 sum;本文档如对你有帮助,请帮忙下载支持!output cout;wire 3:0 ina,inb;wire cin;wire 35:0 control0;wire 13:0 async_in;wire 8:0 async_out;icon i_icon( .control0(control0) );vio i_vio( .control(control0), .async_in(async_in), .async_out(async_out) );assign async_in3:0=ina3:0;assign async_in7:4=in

8、b3:0; assign async_in8=cin;assign async_in12:9=sum3:0;assign async_in13=cout;assign ina3:0=async_out3:0;assign inb3:0=async_out7:4;assign cin=async_out8;assign cout,sum=ina+inb+cin; endmodule module icon(control0);output 35:0 control0; endmodule module vio(control, async_in, async_out);input 35:0 co

9、ntrol;input 13:0 async_in;output 8:0 async_out; endmoduleadder4.v,”在进行保存,然后在 ISE 里进行综合,具体操作步骤:单击本文档如对你有帮助,请帮忙下载支持!processes窗口中双击 “Synthesize XS;T”如果综合没有出错,再实现,双击 “ Implement Design,最”后生成 bit 文件,双击 “ Generate Programming File。 ” 过程图为: 在 ChipScope 里观测调试单击“adder4.v在”,Processes窗 口中选择双 击“Analyze Design U

10、sing Chipscope 进”入 ChipScope Pro Analyzer窗口,点击 图标检查连接情况,然后 下载 bit 文件。由于我们没有板子只能做到这一步了。五、总结与体会通过这学期对 FPGA应用技术的学习, 我对 FPGA这项技术也有了一定的了 解。最后通过这个大作业也是我对整个的设计过程有了更进一步的认识。 我觉得 我在这次的课程设计大作业中我在以下几点收获很大。 加深了对全加器的认识; 了解了 4 位并行相加串行进位全加器的组成原理和组成框图; 掌握了工程的生成方法,以及如何创建 HDL 资源文件; 对 Verilog HDL 语言的用法有了一定的了解; 了解了如何进行功能仿真,如何添加激励源;

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。