CPU习题课练习

CPU习题课练习

《CPU习题课练习》由会员分享,可在线阅读,更多相关《CPU习题课练习(11页珍藏版)》请在装配图网上搜索。

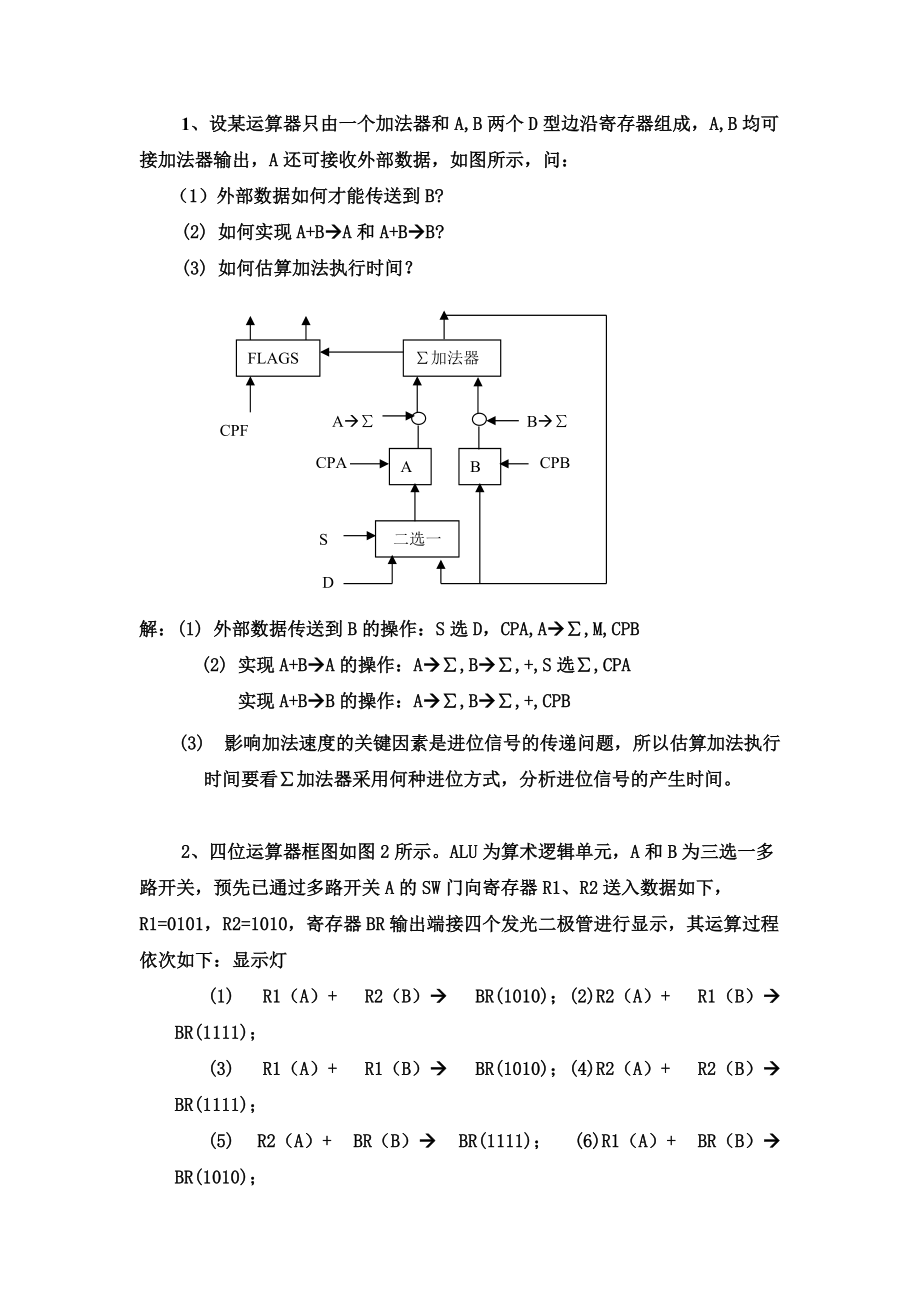

1、1、设某运算器只由一个加法器和A,B两个D型边沿寄存器组成,A,B均可接加法器输出,A还可接收外部数据,如图所示,问: (1)外部数据如何才能传送到B?(2) 如何实现A+BA和A+BB?(3) 如何估算加法执行时间?FLAGS加法器AB二选一CPFABSCPACPBD解:(1) 外部数据传送到B的操作:S选D,CPA,A,M,CPB(2) 实现A+BA的操作:A,B,+,S选,CPA 实现A+BB的操作:A,B,+,CPB(3) 影响加法速度的关键因素是进位信号的传递问题,所以估算加法执行时间要看加法器采用何种进位方式,分析进位信号的产生时间。2、四位运算器框图如图2所示。ALU为算术逻辑单

2、元,A和B为三选一多路开关,预先已通过多路开关A的SW门向寄存器R1、R2送入数据如下,R1=0101,R2=1010,寄存器BR输出端接四个发光二极管进行显示,其运算过程依次如下:显示灯(1) R1(A)+ R2(B) BR(1010);(2)R2(A)+ R1(B) BR(1111);(3) R1(A)+ R1(B) BR(1010);(4)R2(A)+ R2(B) BR(1111);(5) R2(A)+ BR(B) BR(1111); (6)R1(A)+ BR(B) BR(1010);试分析运算器的故障位置,说明理由。 显示灯 BR LDBR BUS ALU74181 S3 S2 M S

3、1 CS S0 BA 01 10 1101 10 11 AS0 ADC BDC BS0 AS1 BS1 R1 R2 BR R1 R2 BRR1 LDR1图2解:运算器的故障位置在多路开关B,其输出始终为R1的值。分析如下:(1) R1(A)+ R2(B)= 1010,输出结果错(2) R2(A)+ R1(B)= 1111,结果正确,说明R2(A),R1(B)无错(3) R1(A)+ R1(B)= 1010,结果正确,说明R1(A),R1(B)无错由此可断定ALU和BR无错 (4) R2(A) + R2(B) =1001,结果错,由于R2(A)正确且R2(A)=1010推知R2(B)=0101,

4、显然多路开关B有问题(5) R2(A) + BR(B) =1111,结果错,由于R2(A)=1010,BR(B)=1111,但现推知BR(B)=0101,证明开关B输出有错(6) R1(A)+BR(B) =1010,结果错,由于R1(A)=0101,本应BR(B)=1111,但现推知BR(B)=0101,证明开关B输出有错综上所述,多路开关B输出有错。故障性质:多路开关B输出始终为0101,这有两种可能:一是控制信号BS0,BS1始终为01,故始终选中寄存器R1;二是多路开关B电平输出始终嵌在0101上。3、某运算部件的基本结构如图3所示,假定此部件只有加(+)和减(-)两种基本操作,要求:(

5、1) 给出运算部件的所有微命令。(2) 指出哪些微命令是相容的,哪些是相斥的?(3)试用位数最少的操作控制字段来表示全部微命令。ALU+-XYR1R2ALUDBUS图3 解:(1)运算部件的微命令如下图所示。ALU+-XYR1R2ALUDBUSR2YR1YR1XDBUSR1DBUSR2(2)R2Y与R1Y是相斥的;+与-是相斥的;DBUSR1与DBUSR2是相容的;R1X与R2Y是相容的。(3) 微命令采用字段直接编码法。DBUSR1与DBUSR2在指令的执行过程中不会同时出现,可以将它们放在同一字段,用2位来控制。+与-也是相斥的,放在同一字段,用2位来控制,但由于能放在同一字段的微命令只有

6、2位,采用直接控制法也只需用2位,所以采用直接控制。根据以上分析,操作控制字段共有8个微命令,全部采用直接控制方式。4、图4所示为双总线结构机器的数据通路,IR为指令寄存器,PC为程序计数器(具有自增功能),M为主存(受R/W信号控制),AR为主存地址寄存器,DR为数据缓冲寄存器。ALU由加减控制信号决定完成何种操作。控制信号G控制的是一个门电路。另外,线上标注有控制信号,例如Yi表示Y寄存器的输入控制信号,R1o表示寄存器R1的输出控制信号。未标注的线为直通线,不受控制。现有“ADD R2, R0”指令完成(R0) + (R2) R0的功能操作。请画出该指令的指令周期流程图,并列出相应的微命

7、令控制信号序列。假设该指令的地址已放入PC中。图4解:ADD指令是加法指令,参与运算的二数放在R0和R2中,相加结果放在R0中。指令周期流程图如下图所示,包括取指令阶段和执行指令阶段两部分。每一方框表示一个CPU周期。其中框内表示数据传送路径,框外列出微操作控制信号。PCAR DRIR PCo,G ARiMDR 取 指 R/W=1 DRo,G,IRiR2 Y R2o,G R0 X 执 R0o,GR0+ R2R0 行 +,G,R0i 5、一台处理机具有如下指令格式 位 位 位位 X OP源寄存器目标寄存器地址格式表明有个通用寄存器(长度16位),X指定寻址模式,主存实际容量为256k字。假设不用

8、通用寄存器也能直接访问主存中的每一个单元,并假设操作码域OP=6位,请问地址码域应分配多少位?指令字长度应有多少位?假设X=11时,指定的那个通用寄存器用做基值寄存器,请提出一个硬件设计规划,使得被指定的通用寄存器能访问1M主存空间中的每一个单元。解:()因为218=256K,所以地址码域18位, 操作码域6位指令长度18 + 3 + 3 + 6 + 2 = 32位 ()此时指定的通用寄存器用作基值寄存器(16位),但16位长度不足以覆盖1M字地址空间,为此将通用寄存器左移,位低位补0形成20位基地址。然后与指令字形式地址相加得有效地址,可访问主存1M地址空间中任何单元。6、某计算机有8条微指

9、令I1I8,每条微指令所包含的微命令控制信号见下表所示,aj 分别对应10种不同性质的微命令信号。假设微指令的控制字段仅限8位,请安排微指令的控制字段格式。 解:微指令的控制字段为 8 位。根据 10 个微命令的兼容性和互斥性,分成 3 组。分别为 2 位、2 位和 4 位的小字段。每个2 位的组是3 个微命令的编码,需译码。4 位的组每位是 1 个微命令,不需译码。 本题可以有以下4种不同的解答。互斥的 d,h,i 为一组。互斥的 e,f,j 为 一组。其余的 a,b,c,g 为一组。互斥的 b,i,j 为一组。互斥的 e,f,h 为 一组。其余的 a,c,d,g 为一组。互斥的 b,g,j

10、 为一组。互斥的 f,h,i 为一组。其余的 a,c,d,e 为一组。互斥的 b,g,j 为一组。互斥的 e,f,h 为一组。其余的 a,c,d,i 为一组。7、设某一微操作控制信号C1既发生在指令1(设操作码 OP为I1I2 = 11)的节拍电位M3、节拍脉冲T1时间,也发生在指令2(设 OP为I1I2 = 01)的节拍电位M2节拍脉冲 T2时间,写出Ci的逻辑表达式,并表示在如图所示的GAL器件中。解:(1) C1= I1 I2 M3 T1+ I1 I2 M2 T2 (2)画图8、CPU数据通路为双总线结构,如图所示。图中:ALU:运算器IR:指令寄存器RA:ALU的输入寄存器 PC:程序

11、计数器 R1R4:程序员可用通用寄存器 MAR:存储器地址寄存器 MDR: 存储器数据寄存器(1) 画出修正错误后的连线图。(2) 描述指令ADD addr,R1(功能是R1+(addr)addr)的执行过程。R1PCIRMDRMMARRAR2R3R4ALU3232解:(1)画图R1PCIRMARMMDRRAR2R3R4ALU3232(2)指令ADD addr,R1的执行过程PCMAR; MMDR; MDRIR; IR(addr)MAR; MMDR; MDRRAR1MDR; +; ADDMDR; addrMAR; MDRM其中前3条微指令用来取指令;第4、5、6条微指令用来将IR地址部分给出的

12、直接地址addr的内容送入RA;第9条微指令实现加法并将结果送入MDR;第11条微指令将加法结果送回addr的存储器。9、某计算机的数据通路如下图所示,其中M主存, MBR主存数据寄存器, MAR主存地址寄存器, R0-R3通用寄存器, IR指令寄存器, PC程序计数器(具有自增能力), C、D-暂存器, ALU算术逻辑单元(此处做加法器看待), 移位器左移、右移、直通传送。所有双向箭头表示信息可以双向传送。请按数据通路图画出“ADD(R1),(R2)”指令的指令周期流程图。该指令的含义是两个数进行求和操作。其中源操作地址在寄存器R1中,目的操作数寻址方式为自增型寄存器间接寻址(先取地址后加1

13、)。解:解:“ADD (R1),(R2)+”指令是SS型指令,两个操作数均在主存中。其中源操作数地址在R1中,所以是R1间接寻址。目的操作数地址在R2中,由R2间接寻址,但R2的内容在取出操作数以后要加1进行修改。指令周期流程图如下:(每个步骤1分)10、某指令系统指令字长为20位,具有双操作数、单操作数和无操作数3种指令格式,每个操作数地址规定用6位二进制表示,当双操作数指令和单操作数指令条数均取最大值时,这3种指令最多可能拥有的指令数各是多少?解:解:按控制操作码的思想来设计,双操作数指令条数最大为28-1255条,单操作数指令条数最大为63条,无操作数指令条数最大为64条。0000000

14、0 255条二地址指令11111110 11111111 0 0 0 0 0 0 63条一地址指令 11111111 1 1 1 1 1 0 11111111 1 1 1 1 1 1 0 0 0 0 0 0 64条零地址指令 11111111 1 1 1 1 1 1 1 1 1 1 1 1 11、单总线CPU结构如图所示,其中有运算部件ALU、寄存器Y和Z,通用寄存器R0R3、指令寄存器IR、程序计数器PC、主存地址寄存器MAR和主存数据寄存器MDR等部件。试拟出转移指令 JMP #A的读取和执行流程。解:(1)PCMARPC+1PC(2)DBUSMDR,MDRIR(3)PCY IR(地址段)+YZ ZPC12、假设某机器有86条指令,平均每条指令由12条微指令组成,其中一条是取指微指令,是公用的,已知微指令字长48位,请问控制存储器的容量需多大?解:共有微指令(12-1)861947条,控存的容量为94748bit。

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。