八位加法器设计实验报告

八位加法器设计实验报告

《八位加法器设计实验报告》由会员分享,可在线阅读,更多相关《八位加法器设计实验报告(5页珍藏版)》请在装配图网上搜索。

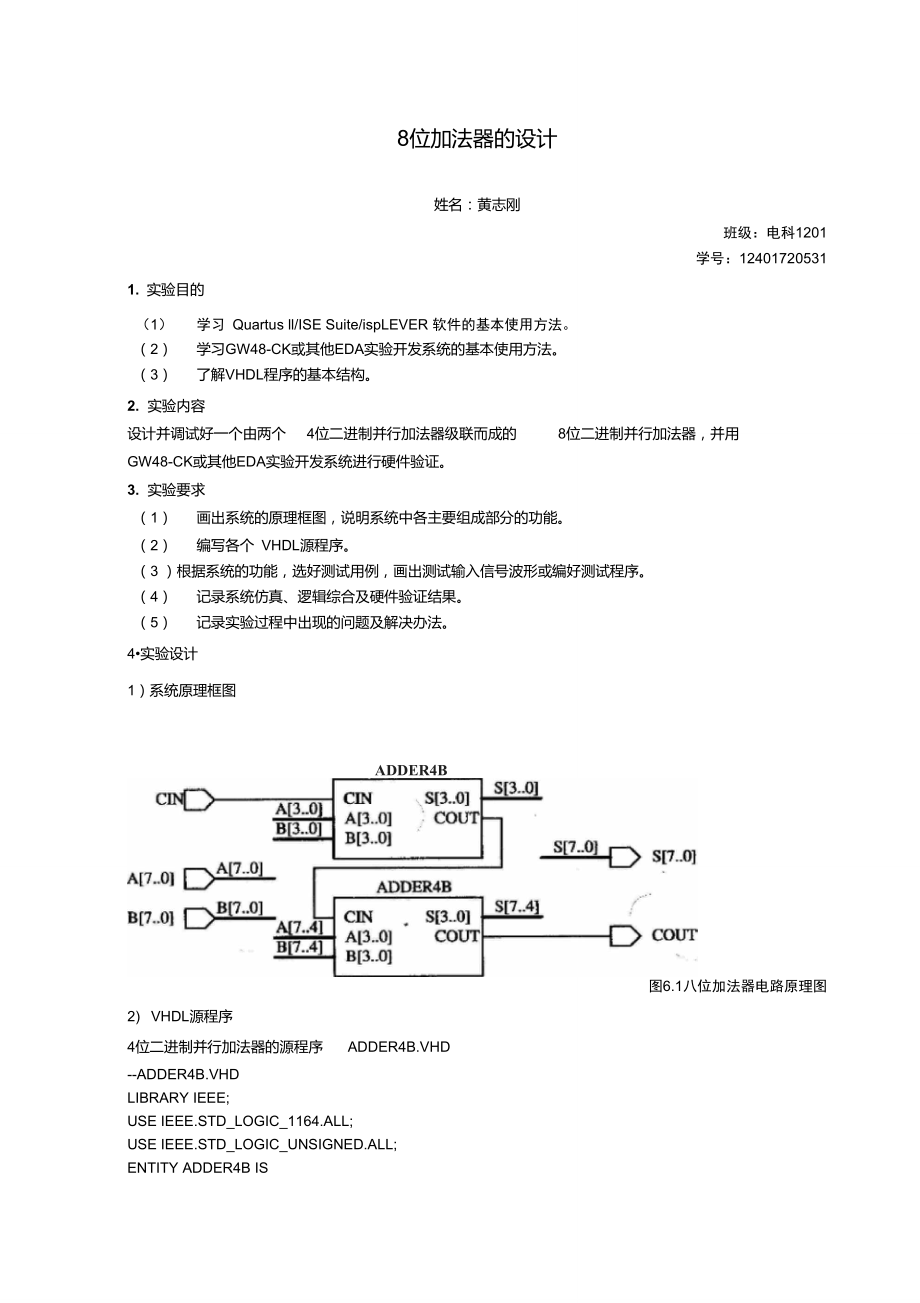

1、8位加法器的设计姓名:黄志刚班级:电科1201 学号:124017205311. 实验目的(1)学习 Quartus ll/ISE Suite/ispLEVER 软件的基本使用方法。(2)学习GW48-CK或其他EDA实验开发系统的基本使用方法。(3)了解VHDL程序的基本结构。2. 实验内容设计并调试好一个由两个4位二进制并行加法器级联而成的8位二进制并行加法器,并用GW48-CK或其他EDA实验开发系统进行硬件验证。3. 实验要求(1)画出系统的原理框图,说明系统中各主要组成部分的功能。(2)编写各个 VHDL源程序。(3 )根据系统的功能,选好测试用例,画出测试输入信号波形或编好测试程序

2、。(4)记录系统仿真、逻辑综合及硬件验证结果。(5)记录实验过程中出现的问题及解决办法。4实验设计1)系统原理框图ADDER4B图6.1八位加法器电路原理图2) VHDL源程序4位二进制并行加法器的源程序ADDER4B.VHD-ADDER4B.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ADDER4B ISPORT(C4: IN STD_LOGIC;A4: IN STD_LOGIC_VECTOR(3 DOWNTO 0);B4: IN STD_LOGIC_VECTOR(3 D

3、OWNTO 0);S4: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CO4: OUT STD_LOGIC);END ENTITY ADDER4B;ARCHITECTURE ART OF ADDER4B ISSIGNAL S5: STD_LOGIC_VECTOR(4 DOWNTO 0);SIGNAL A5, B5: STD_LOGIC_VECTOR(4 DOWNTO 0);BEGINA5= 0 & A4;B5= 0 & B4;S5=A5+B5+C4;S4=S5(3 DOWNTO 0);CO4C8,A4=A8(3 DOWNTO 0),B4=B8(3 DOWNTO 0),S4

4、=S8(3 DOWNTO 0),CO4=SC);U2:ADDER4BPORT MAP(C4=SC,A4=A8(7 DOWNTO 4),B4=B8(7 DOWNTO 4), S4=S8(7 DOWNTO 4),CO4=CO8);END ARCHITECTURE ART;5实验结果及总结1)系统仿真结果验证在程序调试和仿真时,我们要使用自底向上的方法进行,也就是对于含有多个模块的设计,我们要先从底层模块进行调试和仿真, 再进行更高层次模块的调试和仿真, 最后进行顶层模 块的调试与仿真。下图分别使用 Quartus II 8.0对ADDER4B和ADDER8B进行时序仿真的 结果。匕 Sinniil

5、atjon Wavefornn Editor - G:/eda/ADDER8B/ADDR4B - ADDER斗B - simulatiorVqsim/AD.View琦鱼|鑫R A三建耀黔足腹泄理心Master Time Bar: 0 psPointer: 150,52 nsInterval;Start:End:i录P MU3学阴 11C4 0D S4UX。斗UXVslije atr3) ASU3U 66CSU0CO9OX曲S&UXName【、殆X诟厂邮x 一叫 i GX 1 mX.迂 j !i i |j.(耳廉 钳鼎皿 % 乜 耳五燉222痢厂石厂:ISimulation Waveform E

6、ditor - Gyeda/ADDERBB/ADDERBB - ADDER8B - simulation/qsim/AD.-File Edit View SiHiiatioriHdp Search!冷1珂履& j蛊=解:Master Time Bar: 0 pS4 卜 Pointjer: 51.04 ftSInterval:Start:End:0% 00:00;00图6.3ADDER8B的时序仿真结果2)逻辑综合分析下面是使用 Quartus II 8.0进行逻辑综合 ADDER8B的RTL视图;对ADDER8B 的RTL视图 中ADDER4B进行展开的视图;使用 Quartus II 8.0对ADDER8B进行逻辑综合后的资源使 用情况。ADDER8B综合后的RTL视图Technology Map Viewer - Po吐-Filling - G7eda/ADDER3B/ADDER4E - ADDER4BSearch albtra.tDrflPage; lof 1+“戰 ADO&l 姬:】IDO% 00 巾 D:盟ADDER8B综合后的RTL视图中将ADDER4B展开后的视图3)实验过程中出现的问题及解决方法问题:仿真结果与书本结果不一样答:设置的时间间隔过小,将其扩大便能得到正确结果。问题:无法完成编译答:通过对下面提示对文本进行修改最终完成了编译。

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。