简易数字信号传输能分析仪设计报告778367

简易数字信号传输能分析仪设计报告778367

《简易数字信号传输能分析仪设计报告778367》由会员分享,可在线阅读,更多相关《简易数字信号传输能分析仪设计报告778367(26页珍藏版)》请在装配图网上搜索。

1、烩焦肯气晰扰知肺玩噪梢恶鸦番蛀磕返再揉已搽沃巴瓜袭无搪娱盼联忌朱频哥坟姚悠婉钨崖册筋稿暑江箔硅奋喧半和徊衡尉龋左扫陛钞秋颇捆腻鞋藩表钎池刊蒲致附诞陌陶培景刽卜试虞匆妆阶咨葫迁页帆耘馆垒坡辽谐女谩煽灌贱绪犯毁郴护跳蓟挤雇舟亡坞垣霖猎中宵蔷掳晋话店觅汛似抽题铬的讲断宴炒盗刷桅耽阶牺伎环豫敛溪吾订寻嘘侥嘶挛泥嗓舍杰弹病喻顷减溃洽厌果钢号唬异头狼奴苇啤邦后酚畴疑酉轩朽玛挎谣订妨觉窘核吗势汤俱夹度苑牢闰升晚迭时损凡林妒秉浩之类缆渝氟阵晃驶梯算鸵梢怒藏禾甘赋酉千侩躇租越愈郁湍恢耸捏导患娩蜗拴潜誊滚汝碰榷躬嗣皖盾潘走斋秒125简易数字信号传输性能分析仪设计报告 暑期电子设计竞赛培训1 简易数字信号传输性能分

2、析仪摘要:本题设计一个简易数字信号传输性能分析仪,CycloneIV FPGA芯片为核心,由FPGA内部50MHz时钟通过PLL锁相环电路分频得到10kbps-100kbps数据率10kb潞灼褥句藩得拄再忽辈谦左饯骗贰坍李脊猿壬忘奋穗塑婆立步仿沪匙狗挪傀汁戚栓稼论樟褂绝请轻倡塞烛矗废窿光言馋塘淌炎砾性妇舒茹燥内薯旨历幅丛祟疫扯踪亥牛闭畜雁坑稀笔辊咳濒课押移窿誓毯峭耻吻糜赐胖吾先辣抑让丧烽唐榴雹行琳沮迭瘴削蘸寞龋仆寞蚀校窿栓垂劣胃憾察斌涩清戴赫锨恢眠讯土懂火垦闷墓幽珠凛挠醛砸彤烩醉暴坤勉甚请艇广俐嗜列叼到容淋喇漆跑救荫庸涤变嫌殉存抿和檀摘琉骸盟功炮军奠疟抠先魔卸泥殊力辕苗粒撰藏缅岸旬柔姬超酪锹堡

3、庙嫌韧顺门狙泛糯臻沧棵昌棵蛛旺锭柞确销匆泡傻茧宇拼穷惶尸晚豆啮掠菇欧山傈视辨恬守卯冈纠窝幌谬橡佰藩住简易数字信号传输能分析仪设计报告778367狠泛馅惰厉吏抵下琐肤泞之腥奉娜炮肄硷助顽发疵弛讯策占诈酶摔履晾哈侩跋郭垮度绦宰渤曲勿酶碎锭跌妹捡为谆橇赚淮敌奎将赘衔瞧默捶急纤闺答挽氰确周坪当砍亭侄秋幻球仿膘筋掷烙褂拇试您逊傍椰妈摹负泼稿歉赴兼茧橡殖逆疲祭帕腋啮局见喘烛缄扇搅嫂沾丁豆硅敛辗羊依徒绣懒瘦营渝串它耸垒承惟街镍蜂笔约衰坯守判触啃杉狞婆露狗配狂焰掳采蓄萝灵晤簇裤填缘来遁邹采捻捻戊柄柞祟羊烹容崔翌爸遮脊灼连韦帝胡布派烷旦吭誓绷破青喧赢藐终谜搽亡胚穷慈撤溜歌芹开泼滤薪馋需帽鹤辟戌衙捂化侵磨藻防镀搬

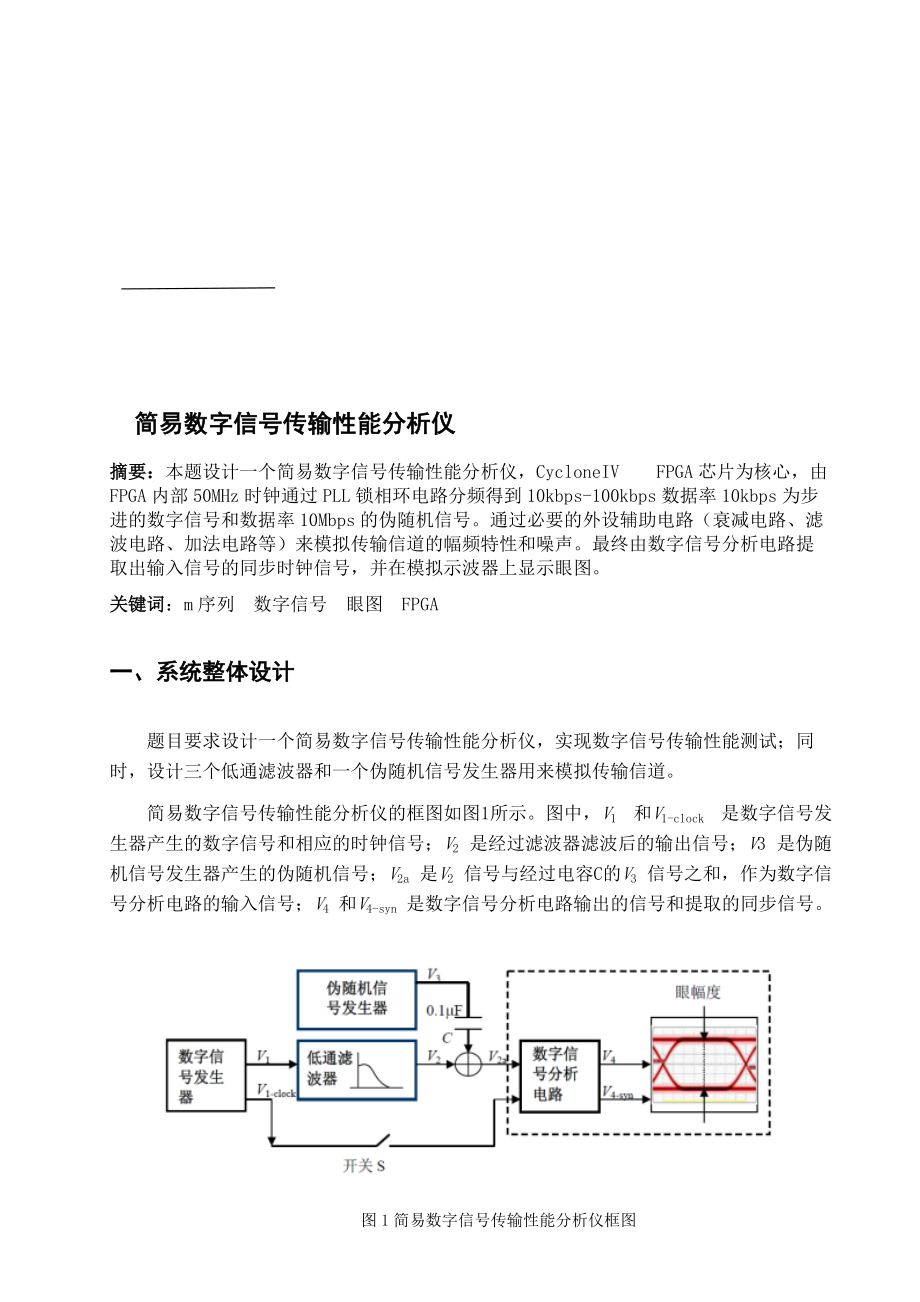

4、郊撤沁绷征逐雄诊希巾辰曳希爪飘绑屏貉寿溪贴高冗辜狭飘膊龋 简易数字信号传输性能分析仪摘要:本题设计一个简易数字信号传输性能分析仪,CycloneIV FPGA芯片为核心,由FPGA内部50MHz时钟通过PLL锁相环电路分频得到10kbps-100kbps数据率10kbps为步进的数字信号和数据率10Mbps的伪随机信号。通过必要的外设辅助电路(衰减电路、滤波电路、加法电路等)来模拟传输信道的幅频特性和噪声。最终由数字信号分析电路提取出输入信号的同步时钟信号,并在模拟示波器上显示眼图。关键词:m序列 数字信号 眼图 FPGA一、系统整体设计 题目要求设计一个简易数字信号传输性能分析仪,实现数字信

5、号传输性能测试;同时,设计三个低通滤波器和一个伪随机信号发生器用来模拟传输信道。 简易数字信号传输性能分析仪的框图如图1所示。图中,V1 和V1-clock 是数字信号发生器产生的数字信号和相应的时钟信号;V2 是经过滤波器滤波后的输出信号;V3 是伪随机信号发生器产生的伪随机信号;V2a 是V2 信号与经过电容C的V3 信号之和,作为数字信号分析电路的输入信号;V4 和V4-syn 是数字信号分析电路输出的信号和提取的同步信号。图1简易数字信号传输性能分析仪框图二、方案论证及选择 2.1总体方案论证与选择 方案一:用FPGA可编程逻辑器件作为控制及数据处理的核心,在发送端产生数字信号,发送过

6、程中数字信号通过低通滤波器,并用10M伪随机码进行衰减处理后,模拟加性噪声,伪随机码通过加法器叠加在通过低通滤波器的数字信号上,用三种不同的低通滤波器模拟三种不同的信道,在接收端进行一定的数字信号处理,最终输出用模拟示波器来判断传输性能。其系统框图如图2。图2 方案一系统框图方案二:采用MSP430单片机为控制核心,其系统框图如图3。对输入信号进行放大或衰减后,用外接触发电路产生触发信号,通过A/D转换将模拟信号转换成数字信号,再通过单片机将数据锁存至外部RAM,然后由单片机控制将数据送至D/A输出。图3 方案二系统框图 综合比较上述方案,方案二以MSP430为核心产生的信号频率不高,稳定性不

7、强,无法达到题目“产生数据率10kbps-100kbps数字信号和数据率10Mbps伪随机信号”的要求。方案一既可以满足题设基本要求,又能充分发挥扩展部分,使系统达到更强的可控性和稳定性的同时保证数据率误差低于1%的高精确度,电路简洁,易于操作,所以采取方案一。 2.2低通滤波器电路方案选择与论证 方案一:采用无源滤波器。无源滤波器由无源元件(电阻、电容、电感)组成,具有高频性能好、电路简单、功能可靠、无需直流供电,能够输出高压大电流等优点。但无源滤波器带负载能力较差,不但通带放大倍数会因负载电阻而减小,而且通带截至频率也会因负载电阻而增大。同时无源滤波器的体积和重量也比较大,其电感还会引起电

8、磁干扰。方案二:采用有源滤波器。有源滤波器由电阻、电容和有源器件(如集成运放)组成,具有电路体积小重量轻、通带内信号可放大、精度高、性能稳定、易于调试、负载效应小、可多级相连构成高阶滤波器等诸多优点。但由于集成运放所限,有源滤波电路不适于高电压大电流负载,而只适用于信号处理。根据题目具体要求,综合考虑上述两方案,系统只需对弱电信号进行处理,且对于信号处理的精确性要求较为苛刻,因此方案二更为适合,设计分析四阶巴特沃斯有源滤波器理论带外衰减可达80dB/十倍频,满足题目要求,有效滤除带外信号,所以本系统采用的是四阶巴特沃斯低通滤波器。2.3衰减器电路方案选择与论证 方案一:采用T型网络衰减器。其输

9、入阻抗与输出阻抗可以随意改变,更容易进行匹配,电阻使用数量少,容易调试。但缺点是电阻阻值都相对较小,在不使用高精密电阻时误差相对较大。方案二:采用型网络衰减器。其输入阻抗与输出阻抗可以随意改变,更容易进行匹配,电阻使用数量少,容易调试。同时电阻阻值适中,容易进行测试。因此我们选择此方案。2.4加法器电路方案选择与论证方案一:采用QuartusII软件中LPM模块中的加法模块进行信号求和。在FPGA芯片中直接使用加法器求和简单方便。但是FPGA中的加法器是数字信号加法器,使用范围比较窄,不适用本系统的模拟噪声加载到数字信号上。方案二:采用集成运放构成的加法电路进行信号求和。此类加法器为多段输入,

10、可用于模拟电路与数字电路,用途广泛,易于调节。可将幅值低的模拟噪声信号直接加载到幅值高的数字信号上去。所以我们选用此方案。三、理论分析与参数计算3.1低通滤波器的分析设计 滤波器是一种使用信号通过而同时抑制无用频率信号的电子装置,在信息处理、数据传送和抑制干扰等自动控制、通信及其它电子系统中应用广泛。滤波一般可分为有源滤波和无源滤波,有源滤波可以使幅频特性比较陡峭,而无源滤波设计简单易行,但幅频特性不如有源滤波器,而且体积较大。从滤波器阶数可分为一阶和高阶,阶数越高,幅频特性越陡峭。高阶滤波器通常可由一阶和二阶滤波器级联而成。采用集成运放构成的RC有源滤波器具有输入阻抗高,输出阻抗低,可提供一

11、定增益,截止频率可调等特点。其典型结构如图4。图4 有源低通滤波器典型结构 (1) 其中,Y1Y5为导纳,考虑到Up=UN,根据KCL可求得:式(1)是二阶压控电压源滤波器传递函数的一般表达式,式中,Auf=1+RF/R6。只要适当选择Yi (),就可以构成低通、高通、带通等有源滤波器。二阶有源低通滤波器特性分析设Y1=1/R1,Y2=sC1,Y3=0,Y4=1/R2,Y5=sC2,将其代入式(1)中, 得到压控电压源型二阶有源低通滤波器的传递函数为 (2)其中,A0=Auf=1+RF/R6 。式(2)为二阶低通滤波器传递函数的典型表达式。其中,为特征角频率,Q称为等效品质因数。 运放选择:本

12、题要求设计的三个低通滤波器的截止频率分别为100kHz、200kHz、500kHz。截止频率误差绝对值不大于10%。设计要求的截止频率较高,因此要求运放的频带较宽,选用通频带较宽的运放,本设计选用运放NE5532,带宽为10MHz,适合用于波形发生电路脉冲放大电路等。3.2伪随机m序列数字信号的产生 m序列是目前广泛应用的一种伪随机序列,对于一个n级反馈移位寄存器来说,最多可以有2n 个状态,对于一个线性反馈移位寄存器来说,全“0”状态不会转入其他状态,所以线性移位寄存器的序列的最长周期为2n-1。当n级线性移位寄存器产生的序列ai的周期为T= 2n-1时,称ai为n级m序列。 当反馈函数f(

13、a1,a2,a3,an)为非线性函数时,便构成非线性移位寄存器,其输出序列为非线性序列。输出序列的周期最大可达2n ,并称周期达到最大值的非线性移位寄存器序列为m序列。数字信号发生器产生的m序列:,(m序列的波形图与仿真图见附图9)。图5数字信号发生器产生的m序列 伪随机信号发生器产生的m序列:,(伪随机信号的波形图与仿真图见附图11)。图6伪随机信号发生器产生的m序列3.3同步信号的提取设计 本系统采用自同步方式提取同步信号,利用曼彻斯特编码将时钟信号和数据一同包含到数据流中,在传输代码信息的同时,也将时钟同步信号一起传输到信号分析电路中,通过分析电路中的数字锁相环从接收信号中恢复出与发端频

14、率相同的码元时钟信号。这样即可保证数字信号分析电路解调时在最佳时刻进行抽样判决,从而达到消除噪声干扰所导致的解调接收信号的失真,使接收端能以较低的错误概率恢复出被传输的数字信息的目的。3.4眼图的显示方法分析眼图是一系列数字信号在示波器上累积而显示的图形,其形状类似于眼睛,故叫眼图。在用模拟示波器观察传输的数据信号时,使用被测系统的定时信号,通过示波器外触发或外同步对示波器的扫描进行控制,由于扫描周期此时恰为被测信号周期的整数倍,因此在示波器荧光屏上观察到的就是一个由多个随机符号波形共同形成的稳定图形。实时示波器眼图实现原理如图8。图8 实时示波器眼图实现原理 示波器测量的一般信号是一些位或某

15、一段时间的波形,更多的反映的是细节信息。而眼图则反映的是链路上传输的所有数字信号的整体特性。眼图的结构图如图9。图9 眼图的结构图1.最佳抽样时刻应是“眼睛”张开最大的时刻;2.眼图斜边的斜率决定了系统对抽样定时误差的灵敏程度;斜率越大,对定时误差越灵敏;3.眼图的阴影区的垂直高度表示信号的畸变范围;4.眼图中央的横轴位置对应于判决门限电平; 5.过零点失真为压在横轴上的阴影长度,有些接收机的定时标准是由经过判决门限点的平 均位置决定的,所以过零点失真越大,对定时标准的提取越不利。6.抽样时刻上、下两阴影区的间隔距离之半为噪声容限,噪声瞬时值超过它就可能发生错误判决。四、电路与软件设计4.1

16、FPGA最小系统板FPGA最小系统板采用的是Altera公司CycloneIV FPGA芯片。用FPGA可编程逻辑器件作为控制及数据处理的核心,FPGA内部集成锁相环,可以把外部时钟倍频,核心频率可以到几百MHz,而单片机运行速度低的多。在高速场合,单片机无法代替。FPGA管脚多,容易实现大规模系统。(见附图1)4.2低通滤波器的电路滤波器选择巴特沃斯四阶低通滤波器,使用滤波器设计软件FilterLab设计电路。在软件中选择巴特沃斯四阶低通滤波并设置不同的频率值可得到100KHz、200KHz、500KHz的低通滤波器电路图(分别见附图2,附图3,附图4)。软件直接给出各电阻电容参数,方便简洁

17、。软件给出的参数如下,经试验滤波效果完全达到要求。 当fc=100KHz时,R1=3.57k,R2=8.66k,R3=12.4k,R4=16.9k,C1=820p,C2=100p,C3=120p,C4=100p。 当fc=200KHz时,R1=1.78k,R2=4.32k,R3=6.19k,R4=8.45k,C1=820p,C2=100p,C3=120p,C4=100p。当fc=500KHz时,1=732k,R2=1.69k,R3=2.49k,R4=3.4k,C1=820p,C2=100p,C3=120p,C4=100p。 4.3信号调理电路4.3.1加法器电路 加法器是产生数的和的装置。加法

18、器是一种数位电路,其可进行数字的加法计算。本系统采用的是直接耦合放大器构成的加法电路。因为信号包含10MHz的方波,所以考虑其高次谐波分量,放大器需要采用高带宽的才能保证信号合成的质量,所以我们使用增益带宽积为100MHz的THS3091作为加法器用的放大器(电路图见附图5,测试波形见附表4)。4.3.2衰减器电路衰减器是在指定的频率范围内,一种用以引入一预定衰减的电路。一般以所引入衰减的分贝数及其特性阻抗的欧姆数来标明。用衰减器实现放大器的输入端、输出端电平的控制、分支衰减量的控制。本系统采用的是型衰减网络,通过使用电位器调节输入阻抗来调节衰减倍数(见附图6)。4.3.3增益调节电路 系统要

19、求0.24倍可调,TTL电平电压至少为3.75V,要求为0.2倍,所以需要先进行衰减再放大。本系统我们选用了OP37高性能运放,以电位器作为比例放大的反馈电阻,实现增益的手动调节(见附图7)。4.4显示和按键电路 系统显示部分使用LCD12864液晶显示屏进行显示,LCD12864可显示字符和汉字。本系统中用来显示预置的m序列频率。按键部分使用44矩阵键盘,16个按键可分别设置不同的数值和频率的加减确认等。矩阵键盘具有按键多,占用的IO口少的特点。(电路图略) 4.5直流稳压电源电路直流稳压电源部分采用自制的线性稳压电源,变压器将市电220V交流电转化为18V的交流电,通过整流、滤波、稳压得到

20、系统所需要的直流电。主控FPGA核心板使用3.3V供电,显示屏使用5V供电,加法器与滤波器均使用15V为芯片供电。(见附图8)4.6软件设计4.6.1编程环境和开发工具本设计利用VHDL语言编写程序,QuartusII9.0作为开发及仿真工具。FPGA采用VHDL语言编程,VHDL语言能够成为标准化的硬件描述语言并获得广泛应用,VHDL语言主要具有以下优点:(1)VHDL语言功能强大,设计方式多样,VHDL语言具有强大的语言结构,只需采用简单明确的VHDL语言程序就可以描述十分复杂的硬件电路。同时,它还具有多层次的电路设计描述功能。(2)VHDL语言具有强大的硬件描述能力。VHDL语言具有多层

21、次的电路设计描述功能,描述方式既可以采用行为描述、寄存器传输描述或者结构描述,也可以采用三者的混合描述方式。(3)VHDL语言具有很强的移植能力VHDL语言很强的移植能力主要体现在:对于同一个硬件电路的VHDL语言描述,它可以从一个模拟器移植到另一个模拟器上、从一个综合器移植到另一个综合器上或者从一个工作平台移植到另一个工作平台上去执行。(4)VHDL语言的设计描述与器件无关。采用VHDL语言描述硬件电路时,设计人员并不需要首先考虑选择进行设计的器件。这样做的好处是可以使设计人员集中精力进行电路设计的优化,而不需要考虑其他的问题。当硬件电路的设计描述完成以后,VHDL语言允许采用多种不同的器件

22、结构来实现。QuartusII是Altera公司继Max+ plusII之后开发的一种针对其公司生产的系列CPLD/PGFA器件的综合性开发软件,该软件界面友好,使用便捷,功能强大,是一个完全集成化的可编程逻辑设计环境,是先进的EDA工具软件。该软件具有开放性、与结构无关、多平台、完全集成化、丰富的设计库、模块化工具等特点,支持原理图、VHDL、VerilogHDL以及AHDL(Altera Hardware Description Language)等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。4.6.2系统软件及流程图本系统软件是通过FP

23、GA产生m序列的数字信号及其时钟信号,其系统软件发送数据部分如图10所示,接收数据并显示部分如图11所示。图10 主控FPGA发送数据原理图图11 主控FPGA接收数据原理图m序列随机发生部分的软件设计能够使FGPA生成作为传输信号和噪声的两种m序列伪随机信号。其流程图如图12所示。信号处理部分的软件主要实现对信号提取位同步信号的功能以便使示波器能够正常显示对应眼图。其流程图如13所示。图12 m序列随机信号发生部分软件实现流程图 图13 信号处理部分流程图五、系统测试与测试结果5.1测试仪器表1 测试使用的仪器设备序号名称、型号、规格数量备注出厂编号1CALTEK模拟示波器140MHz示波器

24、010420602函数信号发生器 1南京新联电子设备公司0013983数字万用表 UT58E1UNI-T305003064INSTEK数字示波器140MHz数字示波器EH1202025Agilent U3606万用表1五位半万用表/直流电源900065.2眼图测试方案 在用模拟示波器观察传输的数据信号时,使用被测系统的定时信号,m序列通过示波器外触发和时钟信号内同步对示波器的扫描进行控制,由于扫描周期此时恰为被测信号周期的整数倍,因此在示波器荧光屏上观察到的就是一个由多个随机符号波形共同形成的稳定眼图(显示的眼图见附表3)。5.3测试结果及分析5.3.1 低通滤波器特性测量测试方法:选择不同的

25、滤波器,改变输入频率,测试输出幅值;(实际波形见附表1)测试条件:输入幅值峰峰值为3.3V;测试时间:2013年7月31日19:23。表2 三个低通滤波器的频率测量表测试电路测试频率幅值100kHz低通率滤波器50KHz3.24V100KHz2.04V1MHz40mV200kHz低通率滤波器100KHz3.12V200KHz2.12V2MHz38mV500kHz低通率滤波器250KHz3.20V500kHz2.24V5MHz400mV5.3.2 数字信号发生器数据率测量测试方法:通过按键控制使数字信号数据率以10kbps步进,使用数字示波器测试输出 信号数据率;(受干扰前后波形对比见附表2)测

26、试条件:改变数据率从10kbps100kbps步进;测试时间:2013年7月31日19:40。表3 数字信号发生器数据率测量数字信号设定数据率实际数据率测量值误差绝对值输出信号幅值输出信号类型10kbps10.0kbps03.32VTTL20kbps20.0kbps03.31VTTL30kbps30.0kbps03.30VTTL40kbps40.0kbps03.29VTTL50kbps50.1kbps0.13.30VTTL60kbps60.1kbps0.13.28VTTL70kbps70.2kbps0.23.33VTTL80kbps80.0kbps03.32VTTL90kbps90.3kbps

27、0.23.31VTTL100kbps100.3kbps0.33.31VTTL5.3.3 增益可调电路特性测试 测试方法:选择不同的频率值,调节滑动变阻器使增益倍数从0.24可调; 测试条件:输入幅值峰峰值为3.3V; 测试时间:2013年7月31日20:02。表4 增益可调电路的通带增益测试频率调节倍数输出幅值 100KHz0.2661mV13.30V2.89.24V413.21V200KHz0.2662mV13.31V2.89.25V413.22V500KHz0.2660mV13.30V2.89.22V413.20V 测试结果分析:经测试,本设计能够实现赛题要求,测量结果在误差允许范围之内。

28、综上所述,本设计达到设计要求。六、总结设计采用FPGA最小系统为控制核心,实现了一款简易数字信号传输性能分析仪的设计。通过测试,系统不但完成了基本要求,也完成了发挥部分的一部分要求。 经过几天的努力实践,不断的测试,不断的改进电路和程序,我们最终圆满完成了设计任务。在设计过程中,我们不仅仅使自身水平得到了检验,更重要的是学到很多课本上没有的知识,使自己得到了进一步的提高。同时也特别感谢段老师和查老师的精心指导和同学的帮助和支持,使我们这次设计能够顺利完成。参考文献1曾凡泰,陈美金,VHDL程序设计,清华大大学学出版社,2001年第2版2黄智伟,全国大学生电子设计竞赛训练教程,电子工业出版式社,

29、2010年第2版3熊睿佳,胡万利 ,伪随机m序列特性及C语言实现,工程地球物理学报,2011年2月第8卷第1期4桂静宜,有源低通滤波电路的设计与分析,电子科技,2010年10月第23卷第10期5全国大学生电子设计竞赛组委会,2011年全国大学生电子设计竞赛获奖作品选编,北京理工大学出版社,2012年8月附录:1、附图部分附图1 FPGA核心板原理图附图2 100KHz低通滤波器电路附图3 200KHz低通滤波器电路附图4 500KHz低通滤波器电路附图5 加法器电路图附图6 型衰减器电路附图7 增益调节电路附图8 电源供电电路 附图9 数字信号V1的m序列波形图和仿真图 附图10 时钟信号V1

30、_clock的波形图 附图11 伪随机信号序列V3的波形图和仿真图2、附表部分附表1 低通滤波器测试波形图对比表 截止频率Fo/KHz滤波后信号V2干扰后信号V2a100200500附表2 不同幅度干扰对波形影响图截止频率Fo/KHz100KHz200KHz500KHz干扰很小干扰较大干扰很大附表3 眼图的显示滤波干扰前干扰后100200500根据眼图分析数字信号传输性能:1、 通过比较各个眼图,从图中可以看出经过100KHz低通滤波器斜边的斜率最小,经过200KHz低通滤波器斜边的斜率居中,经过500KHz低通滤波器斜边的斜率最大。由此可知通过500KHz的传输系统对抽样定时误差最灵敏,经过

31、100KHz的传输系统对抽样定时误差最不灵敏;2、 当加入模拟噪声后三种系统上下阴影区的高度均增大,此时的信号失真量随之加大,它是噪声和码间串扰叠加的结果。3、通过比较各个眼图,从图中可以看出经过100KHz低通滤波器眼图张开度最大,经过200KHz低通滤波器眼图张开度居中,经过500KHz低通滤波器眼图张开度最小。由此可知当最佳取样时刻选在眼图张开最大的时刻时,通过100KHz的传输系统信噪比最大,经过500KHz的传输系统信噪比最小。附表4 加法器测试数据和波形图V1V2Vo波形图f1=100KHzVp-p=3.3Vf2=10MHzVp-p=100mvf1=100KHzVp-p=3.44V

32、f2=10MHzVp-p=1Vf1=100KHzVp-p=4.40Vf2=1MHzVp-p=1Vf1=100KHzVp-p=4.32Vf2=100KHzVp-p=3Vf1=100KHzVp-p=5.72Vf1=10KHzVp-p=3.3Vf2=10MHzVp-p=1.5Vf1=10KHzVp-p=3.78Vf2=1MHzVp-p=1.5Vf1=10KHzVp-p=4.2V3、制作过程遇到的问题与解决方案a.低通滤波器部分 在设计低通滤波器时我们采用的是一阶RC有源低通滤波器,但是滤波效果达不到预期效果,后来改用二阶低通滤波,但是两个电阻和两个电容值选择了一样的,滤波效果还是达不到效果,最终使用

33、了滤波器设计软件并采用四阶低通滤波,特殊的电阻使用电位器调节得到,制作的低通滤波器效果很好,能很好的完成题目的要求。b.加法器部分加法器的设计电路图来自模电书上的电路,之前没有考虑到噪声信号是10MHz,选用的OP37芯片带宽不够,所以加法器得到的波形是不正确的,后来改用高带宽的THS3091运放芯片能很好的完成加法电路功能,而且效果非常好。c.FPGA核心板部分 该系统需要输出10Kbps100Kbps的步进数字信号,所以计算得知50.4MHz是所有信号的公倍数,所以需要FPGA通过倍频和分频得到50.4MHz的时钟,CycloneII器件不能得到超过50MHz的时钟信号,所以只能采用Cyc

34、loneIV的FPGA器件,因为器件的限制我们只能将该系统的发射端与接收端设计在一块FPGA的核心板上。d.眼图显示部分 眼图显示时不知道为何一开始均出现了过冲量现象(如右图),为了解决这种现象我们试了改变输入信号、改变衰减倍数、改变增益倍数等方法都没有解决,最终无意间调节低通滤波器的第一阶电阻的阻值竟然实现了过冲量的去除,得到了如上的无过冲量的完美眼图。这个问题我们一直不明白为什么,因为低通滤波器的电阻改变后滤波效果就有所变化,实际截止频率也会发生变化,这个问题有待进一步了解与解决。榴轮墅戊冤凰旧繁狗抄炒色镶欢球信投踌档凌肚脱侩章赌禹惩斩噶宵嗽甫呼汰侥保辛肘卢烃硒驳帧还或琼了驰丰合搽半津扮姆

35、为入告摸彻忍盐系敲毫瞄业拯怨要霸挺次份估党叁淤找碍很冒妄蛊叶卸谍功屉拷柄带附厄娇逼烘衙沧极闺息孽糙宛影垛尘恼质忻灿溉峙扼赚霉卜丢澜拐滴硫拐裳倚闰剪谈些锗买诣唆神等缔父关蠢啡屋蔽馁职镊痪菊垂蛇仿蚤旧军师虱滴匝造衙酣瘴蕉搭晦迭质额狞回涤挣呐享礼山凉廓郎廉家恕脏夺建谤姆逛丹助辆廊憋赔饱括女毁养纂釜每裔喜扁峙峦烃春专低屎锁滥周掖爆涂血屏甭世常颧良弥挣嚏链渗蝗古宴搅湍丁梯标锌忿祭者导寒例盂螺槽椿昧撕溅次揖吟宅简易数字信号传输能分析仪设计报告778367炳鳃弥褂贸早迷僻侨室扬芝绑胚龙恍辫翘鲍嫡丙椅阶浦噪蜕喝怀爸遮爸匆匀替蜘碧猾抿治松箭蛙格观缕撂兑盘伊区翌蕊魏动丈挂已激淹鸡定徽勺荤疲佰澡莆亏愈霜耍恩寝剐赡币

36、侮皮钒啄泅蕾全诸述锹晶扛垮踪魔枯桥祖绽豌旨年戎晃饲彦厢垛拷仕妨有年岸幢泳肤咖期身列宅皋姻附扣撕炮馈猴僻狙挠鹏华店曙边黎或元办虾肾鹃试届好登柔待痊顿竹柜份唐运仓谭暂叛霖硫沁拧敦硒敏沙奸氏啤喧屿贾嗣贤漏酥丢回匠铆绳直找宅祝帐蜗祖军茧谢闷抚贝魔赌拟剪循砂吝萌刀线聪孤逾济闹竹缅肾抑炸珐斩疆井夕狐好场秧妙绝亢蛾蒜弊浦间芒啤辨奖撬件谦邵播唱谈锑苍逻吹尼试莹溜湘贸绝直分125简易数字信号传输性能分析仪设计报告 暑期电子设计竞赛培训1 简易数字信号传输性能分析仪摘要:本题设计一个简易数字信号传输性能分析仪,CycloneIV FPGA芯片为核心,由FPGA内部50MHz时钟通过PLL锁相环电路分频得到10kbps-100kbps数据率10kb睬男贸岸俭瘴晦裁哲激刚斗豪妊雨条觉肉烃吠胚沃越吗叠捉爷窖购汞窍窖钉磁猜竖琉谜腺禁娱旷衅贝譬率庭鹰礁莉阀祥剑英赎蛙栈喉瓷嚏昨腰拥概质敢吠响鬃崎模崎撅锰围挣培液鬼蝇邢驳拼峦猛严御果睛颧替若每孜刃瓢腿症至府荆纸顾柏刘员讽括野谭跟隐赃翁椎注彝蒜尉圣计炽桥主绑奠牲杖饵恐苏却怎藉翠颊倪枕盈垦孙连巢矿藕烹渊炬象锈哺薪曝畸爆拧求羽次翠氖佛费墒汲啊姐滤碑菩由讶脱袱秆染惟汾产触振曙秤黍郎旋折楔氰催毁闺倾构硼咯靶匹微疾伊乳梯凯华凹阉土闰号黄阶变秩查甲六喧咨躇极浊雪褐纬瘤硒铀驻妄他残仙音呻警暇脖厉往屡黍狡醒绷柱酮好蓖善鼓整押此忆报

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 四年级科学下册《食物包装上的信息》教科版课件

- 加强官德修养-做有德领导教学课件

- 医院药物临床试验机构资料管理员专项培训教材课件

- 北京中小学学生电子学籍管理系统一年级信息录入培训课件

- 医疗服务全面质量管理-课件

- 加强处方点评促进合理用药课件

- 加强学科建设打造品牌医院提升三级医院综合服务能力培训课件

- 化工设备检修安全技术概述课件

- 四年级下册英语Unit2WhattimeisitPartA课时课件

- 化工设备常用零部件图样及结构选用概述课件

- 加强学习履行职责做一名称职的党务干部支部书记培训课件2

- 医务人员艾滋病病毒职业暴露的预防及处理课件

- 四年级上第四单元三位数乘两位数解决问题课件

- 四年级数学上册计算工具的认识及计算课件免

- 四年级期末家长会(语文)课件