基于FPGA的多功能波形发生器的设计与实现

基于FPGA的多功能波形发生器的设计与实现

《基于FPGA的多功能波形发生器的设计与实现》由会员分享,可在线阅读,更多相关《基于FPGA的多功能波形发生器的设计与实现(21页珍藏版)》请在装配图网上搜索。

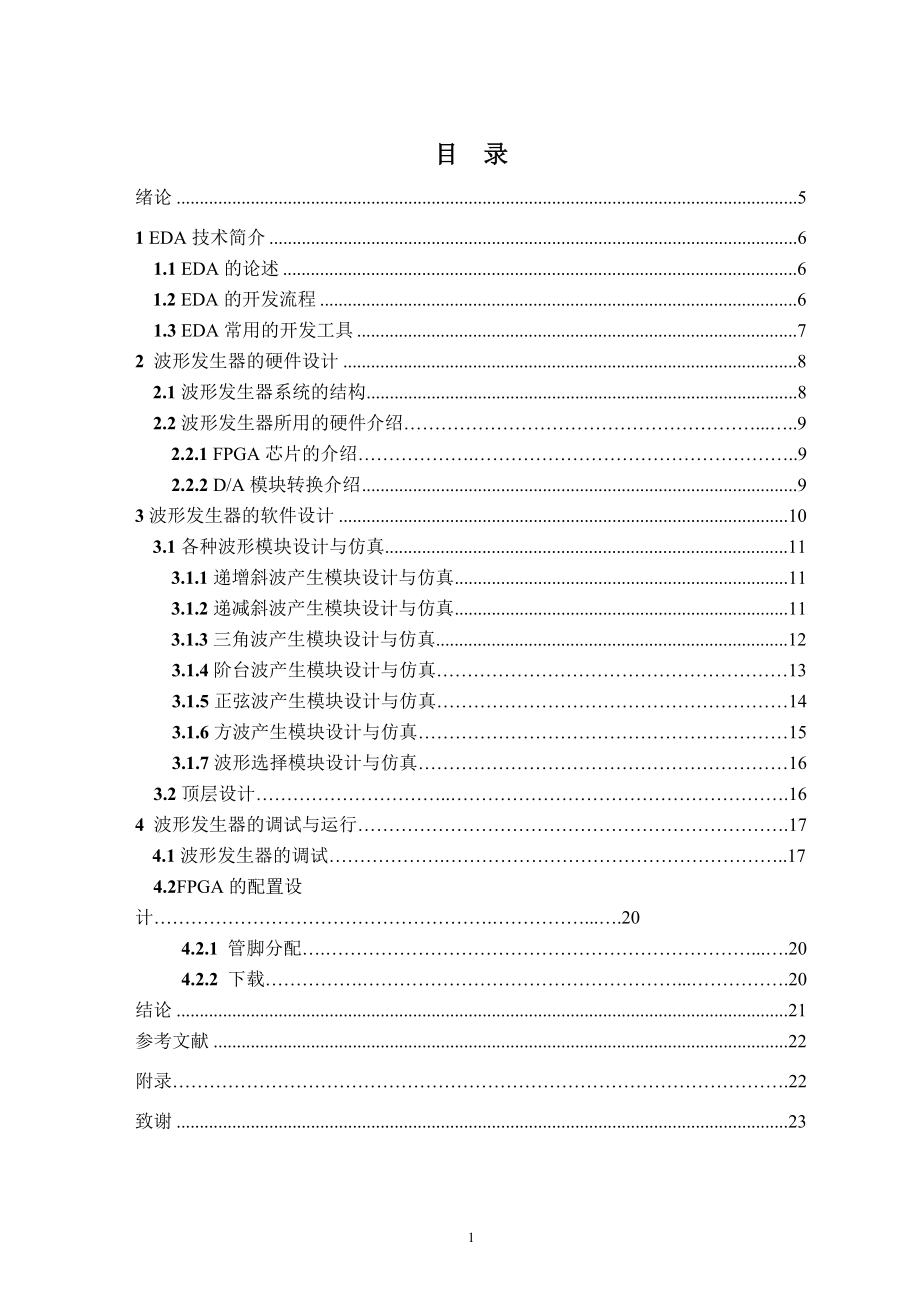

1、目 录绪论51 EDA技术简介61.1 EDA的论述61.2 EDA的开发流程61.3 EDA常用的开发工具72 波形发生器的硬件设计82.1波形发生器系统的结构82.2波形发生器所用的硬件介绍.9 2.2.1 FPGA芯片的介绍.92.2.2 D/A模块转换介绍93波形发生器的软件设计103.1各种波形模块设计与仿真113.1.1递增斜波产生模块设计与仿真113.1.2递减斜波产生模块设计与仿真113.1.3三角波产生模块设计与仿真12 3.1.4阶台波产生模块设计与仿真13 3.1.5正弦波产生模块设计与仿真14 3.1.6方波产生模块设计与仿真15 3.1.7波形选择模块设计与仿真16

2、3.2顶层设计.164 波形发生器的调试与运行.17 4.1波形发生器的调试.174.2FPGA的配置设计.20 4.2.1 管脚分配.20 4.2.2 下载.20结论21参考文献22附录.22致谢23插图索引图1查找表结构原理图6图2 FPGA的流程图7图3波形发生器的结构8图4芯片0832的内部结构图9图5波形发生器的软件模块10图6递增斜波仿真图17图7递减斜波仿真图18图8三角波仿真图.18图9阶台波仿真图.18图10正弦波仿真图.19图11方波仿真图 .19基于FPGA的多功能波形发生器的设计与实现摘 要应用EDA技术完成一个电子产品的设计, 以 FPGA芯片中集成一个在电子生产或检

3、测中通常用到波形发生器。在MAX+PLUS软件开发平台,输入原理图或硬件描述语言HDL完成的设计文件,系统将自动地完成逻辑编译、综合、仿真、目标芯片的适配编译、下载等的工作。设计的工作是利用编程的方式来进行对系统的功能的描述,在EDA工具的帮助下,应用相应的可编程器件,实现设计的最终结果。使常用到的波形发生器微型化,设计简单化,使用简单化。【关键词】:FPGA EDA 六种波形Design and implementation of multiple functions wave generator based on FPGAAbstractEDA application of technol

4、ogy to complete an electronic product design to FPGA chip integrated in a production or electronic detection function in usually used in signal generator。 MAX+PLUS in the software development platform for the importation of schematic or hardware description language HDL design document completed, th

5、e system will automatically compile the completion of logic, integrated, simulation, the goal of the chips fit to compile, download, and so on。 Design work is to use programming on the way to carry out the function of the system described in the EDA tools with the help of the appropriate application

6、 of the programmable devices, designed to achieve the final result。 Used to make the micro-function signal generator, simple design, simple to use。【Key words】:FPGA EDA Six kinds of waveform绪论EDA(electronic design automation,电子设计自动化)技术是现代电子工程领域的一门新技术。它提供了基于计算机和信息技术的电路系统设计方法。EDA技术的发展和推广应用极大地推动了电子工业的发展

7、,随着EDA技术的发展,硬件电子电路的设计几乎全部可以依靠计算机来完成。这样就大大缩短了硬件电子电路设计的周期从而使制造商可以快速开发出品种多批量小的产品,以满足市的众多需求。EDA技术的推广是当今世界的一个技术热点。EDA技术是现代电子工业中不可缺少的一项技术。传统设计应用分立元件或通用数字电路芯片,设计周期长,花费大,而且往往局部功能优化,而整体功能较差。EDA 以计算机为平台,根据硬件描述语言,如VHDL,自动地完成逻辑编译、化简分割、综合及优化,布局布线,仿真直至对特定目标芯片的适配编译,逻辑映射和编程下载等工作。以自顶向下的设计方法,使硬件设计软件化,摆脱了传统手工设计的众多缺点。其

8、方法简单,频率稳定度高,易于程控。随着EDA技术的深入发展,基于硬件描述语言的方法将有取代传统手工设计方法的趋势。尝试用VHDL设计来产生正弦波,其频率切换非常便捷,调试、修改也非常节省时间。FPGA是英文Field Programmable Gate Array的缩写,即现场可编程门阵列,它是在PAL、GAL、EPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个新概念,内部包括可配置逻辑模块CL

9、B(Configurable Logic Block)、输出输入模块IOB(Input Output Block)和内部连线(Interconnect)三个部分。它与分立元件相比,具有速度快、容量大、功耗小和可靠性高等优点。由于集成度高,设计方法先进、现场可编程,可以设计各种数字电路,因此,在通信、数据处理、网络、仪器、工业控制、军事和航空航天等众多领域内得到了广泛应用。不久的将来将全部取代分立数字元件,目前一些数字集成电路生产厂商已经停止了分立数字集成电路的生产。此外,FPGA还具有静态可重复编程和动态在系统重构的特性,使得硬件的功能可以像软件一样通过编程来修改。因此,FPGA技术的应用前景

10、非常广阔。VHDL(Very High Speed Integrated Circuit Hardware Description Language,超高速集成电路硬件描述语言)诞生于1982年,是由美国国防部开发的一种快速设计电路的工具,目前已经成为IEEE(The Institute of Electrical and Electronics Engineers)的一种工业标准硬件描述语言。相比传统的电路系统的设计方法,VHDL具有多层次描述系统硬件功能的能力,支持自顶向下(Top to Down)和基于库(LibraryBased)的设计的特点,因此设计者可以不必了解硬件结构。从系统设计

11、入手,在顶层进行系统方框图的划分和结构设计,在方框图一级用VHDL对电路的行为进行描述,并进行仿真和纠错,然后在系统一级进行验证,最后再用逻辑综合优化工具生成具体的门级逻辑电路的网表,下载到具体的FPGA器件中去,从而实现可编程的专用集成电路(ASIC)的设计。波形发生器在生产实践和科技领域中有着广泛的应用。例如在通信、广播、电视系统中,都需要射频(高频)发射,这里的射频波就是载波,把音频(低频)、视频信号或脉冲信号运载出去,就需要能够产生高频的振荡器。在工业、农业、生物医学等领域内,如高频感应加热、熔炼、淬火、超声诊断、核磁共振成像等,都需要功率或大或小、频率或高或低的振荡器。现在波形发生器

12、的实现方法通常有以下几种:(1)用分立元件组成的波形发生器:通常是单一波形发生器且频率不高,其工作不很稳定,不易调试。(2)可以由晶体管、运放IC等通用器件制作,更多的则是用专门的波形发生器IC产生。早期的波形发生器IC,如L8038、BA205、R2207/2209等,它们的功能较少,精度不高,频率上限只有300kHz,无法产生更高频率的信号,调节方式也不够灵活,频率和占空比不能独立调节,二者互相影响。(3)利用单片集成芯片的波形发生器:能产生多种波形,达到较高的频率,且易于调试。鉴于此,美国马克西姆公司开发了新一代波形发生器,它克服了(2)中芯片的缺点,可以达到更高的技术指标,是上述芯片望

13、尘莫及的。此波形发生器频率高、精度好,因此它被称为高频精密波形发生器IC。在锁相环、压控振荡器、频率合成器、脉宽调制器等电路的设计上都是优选的器件。1. EDA技术简介1.1 EDA的论述EDA(Electronic design automation)即电子设计自动化,它是近几年来迅速发展起来的将计算机软件。硬件。微电子技术交叉运用的现代电子学科,是20世纪90年代从CAD。CAM。CAT和CAE的概念发展而来的。EDA技术就是以计算机为工作平台。以EDA软件工具为开发环境。以硬件描述语言为设计语言。以ASIC为实现载体的电子产品自动化设计过程。在EDA软件平台上,根据原理图或硬件描述语言H

14、DL完成的设计文件,自动地完成逻辑编译。化简。分割。综合及优化。布局布线。仿真。目标芯片的适配编译。逻辑映射和编程下载等工作。设计者的工作只限于软件的方式来完成对就的硬件功能的描述了,要EDA工具的帮助下,就应用相应的FPGA器件就可以得到最后的设计结果。尽管目标系统是硬件,但整个设计和修改过程如同完成软件设计一样方便和高效。当然我们这说的是EDA是狭义的EDA,主要是指数字系统的自动化设计。在这设计中是基于MAX+PLUS为EDA的开发工具,以ALTERA生产的FPGA为核心芯片,采用康草科技的产品作为核心板,用这两者作为我们的桥梁,满足开发的需求。 在一切工作开始之前先了解下我们的工具FP

15、GA芯片和MAX+PLUS软件。目前我们的要求集成电路的集成度超来超高,由于需求的推使,经历了PLA。PAL。GAL至现在的FPGA。各种性能和集成度都不断改进,能实现的功能也不断地丰富,当然开发起来也变得容易和快速,相应的投资也越小。因为涉及到的面也非常广,在此只对用到的FPGA作简要的说明。FPGA器件在结构上,由逻辑功能块排列,它的结构可以分为三部分:可编程逻辑功能块;可编程I/O单元;可编程内部连线资源。可编程逻辑块是FPGA的主体,可以根据设计灵活改变其内部的连接,完成不同的逻辑功能;可编程I/O它们是芯片与外界电路的接口部分,完成不同电气特性下对I/O信号的驱动与匹配需求。可编程内

16、部连线资源是连通FPGA内部所有单元,连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。常见FPGA的可编程逻辑功能块结构主要有3种类型:查表结构、多路开关结构和多级与非门结构。查找表结构的FPGA用得相当的多,所以就以它的逻辑实现原理为例,如下图所示 图1 查找表结构原理图A,B,C,D由FPGA芯片的管脚输入后进入可编程连线,然后作为地址线连到查找表LUT,LUT中已经事先写入了所有可能的逻辑结果,通过地址查找到相应的数据然后输出,这样组合逻辑就实现了。 该电路中D触发器是直接利用LUT后面D触发器来实现。时钟信号CLK由I/O脚输入后进入芯片内部的时钟专用通道,直接连接到触发器的时

17、钟端。触发器的输出与I/O脚相连,把结果输出到芯片管脚,就完成了图1。1所示电路的功能。(以上这些步骤都是由软件自动完成的,不需要人为干预)FPGA的开发工具也是很多的, MAX+PLUS平台是由ALTERA公司的开发工具之一。1.2 EDA的开发流程做每一个工程跟画画一样,我们先要有准备好作画时的工具,比如纸、笔、墨。工具有了,更重要的就是思考应怎样出色地完成作品,都思考好了才动手画,最后得出满意的作品。在做每一个工程,在它的开发前都是要先了解它要用到哪些工具,它的基本的开发流程,它具体要经过哪些过程,这样在做工程时才不会乱作一团忙忙碌碌而无所获。现在我们拥有了开发所用到的软硬件。接下来就到

18、我们策划了。基于FPGA的开发流程如图2所示 : 图2 FPGA的流程图示图说明:构思是一开始的必要的一个项目构思,在它的之后才动手做我们的项目。建立工程是每个项目是着手做的第一步, MAX+PLUS以工程单元对设计过程进行管理。建立顶层图,可以这样理解,顶层图是一个容器,将整个工程的各个模块包容在里面,编译时就是将这些模块整合在一起。采用ALTERA公司提供的各种功能模块。MAX+PLUS软件环境里包含了大量的常用功能模块,例如计数器、累加器等等。如果采用这些功能模块将节省你许多宝贵的开发时间,带来事半功倍的效果。当然也可以自己去构造属于自己的功能模块。将各个功能模块用线连起来,这个过程就像

19、PROTEL连结各电器元件,把各个芯片连接起来,组成系统。这时设计的系统就差不多出来了,下一步要为该设计选择芯片载体,才真正在物理上实现系统功能。这一步的主要工作是:选择芯片型号,为顶层图的各个输入输出信号分配芯片的管脚,设置编译选项,目的是让编译器知道更多更好的信息。编译,这个过程像软件开发里的编译,但这过程比软件的编译要复杂得多,它毕竟最终要实现硬件里的物理结构,包含了优化逻辑的组合。综合逻辑以及布线等步骤。在MAX+PLUS这些集成环境会帮你自动完成这几个步骤的工作。如果设计出错了,系统就会有相应的提示,那么就要根据提示进行改正,直到编译成功。编译后会生成.SOF和.POF的文件,前者是

20、通过JTAG下载到FPGA内部,设计就能实现预期的功能,但断电后FPGA里的信息会丢失,后者可以下载到FPGA的配置芯片(EEPROM或FLASH芯片),掉电后这些配置信息不会丢失,重新上电后通过该配置芯片对FPGA的内部RAM进行配置。对于复杂的设计,工程编译了以后可以用MAX+PLUS的仿真功能或其它仿真软件(如MODELSIM)对设计反复进行仿真的验证,直到满足要求。1.3 EDA常用的开发工具EDA工具在EDA技术应用中占据极其重要的位置,EDA的核心是利用计算机完成电子设计全过程自动化,因此,基于计算机环境的EDA软件的支持是必不可少的。EDA工具大致可以分为如下5个模块: 1.设计

21、输入编辑器 2.仿真器 3.HDL综合器 4.适配器 5.下载器当然这样的分类并不是绝对的,现在往往把各个EDA工具集成在一起,如用到的MAX+PLUS。一、设计输入编辑器 设计输入编辑器是工程设计的第一部,常用的设计输入方法有HDL语言输入(目前用得最多的是Verilog和VHDL),原理图输入、IP CORE输入(是指那些已设计好了的模块)。二、仿真器它有很多仿真工具但在这讲述一下基于FPGA的HDL的仿真,按仿真的描述的能级别的不同,HDL仿真器可以分为单独或综合完成以下各步骤:系统级的仿真、行为仿真、RTL级仿真、门级时序仿真。这个过程按仿真是否考虑延时分类,可以分为功能仿真的时序仿真

22、,根据输入仿真文件的不同,可以由不同的仿真器完成,也可以由同一个仿真器完成。 三、HDL综合器 综合器的功能就是将设计者在EDA平台上完成的针对某个系统的HDL、原理图或状态图形描述,针对给定的硬件结构组件,进行编译、优化、转换和综合,最终获得门级电路甚至更底层的电路描述文件。由此可知综合器是软件描述与硬件实现的一座桥梁。综合的过程就是将电路的高级语言描述转换成低级的、可与FPGA的门陈列基本结构相映射的网表文件。四、适配器 适配器的功能是将由综合生成的网表文件配置于指定的目标器件中,产生最终的下载文件。适配器的目标器件(FPGA芯片)必须属于原综合器指定的目标器件系列。五、下载器 编程下载就

23、是把设计下载到对应的实际器件,实现硬件设计。2 波形发生器的硬件设计2.1波形发生器系统的结构通过波形发生器可以得到正弦波、三角波、方波。这些波形的生产都是通过FPGA的核心芯片,各种运算都在FPGA中进行,直接输出选择的波形。其总的结构示意图如3: 图3 波形发生器的结构其中CLK接在核心板上的50M的晶振,由于50M 的频率太高了,要对这个频率进行分频,为了简单起见,不再专门设计一个分频器,而调用MAX+PLUS里自带的计数器功能宏模块,采用计数器来代替分频器。RESET是用于复位之用,而SEL是用于波形的选择。通过了FPGA芯片和DAC0832就可以得到波形的输出。其中FPGA是波形发生

24、器系统的结构中的核心,相当于电脑的CPU。从DAC0832输出的是电流,如要在DAC0832要输出端输出电压,可以用一个运器,对输出波形进行I/V转换,在放大器在的输入端加一个可变电阻,即可得到所需幅值。对于芯片所用到的电源核心板上已有提供,可以直接用。2.2波形发生器所用的硬件介绍采用此技术的目的就是减少耗材,同时减小器件的体积提高性能,在相同的硬件结构系统中得到所需的功能。所以在这里用到的器件不多。波形发生器制作过程中用到的硬件有:4.5V的电源、以ALTERA公司生产的芯片,和以这个目标芯片为核心的核心板,核心板上有稳压管及其供电系统、50MHZ的晶振、SDRAM:8Mbyte、Flas

25、h:2Mbyte、提供配置模式:JTAG和EPCS,此外所有IO配置管脚通过插针引出,下载设计到目标芯片时用到的并口下载数据线;还用到选择波形的按钮。由于这些波形产生都是在FPAG芯片中产生,产生的都是数字信号,比如三角波,它从00000000,CLK来一个上升延信号系统会自动给它加1,变成了00000001,再把这个8位二进制的信号输出来,这样周而复始地工作。而FPGA是只数字信号处理器,在模拟号转换它是显得很无助的。所以在它的输出端接上一个数模转换器,把数字信号转换成模拟信号输出。所以它由两部分组成:数据产生,数据的转换。2.2.1 FPGA芯片的介绍1所要的频率就是把50MHZ的频率通过

26、分频的办法得到所要的频率。用通常的方法是专门设计一个分频器,但也可以通过调用MAX+PLUS自带的计数器的模块宏。用到设置设计宽度为256,即可取0到256分频范围,在这我们都选择为250,由此可以计算输出的频率:F=50MHZ/500=100KHZ。T=10微秒2可以用3个物理的按钮给波形选择的信号,但这样实行挺麻烦的,而且外围电路要复杂并也浪费了FPGA的片内资源。我们可以利用片内的资源去设计一个三位的六进制的加法计数器,用一个按钮就可以进行波形的选择。当复位时输出全为1,每按一次就是加法计数器就自动变为1,出来的就是选择波形的信号。3芯片的核心器件是波形发生器的处理部分。波形发生器是由正

27、弦波产生模块(sin)、三角波产生模块(delat)、方波产生模块(square)和输出波形选择模块(ch3a1)它们都是跟着输入的时钟的上升延而产生相应的数字信号,而输出到0832的则要由SEL产生的选择信号来决定。2.2.2 D/A转换模块介绍1D/A转换器的类型很多,从输入电路来说,一般的D/A转换器都带有输入寄存器,与微机能直接对接。在这采用DAC0832分辨率8位的D/A转换集成电路芯片。它具有连接简单,转换控制方便、价格低廉等特点,在各微机系统中得到广泛的应用。如下面是DAC0832的结构框图:图4 芯片0832的内部结构图 8位D/A转换器,实际上是一个T型电阻网络,在外部运算放

28、大器配合下完成D/A转换工作。DAC0832的内部包括两个8位寄存器、1个8位转换器和相应辅助电路:8位输入寄存器为第一级锁存器,它的锁存信号为ILE。当ILE为高电平、CS和WR1为低电平时,输入寄存器的输出随输入而变化。此后,WR1由低变高时,ILE变为低电平,此时,数据被锁存到输入寄存器中。我们这里这种工作方式。 8位DAC寄存器为第二级锁存器,它的锁存信号也称为通道控制信号。WR2和XFEB同时为低电平时,LE2为高电平,这时,8位的DAC寄存器的输出随输入而变化,此后,当WR2由低变高时,LE2变为低电平,将输入寄存器的信息锁存到DAC寄存器。2DAC0832内部有两个寄存器,能实现

29、双缓冲、单缓冲和直通三种工作方式。我们用DAC0832的单缓冲的工作方式,也就只有用一个寄存器受到控制,这时将另一个寄存器的有关控制信号预设置成有效,使之开通。3DAC0832C 以电流形式输出转换结果,若要得到电压形式的输出结果需另加I/V转换电路,这时可采用运算放大器。于我们用到的单极性输出电路,输出电压的格式为:Vout=-(DVref/256)式中D为输入数字量的十进制值。因为转换结果Iout1接运算放大器的反相端,所以式中有一个负号。若Vref=+5V,当D=0-255(00HFFH)时,Vout=-(04。98)V。调整运算放大器的调零电位器。可以对D/A芯片进行零点补偿,调节外接

30、于反馈回路的电位器RP1可以调整满量程。3 波形发生器的软件设计设计的波形发生器就是为了得到正弦波、三角波、方波这三种波形,并可通过按钮选择输出波形。波形发生器可以由正弦波产生模块(sin)、三角波产生模块(delat)、方波产生模块(square)和输出波形选择模块(ch3a1)。下图为波形发生器内部的顶层设计的规划图:图5 波形发生器的软件模块如图可以看到,控制输入有三大块,一个是个按钮的数据选择命令的输入,一个是时时钟输入,它的频率将决定输出波形的频率,还有一个是复位键。在芯片里面要处理的就有波形产生器产生相应的数据后输出8位的数据到数据选择模块中,通过按钮发出选择数据的指令,3选1的数

31、据选择器选择相应的数据进行输出,把这些数据输入D/A模块中,通过D/A模块对数据转换,在它的输出端就可得到相应的波形。3.1各种波形模块设计与仿真3.1.1正弦波产生模块设计与仿真运行MAX+PLUS软件建立工程,在此之间现在任意一个盘里建立一个名为Wave Generator(波形发生器)文件夹。依次点击File -new后弹出指定工程名的对话框,选择Text Editor file这项,确定点OK。出现一个文本输入框,点击保存按钮,在File Name输入sin.vhd,建立一个了设计正弦波的VHDL文档,使文件保存在Wave Generator文件夹里,进入了VHDL的编辑窗口。在文本输

32、入窗中输入正弦波的程序,然后进行编译与仿真。选择“000”的值,于是由上面的设置可以直接按波形仿真按钮,进入仿真介面.可在菜单中选择:PROCESSSimulator命令,也可以用工具栏的按钮.仿真介面与编译的差不多,只是STATUS下只有SIMULATOR状态进度,仿真完成了后它会提示你. 当提示信息提示仿真成功之后,可以看到如下的仿真波形, 如图6是正弦波形仿真结果:图6 正弦波仿真图可以从图6中观察得到OUT 是用十六进制的数来表示的,上面一个周期取了64个值, 从FE按程序选择的查表值输出,形成输出形成正弦波,达到了设计要求.当复位信号为零时复位,OUT 置00.当它的值为1时,各器件

33、开始工作,输出随CLK的上升延的到来而选择对应的值,与程序设置的正弦波一致, CS.WR同时也进入了工作状态,使得DAC0832进行转换。这也达到了设计的要求.CLK的输入时钟T=10US ,可以用计算正弦波的周期。它的一个周期它自加减了64次,自加减一次的时间就是10US,所以正弦波的周期是64*20=1280US。3.1.3三角波产生模块设计与仿真依次点击File -new后弹出指定工程名的对话框,选择Text Editor file这项,确定点OK。出现一个文本输入框,点击保存按钮,在File Name输入delta.vhd,建立一个了设计三角波的VHDL文档,使文件保存在Wave Ge

34、nerator文件夹里。进入了VHDL的编辑窗口,在文本输入窗中输入三角波的程序,然后进行运行与仿真。选择“010”的值,按仿真按钮可以直接进行仿真,提示信息提示你仿真成功之后,可以看到如下的仿真波形, 如图7是三角波波形仿真结果: 图7 三角波仿真图可以从图9中观察得到OUT 是用十六进制的数来表示的,从00自减到了0F后低位就自动置F,输出随线性递减,达到了设计要求.当复位信号为零时复位,OUT 置FF.当它的值为1时,各器件开始工作,输出随CLK的上升延的到来而跳变. CS.WR同时也进入了工作状态,使得DAC0832进行转换。这也达到了设计的要求。CLK的输入时钟T=10US ,可以用

35、计算递三角波的周期。它的一个周期从00H一直计数到FFH,再从FFH自减到00H 它自加减了256*2次,自加减一次的时间就是10US,所以三角波的周期是256*2*10=5120US,即5.12MS。3.1.6方波产生模块(square)依次点击File -new后弹出指定工程名的对话框,选择Text Editor file这项,确定点OK。出现一个文本输入框,点击保存按钮,在File Name输入square.vhd,建立一个了设计方波的VHDL文档,使文件保存在Wave Generator文件夹里。在文本输入窗中输入方波的程序。选择“101”的值,按仿真按钮可以直接进行仿真,提示信息提示

36、你仿真成功之后,可以看到如下的仿真波形, 如图8是方波形仿真结果:图8 方波仿真图可以从图8中观察得到OUT 是用十六进制的数来表示的,它的值经过128个时钟脉冲秒跳变一次,形成输出方波,也就是从00经过128个时钟脉冲后变为FF,从而实现了0101 的值变化,达到了设计要求.当复位信号为零时复位,OUT 置00.当它的值为1时,各器件开始工作,输出随CLK的相应的上升延的到来而改变相应的值,与程序设置的方波的要求是一致的,CS.WR同时也进入了工作状态,使得DAC0832进行转换。这也达到了设计的要求.CLK的输入时钟T=10US ,可以用计算方波的周期。它的一个周期持续了256个时钟周期,

37、所以方波的周期是256*10=2560US。3.1.7波形选择模块(ch3a1)依次点击File -new后弹出指定工程名的对话框,选择Text Editor file这项,确定点OK。出现一个文本输入框,点击保存按钮,在File Name输入ch3a1.vhd,建立一个了设计波性选择的VHDL文档,使文件保存在Wave Generator文件夹里。在文本输入窗中输入波性选择模块的程序,然后对该程序进行编译与仿真,波形选择模块是对所需要的波形进行选择。3.2 顶层设计这一步是把各个元件连接起来, 在MAX+PLUS里面提供多种选择。比如可以用VHDL语言里面自带的元件例化语句,把各元件端口通过

38、用VHDL的描述,系统按你的描述自动你连接。当然大家知道开发复杂的程序要花大量的心血,而且不小心容易出错。所以MAX+PLUS提供一个VHDL与原理图混合设计方式的平台,方法是使用VHDL语言描述底层模块,把VHDL描述的功能模块转换成对应的元件符号存在元件库中,再就用原理图设计方法设计顶层原理呼文件,在很多且复杂的设计中采用的是两者的结合,这样就可以减轻设计的工作量。在Wave Generator的文件夹中新建一个名为TOP的文件夹,用于存放顶层文件。利用上面的方法进入原理图设计系统,步骤如下: FILENEWDEVICE DESIGN FILE.执行后就可以进入原理图编辑窗口了.原理图输入

39、窗口左边有一竖工具栏,点击SYMBOL TOOL的快捷键进入元件库,在LIBRARIES:下面的窗口可以找到你要的元件符号.一般情况下它只有一个MAX+PLUS自带的库文件夹,里面包含有经常用到的与.或.非,异或,与非等门,也有输入输出端口,也有预定义的功能模块。如果你编译后执行了产生实体的步骤,就会在这里增加一个PROJECT文件夹,它下面的就是你设计的工程对应的元件符号,供你任意调用。如果要调用以前的设计,可能它不会在LIBRARIES:中显示出来,这时就要用NAME的对话框中调出所需的文件。选中了后它就会在右边的窗口显示.按OK就可以加进原理图设计窗口, 把在END文件夹中的设计文件调出

40、到编辑窗口,按照如图3的连线.在这要注意的是各模块的输出连接有两条线以上的线都就总线的来连接,而单一个的就用导线,就像PROTEL里面的原理图设计一样.不然在编译时会出错、保存、编译,通过之后就算结束我们软件方面的设计了.4 波形发生器的调试与运行4.1 波形发生器的调试经MAX+PLUS编译后,能产生所要的最终文件,可以下载到FPGA里面,实现你的功能。如果你只是想验证一下设计是否成功,可通过核心板的JTAG口把芯片的配置信息后下载到FPGA芯片内,掉电后配置信息丢失。如果要下载到非易失FLASH配置芯片(掉电后配置信息不丢失)里去,则将通过核心板上的EPCS1的下载口,把文件下载到配置芯片

41、中。要下载到这些文件到芯片中实现功能前,还可以用MAX+PLUS自带的仿真软件,进行波形的仿真。4.2把设计下载到目标器中运行整个设计的预期值与仿真得到的结果相同,也即是通过了在软件上的仿真。下一步要做的就是把设计下载到器件中去,验证硬件与软件的结合是否与预期值相一致。上面讲述到的仿真是设计参与了编译后,由软件自动分配了芯片的输入与输出引脚,进之去仿真,得出相应的仿真结果。但它的分配的引脚有时并不能满足我们的设计要求,所以MAX+PLUS提供了一个管脚分配的功能。为芯片分配管脚可以用MAX+PLUS软件里的TCL文件进行配置, 也可以用“ASSIGNMENTSPINS”菜单,用菜单命令直观且简

42、单。4.2.1管脚分配在菜单命令中运行“ASSIGNMENTSPINS”打开管脚分配的窗口,分配我们所用到的引脚:CLK分配到芯片的28脚; RESET分配到芯片的124脚;SEL分配到芯片的122脚; OUT0分配到芯片的160脚;OUT1分配到芯片的161脚; OUT2分配到芯片的162脚;OUT3分配到芯片的163脚; OUT4分配到芯片的164脚;OUT5分配到芯片的165脚; OUT6分配到芯片的166脚;OUT7分配到芯片的167脚; CS分配到芯片的168脚;WR分配到芯片的169脚。分配完成了就之后,把分配管脚的资料保存,然后进入原理图编辑的窗口,再按编译的按钮,再次编译的目的

43、是看管脚分配是否与合理。如果合理即会通过,如果不合理系统就会提示出错,那就需要你再次的分配。分配完成后我们可以查各端口分配管脚的情况,在原理图窗口下菜单命令VIEWSHOW PIN AND LOCATION ASSIGNMENTS 它会在端口显示各管脚分配的情况。4.2.2下载一、下载设置上面建工程时已选定了芯片型号,在这里就不用再做了。如果第一次使用下载线下载配置文件到FPGA,则需要在MAX+PLUS软件设置下载线的型号等信息。先将BYTEBLASTER 下载线接到PC机的并口,执行菜单TOOLSPROGRAMMER 打开下载界面,在HARDWARE SETUP可以看到 NO HARDAR

44、E,表示还没有设置下载线,点击 HARDWARE SETUP,弹出“HARDWARE SETUP”对话框,点击对话框中的“ADD HAEDWARE”,弹出“ADD HAEDWARE”对话框,点OK返回HARDWARE SETUP对话框,从“CURRENTLY SELECTED HARDWARE:”点击返回下载界面,可看到下载线已经被添加。二、将下载线一头与PC 连接,另一头插入到JTAG口或EPCS1的下载口。FPGA 核心板接上+5V电源。三、如果只是想调试一下设计是否成功,可以通过JTAG口把芯片的配置信息下载到FPGA芯片内,掉电后配置信息会丢失。此时下载界面的“MODE:”下拉列表应选

45、择“JTAG”,并选择工程中。SOF为后缀的文件夹进行下载。一切准备好了后就按STARD按钮就可以下载文件了。下载成功后,设计也就成功了。结论应用EDA技术用FPGA完成波形发生器,通过选择波形的按钮,实现四种波形的互相转换。利用示波器可以验证波形发生器与原定的设计的理论是相一致。用示波器的“+”端接在输出端的,另一端接上示波器的“-”,用按钮发送选择波形的信号,这样可以看到示波显的荧屏上有相应周期的波形。按住RESET按钮,无波形的输出,各器件都处于复位中。用FPGA完成波形发生器的方法与传统的方法相比较,硬件结构是相当简单的。大大减小了它的体积和重量。可以节去传统的烦琐的硬件设计和硬件组合

46、。易于使用,按下选择波形的选择按钮,即可选出你所需的波形。PFGA里面有的是有待连接的逻辑门、D触发器等器件,它的外围还要有EEPROM、SDRAM、FLASH与之相配合才可以正常工作,这一点可能会广泛应用FPGA来比较麻烦。随着技术的发展,如果把EEPROM、SDRAM、FLASH都集成要在FPGA中去,组成它的最小系统,这样的话将会,节去芯片外的线路设计,会得到更加广泛地的应用。 应用EDA技术完成波形发生器的设计,设计简单。 可以看到利用EDA技术完成一个电子设计,可以节省我们开发时间,从而提高大大地了我们的效率。采用新技术就是为了提高效率,快速完成设计任务。我们做一个项目时,所在追求的

47、也是快且高效率。不断地去快速掌握并能快速地应用新技术是我们做技术的人的基本素质。我们要注重自己在这方面的能力。当然我们不能废弃我们基本的东西学科基础,全面发展自己,这需要我不断去追求。参考文献1潘松,黄继业.EDA技术实用教程M.北京:科学出版社,2002:235-250.2陈美金.EDA程序设计M.北京:大学出版社,2000:257-275.3陈美加.基于FPGA数控源设计J.黎明学报,2003,35(6):13-18.4王文钦.高质量微波信号源发生器研制J.电子质量, 004(2):12-14.5郑凤涛,陈金佳. 基于CPLD 的数控正弦波的信号源的设计J. 黎明职业大学学报,2003.8

48、(1):2530.6 侯伯亨,顾新.VHDL硬件描述语言与数字逻辑电路设计M.西安:西安电子科技大学出版社,1999.7MAXIM 1993 NEW RELEASES DATA BOOK VOOL-UME I.8Configuring APEX20K.Z.A1tera公司,2000.9Jonath A. Titus, Chriotopher A Titus PeterR. Reny Microcomputer.Analog Converter Software and Hardware Interfacing.M. Davidg. Larsen:11-47.附录:1 正弦波产生程序:LIBRA

49、RY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY sin ISPORT(CLK,clr:IN STD_LOGIC; d:OUT integer range 0 to 255 );END sin;architecture behave of sin isbeginprocess(clk,clr)variable b: integer range 0 to 63;beginif clr=0 thenddddddddddddddddddddddddddddddddddddddddddddddddddd

50、ddddddddddddddnull;end case;end if;end process;end behave;2 三角波产生程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY DELTA IS PORT(CLK,RESET:IN STD_LOGIC; Q:OUT STD_LOGIC_VECTOR(7 DOWNTO 0);END delta;ARCHITECTURE BEHAVE OF DELTA ISBEGINPROCESS(CLK,RESET)VARIABLE M :STD

51、_LOGIC_VECTOR(7 DOWNTO 0);VARIABLE A:STD_LOGIC;BEGIN IF RESET=0 THEN M:=00000000;ELSIF RISING_EDGE(CLK) THENIF A=0 THENIF M=11111110 THENM:=11111111;A:=1;ELSE M:=M+1; -递增运算END IF;ELSE IF M=00000001 THENM:=00000000;A:=0;ELSEM:=M-1; -递减运算END IF;END IF;END IF;Q=M;END PROCESS;END BEHAVE;3 方波产生程序:LIBRARY

52、 IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY square ISPORT(CLK,clr:IN STD_LOGIC; Q:OUT integer range 0 to 255);END square;architecture behave of square issignal a: bit;beginprocess(clk,clr)variable cnt: integer; beginif clr=0 thena=0;elsif rising_edge(clk) thenif cnt63 th

53、en cnt:=cnt+1;else cnt:=0;a=not a;end if;end if;end process;process(clk,a)beginif rising_edge(clk) thenif a=1 thenq=255;elseq=0;end if;end if;end process;end behave;7 波形选择:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY CH6A1 ISPORT(KEY:IN STD_LOGIC_VECTOR(2 DOWNTO 0);p0,p1,p2,p3,p4,p5:IN STD_LOGIC_

54、VECTOR(7 DOWNTO 0);wr:out STD_LOGIC;cs:OUT STD_LOGIC;q: OUT STD_LOGIC_VECTOR(7 DOWNTO 0);END CH6A1;ARCHITECTURE BEHAVE OF CH6A1 ISSIGNAL A: BIT;BEGINPROCESS(KEY,A)BEGINif KEY=000 THEN q=p0 ;A=1; -按钮输入信号选择正弦波形输出ELSIF KEY=001 THEN q=p1;A=1; -按钮输入信号选择三角波形输出ELSIF KEY=010 THEN q=p2;A=1; -按钮输入信号选择方波波形输出ELSE q=P0;A=0;-当输入其它信号时选择器选择P0的数据但不进行转换END IF;END PROCESS;PROCESS(A)BEGINIF A=1 THENWR=0;CS=0;ELSE WR=0;CS=0;END IF;END PROCESS;END BEHAVE;致 谢非常感谢我系包本刚老师在完成本设计期间不厌其烦地指导我,并提出了许多相当有意义的建议的和见解,他乐于帮助学生和工作上兢兢业业精神促使我更快地完成此项设计。在此,对包本刚老师和许多在我遇到困难时给予指引和帮助的老师和朋友一并表示深深的敬意和感谢。21

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。