学习过程中遇到的版图问题

学习过程中遇到的版图问题

《学习过程中遇到的版图问题》由会员分享,可在线阅读,更多相关《学习过程中遇到的版图问题(16页珍藏版)》请在装配图网上搜索。

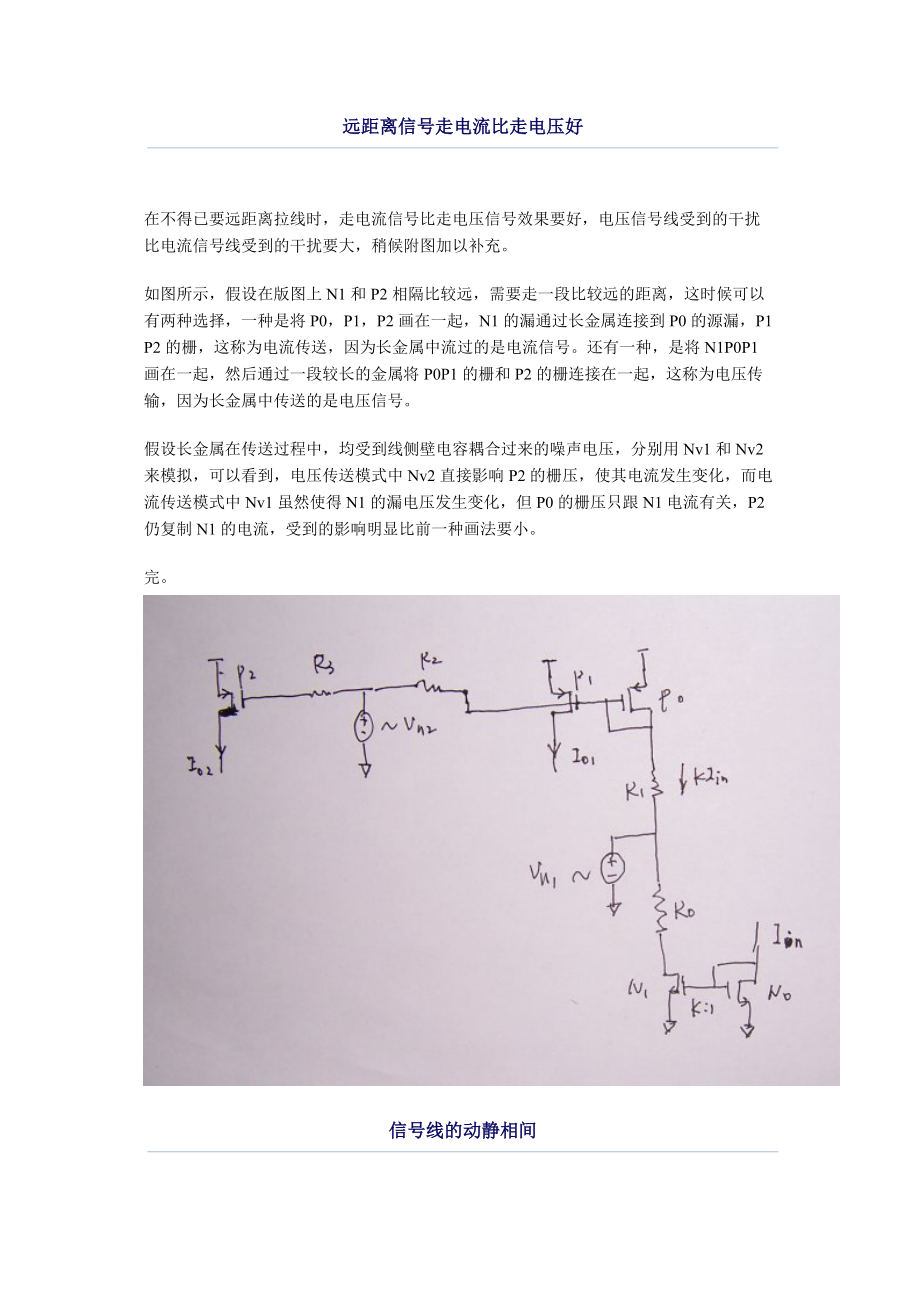

1、远距离信号走电流比走电压好 在不得已要远距离拉线时,走电流信号比走电压信号效果要好,电压信号线受到的干扰比电流信号线受到的干扰要大,稍候附图加以补充。如图所示,假设在版图上N1和P2相隔比较远,需要走一段比较远的距离,这时候可以有两种选择,一种是将P0,P1,P2画在一起,N1的漏通过长金属连接到P0的源漏,P1P2的栅,这称为电流传送,因为长金属中流过的是电流信号。还有一种,是将N1P0P1画在一起,然后通过一段较长的金属将P0P1的栅和P2的栅连接在一起,这称为电压传输,因为长金属中传送的是电压信号。假设长金属在传送过程中,均受到线侧壁电容耦合过来的噪声电压,分别用Nv1和Nv2来模拟,可

2、以看到,电压传送模式中Nv2直接影响P2的栅压,使其电流发生变化,而电流传送模式中Nv1虽然使得N1的漏电压发生变化,但P0的栅压只跟N1电流有关,P2仍复制N1的电流,受到的影响明显比前一种画法要小。完。信号线的动静相间动态信号线,如时钟线,快速变化的数据线如果靠得太近,线与线间的侧壁电容会大于我们的想像,由此电容耦合产生的干扰是比较严重的干扰。如果动态信号线两侧都是静态信号线,甚至是地线,或电源线,它们受到的干扰就会小得多,尤其是两侧用同层金属的地线夹住,会起到明显的保护作用。在条件不允许的情况下,比如地方不够,两边没有办法拉出两根地线,则尽量做到动态信号线和静态信号线相互交叠的方式走线。

3、比如,一根时钟线,旁边是一根运放的偏置电流线,再旁边是一根动态信号线,再旁边又是一条偏置电流线,这样的效果比时钟线和动态信号线并排走要好。走电流信号比走电压信号更好。数字模块和模拟模块的电源隔离数字地和模拟地都连接在衬底上,没有办法做到真正的隔离,唯一可采取的措施在于拉远两者地的距离。数字地的diff都可以打细一些,金属保持足够的宽度,以减少与analog之间的串扰。电源圈顺序为保险起见,不管是analog还是digital,电源圈都是地在外,电源在内。混合信号芯片的电源圈顺序混合信号集成电路中模拟部分和数字部分都要围两圈电源和地,有时候在数字和模拟之间要再加上一圈地,这样,从数字的core到

4、模拟的core之间一共是隔了五条宽线。按照一般的画法,模拟部分是电源放在内圈,地放在外圈,数字部分也是一样,都是地放在外圈。但是为了使电源和地之间的寄生电容更大,有时候需要这五条宽线的电源地交错出现,因此,电源和地谁在外谁在内也可以作适当调整。但一般来说,是应该地在外圈,电源在内圈。如果对数字部分不放心,可将其多围几圈围得像水桶一样,这样更稳妥。Digital电源线用多宽SE没有电源分析功能,如果用SE作PR,电源线的宽度要自己人为估计,是否够用也只能根据经验主观判断,工具也没有办法验证电源的线宽是否够用。因此,对数字PR的线宽有一个基本的概念还是很重要的。根据一般情况,digital部分的电

5、源线宽度约为digital部分总面积的1/100比较合适。比如,对于2000um*2000um的数字电路来说,电源线的宽度设为20um就比较合适,digital部分中间根据需要拉一些strip,strip的宽度可以适当减小一些,比如设为10um或者8um。对于0.5um工艺,每隔800um设一条strip比较合适。这些数据都是比较粗糙的估计,对于具体的项目,就有具体的应对,粗一点细一点都没有太大的影响CMOS工艺中浮阱的处理为避免沟道调制效应,有些MOS管的衬底和源接在一起,如果这时MOS的源不在电源或地方,则衬底需要一个单独的阱,称为浮阱。在我所见的工艺中,整片P衬底是连成一片的,所以浮阱只

6、限于N阱。浮阱需要单独的地围起来,这圈地不能再围其它不同电位的浮阱,稳妥的做法是浮阱边缘n阱以内打一圈nsubstreatering接源极,再在外圈p衬底上打一圈psubstrante接地,之外再打一圈nsubstratering接电源,即形成三圈guardring,这样就最好了。不过在实际项目中,没有做三圈ring的投片回来的东西也没有问题。在不允许的条件下,也可不打三圈ring,但不同电位的浮阱是不能放在同一个gndring中的。宽metal开槽的两个解释在0.5um工艺中,金属线宽超过30um,长超过500um中间要求开槽,这是为什么呢?有机械的和电气的两方面的原因。机械方面,金属太宽,

7、生产出来后更容易发生形变,容易“翘”起来,损坏芯片,这和我们的常识一致,开槽后,金属条局部变细,不容易“翘”起来。电气方面,宽金属中电流在电流的时候都是趋向在边缘流动的,金属中央的电流小,参考本站转载的“趋肤效应”一文。因此,开槽后有效增加了电流的流通途径,减少了金属被电子撞断(电迁移)的危险。这个原理也解释为什么金属和金属之间的via要打很多小的via而不是一整片大的via,因为很多个小的via在一起,它们的周长加起来比一个大的via要大得多,有效地导通了电流。运放版图的布局有哪些讲究运放的输入级都用差分形式的,讲究是做好对称和防止外来的干扰。具体做法是做二维的中心对称,在输入管的两侧加好d

8、ummy管,在最外围加上厚一点的guardring。对称管的连线比较绕,连线的时候让线从管子的外围绕,尽量不要在中心绕线。因为在中心绕线总要占用一些面积,这样对管就要拉开一些,这样不好。匹配性要求高的管子尽量靠得近一些。如果放大级也用差分形式的电路,则比照处理。电流偏置的管子单独画在一起,用guardring包起来。用作比较器的运放只对输入级要求较高,其它部分可灵活处理。数模混合版图中数字外圈该打substratecon吗常规的做法应该是打上substratecontact的,因为数字部分内部噪声是最大的,如果这些噪声泄露出来了,会对模拟版图有比较大的负面影响,把电源地用substrateco

9、ntact打到阱和衬底上可以把这些噪声都包围在数字版图内部。但这同样有一个问题,就是数字的地也打到substrate上,模拟的地也打到substrate上,那么数字和模拟的地岂不是接到一块儿了?这是一个值得商量的问题。一般还是建议数字电源和地打substratecontact,还有一个比较好的做法就是在模拟版图的周围除了自身的电源地之外还打上额外的一层衬底接触的地,越厚越好,这一圈地什么地方都不接,直接拉到gnd的PAD上,这样能更好地避免模拟部分被干扰。Layout空白处ESD保护管周围不宜填充MOS电容在版图工作的后期,会有一些空白处留出,可以填充一些电容来增加电源的洁净程度。如果芯片是c

10、orelimited,则PAD与PAD之间会空出一些空间,这些空间靠近ESD保护管,如果填充值较大的MOS电容,则很容易和ESD保护管之间发生LATCHUP,往往这样的空间不够大不足以让MOS电容和ESD保护管之间有足够的距离避免LATCHUP。因此,在ESD保护管周围填充电容只能是POLY电容,或其它形式的不带diffusion的电容。版图中空白处的利用不可避免地会在版图中出现空白处,这些空白处如果浪费会非常可惜,一般可以作如下三种处理:1,打上到地或到电源的接触孔。2,画上电源到地之间的电容。3,添加电源到地的ESD保护管。芯片的SealRing简介SealRing很容易和划片糟弄混。划片

11、槽叫Scribeline,是把芯片从晶圆上切下来的线,是要实际走刀子的地方,而SealRing是围在芯片周围的一圈从衬底到最上层金属全部都打一圈的保护圈。SealRing还找不到合适的中文翻译,它的作用有两个:主要作用是防止芯片在切割的时候的机械损伤,尤其是芯片的四个角一般都不要放重要器件;其次的作用是SealRing接地,屏蔽芯片外的干扰。SealRing从衬底(大多数是p衬底,n阱,称为n阱工艺),到pdiff,contact,metal1,mvia,metal2等等,直到最高层金属,这样芯片中每一层都有一个圈圈拦截,能很好地受到机械和电气保护SEALRING问题sealring中不是所有

12、层次都做,做的层一类是考虑连接,譬如P型注入,cont,met1,via,met2,这些层次使得sealring最终跟上层的地线连接;另一类与scribelane层次一致而且相连接,考虑到尽量减少scribelane的厚度(包括scribelane和sealring外面半圈),譬如pad,comp,这些在工艺中实际上会腐蚀掉厚的场氧化层或者最后的钝化层pad层通常不是加在整个seal ring上面的吧,而是沿着seal ring的边沿加的,同时在design rule里面可以看到划片道上的pad的区域mask的操作是clear的,也就是说,在工艺中,划片道上面的钝化层是被吃掉的,我个人感觉在s

13、eal ring上面加Pad层是为了在划片时减小崩片和裂片的风险。seal ring上的pad确实只是在靠外边缘很窄的一圈。版图中电源线的布局数模混合芯片中电源的走线分成三类,模拟电路的供电,数字电路的供电,ESD保护管的供电。即,模拟部分,数字部分,和PAD的ESD保护管的电源地都要从PAD上分别连接。对于模拟部分版图,电源和地的连接仍有一些讲究。我个人的做法是:整个模拟版图外圈围上电源和地,电源在内圈,地在外圈;根据线路的功能,将模拟版图分成一个一个子块,这些子块的外圈再围上电源和地;功能类似,或不会引起信号干扰的子块放在一起;电源是连接在N阱上的,比衬底要浅,对噪声的吸引效果比地要弱,因

14、此干扰源周围加比较宽的地连接;在空出来的地方根据需要交错加上到电源和地的contact,注意连线的走向和尖角的倒角处理;模拟版图放到芯片的一角,而不要放在中央用数字部分包围;bandgap中的pnp尽量放在远离数字版图的地方。浅谈ADC中电阻电容的画法ADC中电阻起到取样作用,对具体值不敏感,因此匹配性比较重要,要保证电阻链上从电源到地的电势均衡分配,在电阻的摆放上面要注意避免工艺梯度造成的影响。最理想的匹配方案是将电阻从上而下摆放好后,采用回形连接的方法,最上面的电阻条串到最下面的电阻条上,然后再往上,串到第二个电阻条上,再往下,串到倒数第二根电阻条上,直到所有电阻条连接完毕,这样的电阻链受

15、工艺梯度的影响最小。这样的连接方式连线较多,比较占面积,如果线路对取样精度要求不高,也可采用简化一点的蛇形连接方式。具体为,将从上至下的电阻条依次连接,再镜像复制这些电阻条,电源和地分别从这两列电阻条的最下方的电阻条连接,其它电平从中间抽取。ADC中的电容值呈金字塔分布,即从最大值电容,到最小值电容依次递减,在画这些电容时,同样要考虑到工艺梯度的影响。可将最小值电容画在中间,值稍大的电容依次围在周围,在最外圈加上dummy电容。这样连接电容最理想地避免了工艺梯度的影响,但在连线上有一些复杂。因为电容上的动态电流很小,因此连接这些电容时,可适当用较细的连线从空隙处连接出来,不必过多考虑连线电阻。

16、减小DRC运行时间的一个小技巧DRC运行的时候,根据版图图形的复杂程度和单元个数的不同,所用时间不一。图形越复杂,单元个数越多,运行时间越长。因此在调整版图时,每调整一个细节,有可能要耗上很长的时间来重新运行DRC,很大地阻碍了工作的进展。模拟版图的周边会围上两圈电源和地的环,一是起供电作用,二是吸收周围环境的噪声,因此这两个比较粗的环上面都要打上到衬底和井的contact,并且contact的数量会非常多。打上这些contact后DRC的运行速度会大大减慢,因为需要无数次地重复检查这些contact,比检查主要线路的DRC所耗时间多得多。因此,在版图LVS没有调通之前,可先去掉这些conta

17、ct,以及其它空白处的contact,在调通LVS之后,在最后统一加上这些contact,最后运行一次DRC,LVS,成功后即可留作下一步使用。这样的小技巧,能大大加快版图工作进程。1Foundry提供一种服务,允许客户在量产工艺加工进行到某个阶段的时候,让部分wafer暂时停止,而部分wafer继续加工。这样的话,客户可以在加工到poly层时(后面的金属层还没有做),停止大部分wafer的进程,而让少量wafer继续加工到完成,然后对这些已完成的wafer上的die进行测试,如果发现有功能或时序上的问题,就可能通过预先布在die上的 Spare cell来解决。只是改动几层金属层光罩就可以完

18、成std cell重新连接,而不用改动std cell的布局(要改poly层之前的所有光罩)。那些暂停加工的wafer这时就可以用新的金属层光罩往后加工,于是在silicon和光罩两方面都降低了成本。有时为了验证重连金属是否真的能解决问题,会在前面提到的先一步加工完的有问题die上进行FIB(Focus Iron Beam)操作,能够在不影响其它金属布线的前提下,打断有问题的金属连接,建立金属连接到合适的spare cell上,然后在测试die,如果再没有其它问题的话,就说明之前的金属重连接方案是可行的,这时再重新做金属层光罩就会更有把握些。然而要能进行FIB就必须在tapeout前对spar

19、e cell的金属连线方式做特殊处理。一般我们都把spare cell的输入输出端逻辑上接VDD或VSS,这样在后端工具自动布线时就会将spare cell的输入输出pin接到临近的VDD或VSS rail上,而rail是metal 1,对于FIB而言,这个连接太深了。为方便更改连接,还是应该让从spare cell输入输出pin引出的金属线连接到顶层金属层上。21、在中芯国际0.18(或者别的工艺也有)中的层有:NLL(1。8V NLDD implantation)、PLL(1.8V PLDD implantation)NLH(3.3V NLDD implatation)、PLH(3.3V

20、PLDD implatation)、DG(Dual GATE)等层表示什么意思,该如何使用?LDD: Ligthly doped Drain 浅掺杂源漏& r7 e6 v1 N9 Y1 s3 U1 R+ j) =半导体,微电子,集成电路,IC,工艺,设计,器件,封装,测试,MEMSMicroE.CN:微电中国网6 F( a+ w* 9 * J$ x目的:在短沟条件下,减小漏端电场强度,避免DBIL效应: T6 |# J& EL p9 s半导体,微电子,集成电路,IC,工艺,设计,器件,封装,测试,MEMS (Drain Induced Barrier Lowering).* z* Q- x9

21、T4 V0 R2 U) E/ z5 d: H8 _1 t: I! q( n2 _6 + WMicroE.CN:微电中国网 这是短沟器件制作过程中目前都会用到的工艺MicroE.CN:微电中国网& E1 M8 R, j- ?4 G6 , w5 Z& V& _: # s 至于3.3v/1.8v 则是对应不同VT管子在制作LDD结构中的# m: e; Y* M3 I, aMicroE.CN:微电中国网 掺杂浓度不同的,所以需要不同的mask来区分 为什么都用?diode用来做esd效率相对低一些,为了达到较强的效果,通常面积会很大。但通常是DIODE配合MOS使用,面积过大相应寄生就大,需要平衡.

22、二极管的寄生不是很大么,为什么在rf里面都用这个?二极管可以卸载高密度电流,面积相对MOS要小.短时间起作用,对CDM特别有效.为什么两个不同电位的阱放在一起更容易发生latch up两个NWELL和p型称底形成一个npn三极管,由于两个NWELL的电位不同,也就是有个VCE电压,如果称底有载流子经过使得三极管的VBE达到导通电压,那么三极管就会导通,从而发生LATCHUP.J9 x4 m4 j3 a# ; u( B. N半导体,微电子,集成电路,IC,工艺,设计,器件,封装,测试,MEMS为了防止这个寄生的三极管导通,应该怎么做呢?我的想法是在两个阱电位之间加一个P型环.这个p型环有两个作用

23、:一个是降低称底的电阻,使三极管不容易导通,第二个是吸收多数载流子也就是空穴. 不知道有没有必要在它们之间加一个NWELL环,这样会增加面积?为什么metal-2的厚度会变薄!一些老工艺会因为平坦化做的不好,形成poly或 metal的台阶,所以上层的金属在跨过这些部分的时候,厚度可能受到影响,从而影响过电流的能力,所以这部分金属有过电流要求的时候尽量不要用Min. Width,可以适当加宽一点工艺进步对后端工作影响有多大后端工艺变化带来的漏电流,功耗,以及整体设计上巨大的变化,从 .18 到 .09 可以说是革命性的变化, 以致后来的 .045 从设计上都可以说完全不同,很多甚至连物理原理都

24、不一样了,如出现了量子效应。主要是电器特性上的变化,工艺缩小以后,要多考虑诸如power analysis, IR drop, X-talk,这些附加的效应。前端设计师只关心逻辑上是不是能实现他所要的功能,芯片的电气特性需要后端工程师来把握。简单的说工艺每进步一代,如从。18到。13,器件面积会缩小一半,性能会提高1-2倍应该说尺寸越小,后端要考虑的问题越多,在。18甚至更大尺寸时,差不多不要跑SI,到了。09就好象很有这个必工艺越小,集成度越高,会带来散热和功耗的问题!还会出现量子效应!线宽越窄,会带来延迟和寄生的问题!电迁移和打孔的多少有什么关系如果没有防止电迁徙的措施,更多的孔会加强电迁

25、徙,主要是随着工艺尺寸的减小,孔的侧壁越来越陡峭,而铝蒸汽并非各向同性淀积,使得金属在经过氧化物台阶时变薄,导致导线横截面积减小,因而电流密度增大,加速了电迁徙。不过,目前工艺都有防护措施,比如使用在淀积铝制前,淀积一层难溶阻挡金属(各项同性淀积)来减小侧壁的陡峭度,现在用的最多的好像是钨塞。另外,金属层使用的不是纯铝,而是铝铜合金,而铜可以起到抑制电迁徙的作用。剩余空间加电源地线电容,加PMOS还是NMOS的简单分析用PMOS做电容的时候,PMOS的NWELL与衬底(p型)形成一个反偏二极管,当地线上来一个瞬间大电流,能通过这个来对mos电容栅极进行保护。当然,在栅极上加一个小电阻是常用的做

26、法。但是PMOS的电容比NMOS的电容小,如果不考虑ESD的可靠性方面,单从电容滤波方面考虑的话,NMOS应该比PMOS好模拟版图中带隙基准与振荡器的关系在模拟电路中这两者总是相生相依,电路都离不开时钟,时钟离不开振荡器,振荡器离不开偏置,偏置离不开电流源,电流源离不开带隙基准,这一连串的连带关系确定了这两者不可分离。当然,我们可以使用一个简单的电流源产生电路,在时钟要求不高的时候使用,而对于大多数芯片的模拟部分,带隙基准通常少不了。不幸的是,带隙基准对周边环境的要求高,不希望受到脉冲信号的干扰,而这样的脉冲信号恰恰来自振荡器,因此在模拟版图当中这两者的关系显得比较微妙而且难以处理。如果两者的

27、距离摆放太远,由基准源来的偏置电流要经过漫长的路途才能到达振荡器,难免受到其它信号的干扰;如果两者的距离太近,带隙基准又会受到振荡器的直接干扰。对于这样的困扰,一般这样处理。注意观察常规带隙基准的电路,一般在其放大器的输出部分的栅极会连接一个比较大的MOS电容,起到稳定输出的作用,这个电容相对放大器的差分对管和pnp管对于噪声的敏感度不高,可放在bandgap的边缘部分。为了吸收来自电源的电压波动带来的影响,bandgap输出会有一个减小电源波动的电路,其原理是比较bandgap的输出和电源的取样值,结果经比较器送到电源的下拉管,如果电源取样值高于bandgap输出值,则下拉管打开,减弱电源,

28、否则下拉管关闭。因此,可以利用这部分的取样电阻来达到隔离bandgap和振荡器的目的。在bandgap靠近振荡器的边缘,摆放上取样电阻,然后再用guardring隔离。振荡器部分,rc振荡器由两个比较器,取样电阻,和rc网络组成,在输出端会有rs触发器和输出驱动管。取样电阻上的电流电压变化小,放在振荡器边缘靠近bandgap的地方,然后放上rc网络,再放振荡器中的两个比较器,在最远离bandgap的一端放置输出rs触发器和驱动管。一般说来,这样的效果会比较好,以往投片的画法也都是这样的,没有出现什么问题,因此就一直继承了这种画法。运放版图的布局运放的输入级都用差分形式的,讲究是做好对称和防止外

29、来的干扰。具体做法是做二维的中心对称,在输入管的两侧加好dummy管,在最外围加上厚一点的guardring。对称管的连线比较绕,连线的时候让线从管子的外围绕,尽量不要在中心绕线。因为在中心绕线总要占用一些面积,这样对管就要拉开一些,这样不好。匹配性要求高的管子尽量靠得近一些。如果放大级也用差分形式的电路,则比照处理。电流偏置的管子单独画在一起,用guardring包起来。用作比较器的运放只对输入级要求较高,其它部分可灵活处理。运算放大器应用设计的几个技巧运算放大器在电路中发挥重要的作用,其应用已经延伸到汽车电子、通信、消费等各个领域,并将在支持未来技术方面扮演重要角色。在运算放大器的实际应用

30、中,设计工程师经常遇到诸如选型、供电电路设计、偏置电路设计、PCB设计等方面的问题。一、如何实现微弱信号放大?传感器+运算放大器+ADC+处理器是运算放大器的典型应用电路,在这种应用中,一个典型的问题是传感器提供的电流非常低,在这种情况下,如何完成信号放大?张世龙指出,对于微弱信号的放大,只用单个放大器难以达到好的效果,必须使用一些较特别的方法和传感器激励手段,而使用同步检测电路结构可以得到非常好的测量效果。这种同步检测电路类似于锁相放大器结构,包括传感器的方波激励,电流转电压放大器,和同步解调三部分。他表示,需要注意的是电流转电压放大器需选用输入偏置电流极低的运放。另外同步解调需选用双路的S

31、PDT模拟开关。另有工程师朋友建议,在运放、电容、电阻的选择和布板时,要特别注意选择高阻抗、低噪声运算和低噪声电阻。有网友对这类问题的解决也进行了补充,如网友“1sword”建议:1)电路设计时注意平衡的处理,尽量平衡,对于抑制干扰有效,这些在美国国家半导体、BB(已被TI收购)、ADI等公司关于运放的设计手册中均可以查到。2)推荐加金属屏蔽罩,将微弱信号部分罩起来(开个小模具),金属体接电路地,可以大大改善电路抗干扰能力。3)对于传感器输出的nA级,选择输入电流pA级的运放即可。如果对速度没有多大的要求,运放也不贵。仪表放大器当然最好了,就是成本高些。4)若选用非仪表运放,反馈电阻就不要太大

32、了,M欧级好一些。否则对电阻要求比较高。后级再进行2级放大,中间加入简单的高通电路,抑制50Hz干扰。二、运算放大器的偏置设置在双电源运放在接成单电源电路时,工程师朋友在偏置电压的设置方面会遇到一些两难选择,比如作为偏置的直流电压是用电阻分压好还是接参考电压源好?有的网友建议用参考电压源,理由是精度高,此外还能提供较低的交流旁路,有的网友建议用电阻,理由是成本低而且方便,对此,张世龙没有特别指出用何种方式,只是强调双电源运放改成单电源电路时,如果采用基准电压的话,效果最好。这种基准电压使系统设计得到最小的噪声和最高的PSRR。但若采用电阻分压方式,必须考虑电源纹波对系统的影响,这种用法噪声比较

33、高,PSRR比较低。三、如何解决运算放大器的零漂问题?有网友指出,一般压电加速度传感器会接一级电荷放大器来实现电荷电压转换,可是在传感器动态工作时,电荷放大器的输出电压会有不归零的现象发生,如何解决这个问题?对此,网友“Frank”分析道,有几种可能性会导致零漂:1)反馈电容ESR特性不好,随电荷量的变化而变化;2)反馈电容两端未并上电阻,为了放大器的工作稳定,减少零漂,在反馈电容两端并上电阻,形成直流负反馈可以稳定放大器的直流工作点;3)可能挑选的运算放大器的输入阻抗不够高,造成电荷泄露,导致零漂。网友“camel”和“windman”还从数学分析的角度对造成零漂的原因进行了详细分析,认为除

34、了使干扰源漂移小以外还必须使传感器、缆线电阻要大,运放的开环输入阻抗要高、运放的反馈电阻要小,即反馈电阻的作用是为了防止漂移,稳定直流工作点。但是反馈电阻太小的话,也会影响到放大器的频率下限。所以必须综合考虑!而嘉宾张世龙则建议,对于电荷放大器输出电压不归零的现象,一般采用如下办法来解决:1)采用开关电容电路的技巧,使用CDS采样方式可以有效消除offset电压;2)采用同步检测电路结构,可以有效消除offset电压。PLL画法参考首先,PLL电路中最大面积的是Low-PassFilter(LPF),我的作法都是放在PLL的最下边,同时,我会先计算MOS-C的size与要画的面积为何而整个PL

35、L会以LPF的最大X轴作为边界,然后往上画PLL其他block接下来,则是ChargePumpCircuit,会放在LPF的上边同时紧靠在最左边的位置,这个电路并不大,同时也是analogblock,所以,画完后要作ring围在外圈,并且,这个电路通常会设计成differentialcircuit,所以要特别注意matching,并且留意wire的连接再来则是Phase-Frequencydector(PFD)和pre-divider,这个电路是数位电路,不过,因为PFD中有些电路是要消除dead-zone现象的,故而有些元件的path要特别留意matching,而这点,要看设计者是用那一种P

36、FD电路,若没有特别交待,那layout人员是不会特别留心的再来则是VoltageControlOscillator(VCO),这是整个PLL电路中最难画的地方,同时也是最需要特别留意且小心的电路,一般设计者均会用differentialcircuit,所以,元件的对称要非常小心,同时,它是ring的形式,故而stage1到stage2的摆放位置与拉线要特别留意,同时要注意跨线与VDD和GND的跑线,因为一个不小心就会让VCO的jitter变大,同时也会造成phase-to-phase的误差变大,所以,VCO电路是最难画也需最小心的电路,建议在画这块电路时,一定要请设计者说明他想要layout

37、怎么摆放各个元件及拉线,通常,我会将这块电路放在LPF的上方且紧靠在最右边的地方,再者,因为这块电路不算小,所以,VCO的layout的高度大概是PFD+CP的layout高度最后一块电路则是post-divider,我通常是放在PLL的最上方,它是数位电路,没什么需要特别留意的地方,不过,有时候我们会把pre-divider和post-divider都放在同一块最后,PLL的信号连线顺序是由pre-divider进去,然后接到PFD,再到CP,再到LPF,再到VCO,最后到post-divider,所以,我的layout摆放位置也是依照此一顺序来走而不会有各个子电路交错的问题,所以,这些都是

38、原设计者要交待layout人员的地方。模拟设计的基本考虑1.Minimumchannellengthofthetransistorshouldbefourtofivetimestheminimumfeaturesizeoftheprocess.Wedoit,tomakethelambdaofthetransistorlowi.e.therateofchangeofIdw.r.ttoVdsislow.晶体管最小沟长为工艺最小特征尺寸的4-5倍,用来减小沟长调制效应2.Presentartofanalogdesignstillusesthetransistorinthesaturationregi

39、on.SooneshouldalwayskeepVgsoftheTransistor30%abovetheVt.目前模拟设计仍然是使晶体管工作在饱和区,故应使Vgs大于Vt约30%3.Oneshouldalwayssplitthebigtransistorintosmalltransistorshavingwidthorlengthfeaturesize应把大管分成小晶体管,使其宽/长特征尺寸或=15um4.W/LRatiooftransistorsofthemirrorcircuitshouldbelessthanorequalto5,toensurethepropermatchingoft

40、hetransistorsinthelayout.Otherwise,itresultstotheSystamaticOffsetinthecircuit.电流镜电路的晶体管的w/l比应小于或等于5,以保证较好的Matching,否则会有系统失调5.Oneshouldmakealltherequiredpinsintheschmeticbeforegeneratingthelayoutview.Becauseitsdiffculttoaddapininthelayoutview.AllIOpinsshouldbeametal2pinswhereasVddandGroundshouldbemet

41、al1pins在电路中画出所有的管脚(pin),之后才作layout。因为在layout中增加一个pin是比较困难的。所有的IOpin应该用metal2pin,Vdd和GND用metal1pin6.Oneshouldfirstsimulatethecircuitwiththetypicalmodelparametersofthedevices.SinceVtofthetrasistorcanbeanythingbetweenVt(Typical)-/+20%.Sowecheckourcircuitfortheextremecasesi.e.Vt+20%,Vt-20%.Atransistorha

42、vingVt-20%iscalledafasttransistorandtransistorhavingVt+20%iscalledslowtransistor.Itsjustawaytodifferentiatethem.Sowiththesefastandslowtransistormodelswemakefourcombinationcallednfpf,nfps,nspf,nsps,whichareknownasprocesscorners.Now,oncewearesatisfiedwiththecircuitperformancewithtypicalmodelsthanweche

43、ckitindifferentprocesscorners,totaketheprocessvariationintoaccount.Vtisjustoneexampleoftheprocessvariationthereareothersparametertoo.首先先用tt做电路仿真。考虑Vt有+20%(slow)和-20%(fast),需要对工艺角考虑,FF,SS,FS,SF。除Vt,其他工艺参数也会有变化7.Itsthumbrulethatpolyresistancehasa20%processvariationwhereaswellresistancehasgot10%.Butthe

44、polyresistancehasgotlowertemperaturecoefficentandlowerSheetResistancethanwellresistanceSowechoosetheresistancetypedependingupontherequirments.PolyCapacitancehasgotaprocessvariationof10%.多晶硅电阻大约有20%的工艺变化,而阱区电阻变化约为10%。但多晶硅电阻有较低的温度系数和低的方块电阻,应根据需要来选择电阻。多晶硅电容约有10%工艺变化8.Oneshouldalsocheckthecircuitperform

45、ancewiththetemperaturevariation.Weusulydoitfortherangeof-40Cto85C.需考虑温度变化对电路性能的影响,通常在-40C到85C范围9.Oneshouldtaketheparasiticcapacitanceintoaccountwhereveroneismakinganoverlapwithmetallayersorwells.有覆盖金属层或阱区时,须考虑寄生电容10.InLayout,alltransistorsshouldbeplacedinonedirection,toprovidethesameenvironmenttoall

46、thetransistors.Layout中,所有晶体管统一摆放方向,使有相同的环境11.Oneshouldplacealltransistorinlayoutwithaduecaretothepinpositionbeforestartroutingthem.在对晶体管布局布线之前,考虑Pin的位置12.OneshouldalwaysusetheMetal1forhorizontalroutingandMetal2fortheverticalroutingasfaraspossible.尽量使用metal1横向布线,metal纵向布线13.OneshouldneverusePOLYasrou

47、tinglayerwhentheinterconnectscarriesacurrent.Onecanhaveashortgateconnectionusingpoly.在互连用来传送电流时,不要用Poly来做互连。可以用poly做短的栅连接。14.Oneshouldtrytoavoidrunningmetaloverpolygate.Asthiscausetoincreaseinparasiticcapacitance.避免金属在多晶硅栅上走线,会增加寄生电容15.Currentinallthetransistorandresistorpartshouldflowinthesamedirec

48、tion所有晶体管和电阻有相同的电流走向16.OneshoulddothePower(Vdd&Gnd)routingintoplayermetal(metal5only).BecauseToplayermetalsareusuallythickerandwiderandsohaslowresistance.在最上层金属做电源(Vdd和GND)布线。因为最上层金属通常更厚、更宽,因而电阻较小17.Oneshouldalwaysmergedrainandsourceoftransistor(ofsametype)connectedtogether.merge连接的Source和Drain18.To

49、minimizetheprocessvariationintheResistorvalueoneshouldalwaystaketheresistorswidththreetofourtimesofthedefaultvalue.wedoittodecreasethevalueofdifferentialofR(L)为减小工艺变化对电阻影响,应使电阻的宽度为默认值的3-4倍19.Oneshouldcovertheresistancewithmetallayer,toavoidthedamagedduringthewaferleveltesting.用金属覆盖电阻,避免wafer级测试时的损伤2

50、0.OneshouldalwaysmakeaCommonCentroidstructureforthematchedtransistorinthelayout.Eachdifferentialpairtransistorshouldbedivideintofourtransistorsandshouldbeplacedintworowscommoncentroidstructure.Onemayusethethelinearcommoncentroidstructureforthecurrentmirrorcircuit.对匹配的晶体管用共中心的结构差分对管,分割为4管,2*2排列,共中心对电

51、流镜,可用线形共中心21.Itsadvisiabletoputadummylayersaroundtheresistanceandthecapacitancetoavoidtheerosionatthetimeofetching.建议在电阻和电容周围作dummy22.OneshouldalwayshaveaGuardRingarroundthedifferentialpair.在差分对周围作保护环23.AlwaysputaGuardRingarroundtheN-wellandP-well.在N阱和P阱作保护环半导体24.Thumbruleforthemetalcurrentdensityis

52、0.8mA/um.Itslargerforthetopmostmetallayer.金属电流密度0.8mA/um,最上层金属可以更大25.ToavoidtheLatchup,oneshouldalwaysmakethePNjunctionreversebiasedi.e.InNWELLshouldbeconnectedtopositivepowersupply(Vdd)andPWELLshouldbeconnectedtonegativepowersupply(Gnd).Designersdoittomaketheleakagecurrentsmall.为避免Latchup,应使PN结反偏,如

53、N-Well应连到正电源,P-Well应连到负电源。这样可减小漏电26.Itsalwaysagoodpracticetouseainfotextlayertoputthenameofthedeviceonthetopofitinlayoutandhaveanetnameforeverynetsinschematic.DesignershouldputthepinnameonthetopofthepinwithsamemetaltxtlayerbecausehercuelstakesthenetnamefrommetaltxtonlywhereasDivatakesfromthepin-name

54、.在layout中用infotext标明器件名称,在schematic中标明net。用相同的metaltxt层标明pin27.CadenceSPICEsimulatortakevdd!&gnd!asaglobalVddandGndneti.e.anynetendingwith!isconsideredasaglobalnet.Cadence模拟工具对以!结尾的net认为全局net28.TransistorEquation:Id=(beta/2)*square(Vgs-Vt)基本晶体管方程Id=(beta/2)*square(Vgs-Vt)布局优先还是连线优先手工画图的习惯做法是先把要用到的ce

55、ll摆上去再说,然后再考虑连线问题。比如,想把一个模块画成方块形状,则在画图的初期,把要用到的cell全部摆上去,根据各个管子的形状,摆成一个粗略的方块形,然后再加guardring,再连线。这样的做法一个大好处就是省事,不管是什么模块,按这一套流程走下来,总能把它布好,但也有弊端。如果按上述方法布好了图,在连线的时候,发现模块内部需要连到外面的管子被放到了模块的另一端,而相反的一端也有同样的情况,这样连线的时候难免要扯东扯西,造成连线复杂,工作量加大。同时,上述做法在信号的干扰和屏蔽方面完全没有考虑,只考虑了形状因素,这对于敏感电路是很糟糕的。因此,在布局比较精密的电路时,可考虑优先连线,后

56、考虑布局,这样,即使布出来的版图形状上抑合不好,甚至开天窗,却可以减少连线数量与信号串扰,是一个很好的布图思路。总的说来,画模拟版图的时候还是要根据电路功能来布图,要求不高的部分,优先考虑布局,对于有对称性要求,信号屏蔽要求,寄生参数大小有要求等的比较苛刻的电路,优先考虑这些因素是比较稳妥的做法。关于天线效应by yw 一条条长长的金属线或者多晶硅(polysilicon)等导体,就象是一根根天线,当有游离的电荷时,这些“天线”便会将它们收集起来,天线越长,收集的电荷也就越多,当电荷足够多时,就会放电。 IC现代工艺中经常使用的一种方法是离子刻蚀(plasma etching),这种方法就是将

57、物质高度电离并保持一定的能量,然后将这种物质刻蚀在晶圆上,从而形成某一层。理论上,打入晶圆的离子总的对外电性应该是呈现中性的,也就是说正离子和负离子是成对出现,但在实际中,打入晶圆的离子并不成对,这样,就产生了游离电荷。另外,离子注入(ion implanting)也可能导致电荷的聚集。可见,这种由工艺带来的影响我们是无法彻底消除的,但是,这种影响却是可以尽量减小的。在CMOS工艺中,P型衬底是要接地的,如果这些收集了电荷的导体和衬底间有电气通路的话,那么这些电荷就会跑到衬底上去,将不会造成什么影响;如果这条通路不存在,这些电荷还是要放掉的,那么,在哪放电就会对哪里造成不可挽回的后果,一般来讲

58、,最容易遭到伤害的地方就是栅氧化层。 通常情况下,我们用“天线比率”(“antenna ratio”)来衡量一颗芯片能发生天线效应的几率。“天线比率”的定义是:构成所谓“天线”的导体(一般是金属)的面积与所相连的栅氧化层面积的比率。随着工艺技术的发展,栅的尺寸越来越小,金属的层数越来越多,发生天线效应的可能性就越大,所以,在0.4um/DMSP/TMSP以上工艺,我们一般不大会考虑天线效应。而采用0.4um以下的工艺就不得不考虑这个问题了。 可通过插入二极管的方法来解决天线效应,这样当金属收集到电荷以后就通过二极管来放电,避免了对栅极的击穿。QUESTION:为什么跳到更高层的线能避免ANTENNA?

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。