毕业设计基于AT89C51单片机的多用户门铃设计

毕业设计基于AT89C51单片机的多用户门铃设计

《毕业设计基于AT89C51单片机的多用户门铃设计》由会员分享,可在线阅读,更多相关《毕业设计基于AT89C51单片机的多用户门铃设计(46页珍藏版)》请在装配图网上搜索。

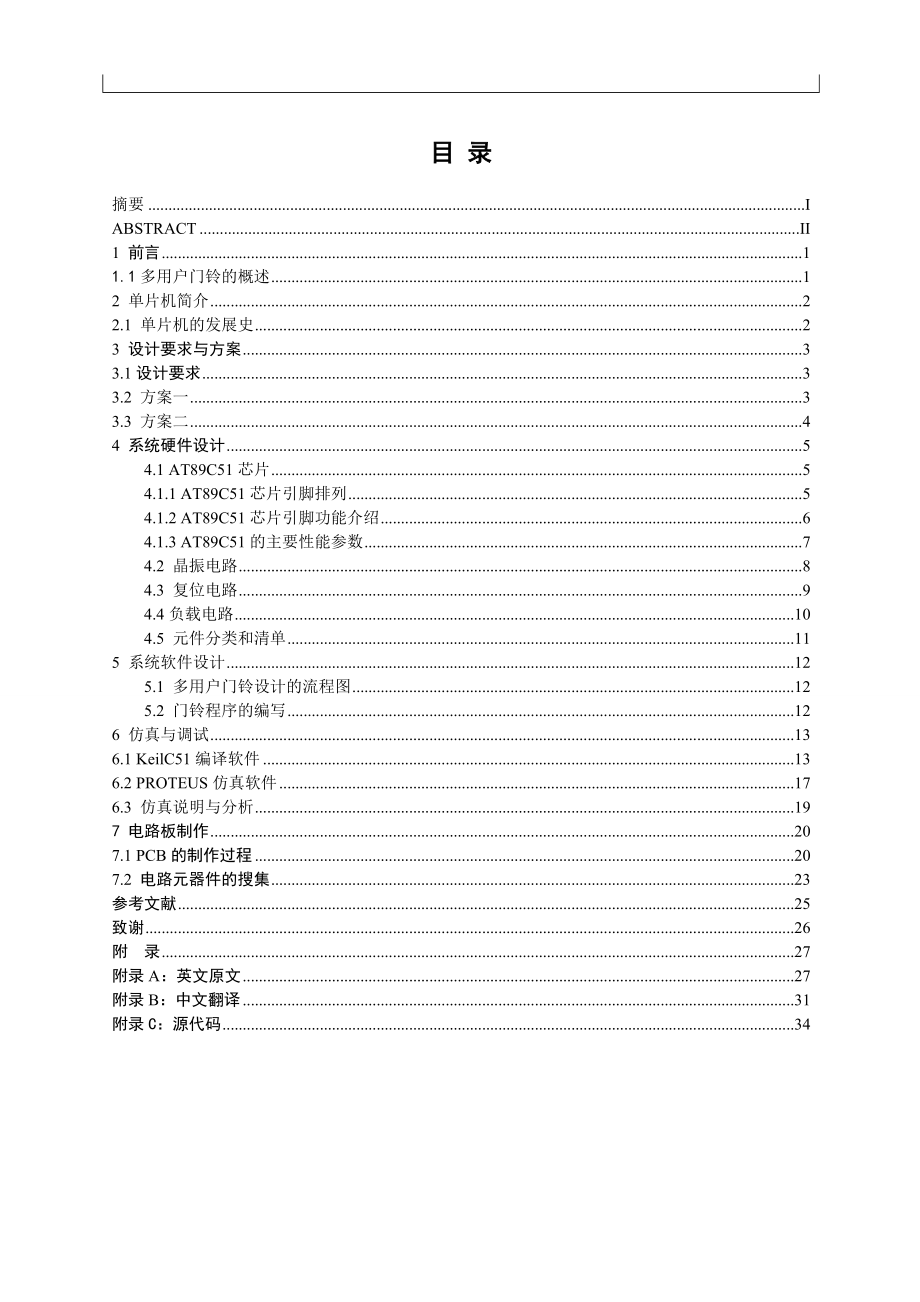

1、 目 录摘要IABSTRACTII1 前言11.1多用户门铃的概述12 单片机简介22.1 单片机的发展史23 设计要求与方案33.1设计要求33.2 方案一33.3 方案二44 系统硬件设计54.1 AT89C51芯片54.1.1 AT89C51芯片引脚排列54.1.2 AT89C51芯片引脚功能介绍64.1.3 AT89C51的主要性能参数74.2 晶振电路84.3 复位电路94.4负载电路104.5 元件分类和清单115 系统软件设计125.1 多用户门铃设计的流程图125.2 门铃程序的编写126 仿真与调试136.1 KeilC51编译软件136.2 PROTEUS仿真软件176.3

2、 仿真说明与分析197 电路板制作207.1 PCB的制作过程207.2 电路元器件的搜集23参考文献25致谢26附 录27附录A:英文原文27附录B:中文翻译31附录C:源代码34摘 要小区的安全受到越来越多人的重视,多用户门铃得到广泛应用。本文针对小区公寓楼的门铃进行设计,来访者只需要在楼下按下住户的门铃,相应住户家里的门铃就会响起,住户听到门铃的响起,可以按下室内开关控制楼下大门的开启。本文采用单片机AT89C51作为中央处理芯片,介绍了多用户门铃的设计及其软硬件调试结果。该多用户门铃方便了人们的生活,大大提高了小区的安全性,满足人们的生活需求。同时这个课题添加了报警的功能,进一步完善门

3、铃的功能。关键词:多用户门铃;单片机;AT89C51;报警;IABSTRACT The safety of Community drawing more and more attention, multi-user doorbell being widely applied. Aiming at the village apartment block to design, the doorbell of visitors only need to press resident doorbell downstairs and corresponding households will ring

4、the doorbell of home. Hearing the bell rang, the residents can press indoor switch control doors downstairs open. This paper mainly introduces the design idea of how the user the doorbell production methods and the whole manufacture process, multi-user doorbell adopts single-chip microcomputer AT89C

5、51 as central processing chip, this multi-user doorbell convenients to peoples life, greatly improves the village of security, satisfy peoples living needs. Key words: Multi-user doorbell;single-chip microcomputer;AT89C51;AlarmII1 前言 门铃在日常生活中已是随处可见了,特别是在城镇和大城市中,几乎是每家每户都有使用。随着人们生活水平的提高,小区的安全受到越来越多人的重

6、视,得到一种简便实用的门铃控制,不但可以保障小区的安全,而且能够提高人们的效率。本设计主要介绍了基于单片机的多用户门铃(四用户门铃)电路的设计,从画电路图开始到编写单片机C语言程序再到仿真再到绘制PCB板,本设计详细的介绍了整个设计的思路和制作流程,并且对使用到的软件(KEIL、PROTEUS)的使用方法和操作流程都有详细的说明。该多用户门铃以单片机AT89C51作为中央处理芯片,详细介绍了AT89C51的管脚结构和每个管脚的作用及各自的连接方法,使得该系统的功能扩展比较方便。AT89C51是美国ATMEL公司生产的低电压、高性能CMOS 8位单片机,片内含2k bytes的可反复擦写的只读程

7、序存储器(PEROM)和128bytes的随机数据存储器(RAM),器件采用ATMEL公司的高密度、非易失性存储技术生产,兼容标准MCS-51指令系统,片内置通用8位中央处理器和Flash存储单元,并且在掉电状态保存存储数据的特点,正是因为AT89C51具有以上的特点,所以很适合作为本次设计的中央处理芯片。1.1多用户门铃的概述由最初的手动敲门,到铃铛门铃,在到本设计制作的基于单片机的多用户门铃,这是门铃的一个发展历程。从最简单的门铃,到基于单片机的多功能门铃这是门铃的进步。随着科技的发展,人们生活水平的提高,生活节奏的加快。为了适应人们对门铃更高的要求,会不断有功能更加强大的门铃被研制出来。

8、本设计制作的基于单片机的多用户门铃是以芯片AT89C51为中央处理器芯片。主要完成对不同楼层用户之间的门铃应答。来访者只需要在楼下大门上的门铃按下相应住户的门铃,相应住户家里的门铃就会响起。住户听到门铃的响起,知道有来访者。可以按下室内开关,室内开关可以控制楼下大门的开启。该多用户门铃方便了人们的生活,提高了小区的安全性。2 单片机简介2.1 单片机的发展史(1)第1阶段(1971年1978年),以MCS-48系列为代表,称4位单片机。在片内:CPU有4位或8位;ROM有1KB或2KB;RAM有64B或128B;只有并行接口,无串行接口;只有1个8位的定时/计时器;中断源只有2个。在片外:寻址

9、范围只有4KB;芯片引脚有40个。(2)第2阶段(1978年1983年),以MCS-51系列为代表,称8位单片机。在片内:CPU有8位;ROM有4KB或8KB;RAM有128B或256B;有串/并行接口;有2个或3个16位的定时/计时器;中断源有5至7个。在片外:寻址范围有64KB;芯片引脚有40个。(3)第3阶段(1983年以后),以MCS-96系列为代表,称16位单片机。在片内:CPU有16位;ROM有8KB;RAM有232B;有串/并行接口;有4个16位的定时/计时器;中断源有8个;增加了D/A和A/D转换电路。在片外:寻址范围有64KB;芯片引脚有48个或68个1。以上MCS-51系列

10、以其优良的性价比,在我国得到了广泛的应用。3 设计要求与方案3.1设计要求设计的功能主要有两个:(1)当有人来访时,实现系统手动发出”叮 咚”的门铃响声;(2)当有危险或者异常发生时,可通过按钮实现报警提示;3.2 方案一根据设计要实现的功能,用一个简单的单片机驱动一个负载,根据选择负载的不同,可以实现不同的门铃响起不同的音乐,从而达到多用户控制的功能,具体控制方案如图3.1。由于芯片和负载的选择过于繁多,考虑到电路的简单性,经济性与实用性,该方案还需进一步改进。图3.1 方案一3.3 方案二考虑小区门铃要求的简单、经济、耐用等特点,选择AT89C51的P2口作为驱动端口,从而减少的芯片的数目

11、,简化电路。该方案可以驱动八个负载,本文选择四个,其余端口可作为扩展时使用。具体控制方案如图3.2。图3.2 方案二本设计选用第二种方案,即可实现多用户门铃的控制,技术含量、成本、设计周期也低,并且根据中央芯片检测门铃按钮是否按下。当按下时,单片机控制扬声器发出”叮 咚”的提示音,当有危险或者异常的情况下,由用户手动按下按钮提醒邻居或者房子里的人有危险需撤离,此设计适合本人此阶段自身的设计水平9。4 系统硬件设计门铃设计硬件电路包括单片机、晶振电路、复位电路和负载电路等8。现将各硬件及电路介绍如下:4.1 AT89C51芯片4.1.1 AT89C51芯片引脚排列AT89C51是标准的40引脚双

12、列直插式集成电路芯片,引脚分布可参照单片机引脚。P0.0P0.7 P0口8位双向线(在引脚的3239号端子);P1.0P1.7P1口8位双向线(在引脚的18号端子);P2.0P2.7P2口8位双向线(在引脚的2128号端子);P3.0P3.7P3口8位双向线(在引脚的1017号端子)。40号管脚VCC:电源+5V输入。20号管脚GND:接地。芯片AT89C51封装引脚排列如图4.1。图4.1 AT89C51芯片引脚排列4.1.2 AT89C51芯片引脚功能介绍VCC:电源电压;GND:地;P0口:P0口为一个8位漏级开路双向I/O口,每脚可吸收8TTL门电流。当P0口的管脚第一次写1时,被定义

13、为高阻输入。P0能够用于外部程序数据存储器,它可以被定义为数据/地址的第八位。在FIASH编时,P0 口作为原码输入口,当FIASH进行校验时,P0输出原码,此时P0外部必须被拉高。 P1口:P1口是一个内部提供上拉电阻的8位双向I/O口,P1口缓冲器能接收输出4TTL门电流。P1口管脚写入1后,被内部上拉为高,可用作输入,P1口被外部下拉为低电平时,将输出电流,这是由于内部上拉的缘故。在FLASH编程和校验时,P1口作为第八位地址接收。 P2口:P2口为一个内部上拉电阻的8位双向I/O口,P2口缓冲器可接收,输出4个TTL门电流,当P2口被写1时,其管脚被内部上拉电阻拉高,且作为输入。并因此

14、作为输入时,P2口的管脚被外部拉低,将输出电流。这是由于内部上拉的缘故。P2口当用于外部程序存储器或16位地址外部数据存储器进行存取时,P2口输出地址的高八位。在给出地址1时,它利用内部上拉优势,当对外部八位地址数据存储器进行读写时,P2口输出其特殊功能寄存器的内容。P2口在FLASH编程和校验时接收高八位地址信号和控制信号。 P3口:P3口管脚是8个带内部上拉电阻的双向I/O口,可接收输出4个TTL门电流。当P3口写入1后,它们被内部上拉为高电平,并用作输入。作为输入,由于外部下拉为低电平,P3口将输出电流(ILL)这是由于上拉的缘故。引脚具体说明如表4-1所示。 RST:复位输入。当振荡器

15、复位器件时,要保持RST脚两个机器周期的高电平时间。 ALE/:当访问外部存储器时,地址锁存允许的输出电平用于锁存地址的地位字节。在FLASH编程期间,此引脚用于输入编程脉冲。在平时,ALE端以不变的频率周期输出正脉冲信号,此频率为振荡器频率的1/6。因此它可用作对外部输出的脉冲或用于定时目的。然而要注意:每当用作外部数据存储器时,将跳过一个ALE脉冲。如想禁止ALE的输出可在SFR8EH地址上置0。此时,ALE只有在执行MOVX,MOVC指令是ALE才起作用。另外,该引脚被略微拉高。如果微处理器在外部执行状态ALE禁止,置位无效。 :外部程序存储器的选通信号。在由外部程序存储器取指期间,每个

16、机器周期两次/PSEN有效。但在访问外部数据存储器时,这两次有效的信号将不出现。 /VPP:当保持低电平时,则在此期间外部程序存储器(0000H-FFFFH),不管是否有内部程序存储器。注意加密方式1时,将内部锁定为RESET;当端保持高电平时,此间内部程序存储器。在FLASH编程期间,此引脚可用于施加12V编程电源(VPP)。 XTAL1:片内晶振电路反向放大器输出端接CPU内部时钟电路。 XTAL2:片内晶振电路反向放大器输出端。表4-1 AT89C51引脚说明引脚功能特性P3.0RXD(串行输入口)P3.1TXD(串行输出口)P3.2INTO(外中断0)P3.3INT1(外中断1)P3.

17、4T0(定时/计数器0外部输入)P3.5T1(定时/计数器1外部输入)4.1.3 AT89C51的主要性能参数(1)与MCS-51产品指令系统完全兼容 (2)2k字节可重擦写闪速存储器 (3)1000次擦写周期 (4)2.7V-6V的工作电压范围 (5)全静态操作:0Hz-24MHz (6)两级加密程序存储器4.2 晶振电路晶体振荡器,简称晶振。在电气上它可以等效成一个电容和一个电阻并联再串联一个电容的二端网络,电工学上这个网络有两个谐振点,以频率的高低分其中较低的频率是串联谐振,较高的频率是并联谐振。由于晶体自身的特性致使这两个频率的距离相当的接近,在这个极窄的频率范围内,晶振等效为一个电感

18、,所以只要晶振的两端并联上合适的电容它就会组成并联谐振电路。这个并联谐振电路加到一个负反馈电路中就可以构成正弦波振荡电路,由于晶振等效为电感的频率范围很窄,所以即使其他元件的参数变化很大,这个振荡器的频率也不会有很大的变化。晶振有一个重要的参数,那就是负载电容值,选择与负载电容值相等的并联电容,就可以得到晶振标称的谐振频率5。ATAL1和XTAL2T89S51引脚X与晶体振荡器及电容C2、C1按图4-2所示方式连接。晶振、电容C1C2及片内与非门(作为反馈、放大元件)构成了电容三点式振荡器,振荡信号频率与晶振频率及电容C1、C2的容量有关,但主要由晶振频率决定,范围在033MHz之间,电容C1

19、、C2取值范围在530pF之间。根据实际情况,对外接电容 C1,C2虽然没有十分严格的要求,但电容容量的大小会轻微影响振荡频率的高低,振荡器工作的稳定性,起振的难易程度及温度稳定性。如果使用石英晶体,推荐电容使用30PF10PF,而如使用陶瓷振荡器建议选择40PF10PF。本设计中采用12MHZ的晶振作为系统的外部晶振,电容取值为30pF。晶振电路原理图如图4.2所示。图4.2 晶振电路原理图4.3 复位电路当输入的信号连续2个机器周期以上高电平时即为有效,用以完成单片机的复位初始化操作,当复位后程序计数器PC=0000H,即复位后将从程序存储器的0000H单元读取第一条指令码。为了确保微机系

20、统中电路稳定可靠工作,复位电路是必不可少的一部分,复位电路的第一功能是上电复位。一般微机电路正常工作需要供电电源为5V5%,即4.755.25V。由于微机电路是时序数字电路,它需要稳定的时钟信号,因此在电源上电时,只有当VCC超过4.75V低于5.25V以及晶体振荡器稳定工作时,复位信号才被撤除,微机电路开始正常工作。电阻给电容充电,电容的电压缓慢上升直到VCC,没到VCC时芯片复位脚近似低电平,于是芯片复位,接近VCC时芯片复位脚近高电平,于是芯片停止复位,复位完成。 选择+5V的电源和10uF的极性电容外加一个10K的电阻就组成了复位电路,复位电路原理图如图4.3所示。图4.3 复位电路原

21、理图4.4负载电路负载电路主要是由一个PNP型三极管和一个2k欧电阻外加一个蜂鸣器组成的。当芯片有电平的变化就会使蜂鸣器导通,使其工作发出蜂鸣声,从而实现门铃的作用。考虑功耗低,经济性能高,本文所选的蜂鸣器为无源蜂鸣器,其额定电压为1.5V,工作电压范围为1.0-1.7V,最大电流0.2A,电阻6-10欧。经实测元件知其电阻为10欧姆。根据图4-4所构成的电路图计算如下:假设蜂鸣器在额定电压下工作,则集电极电流 根据集电极电流满足所选三极管的要求,最终选择PNP型S8550三极管。其耗散功率0.625W,S8550放大倍数40-140,集电极电流0.5A,集电极-基极电压40V ,集电极-发射

22、极击穿电压25V,集电极-发射极饱和电压 0.6V。本设计购买的三极管放大倍数为100。根据放大倍数基极电流 基极电阻 为了保证电路工作的可靠性,将电阻选大一些,且根据常用的电阻型号选择220欧姆的电阻。室内门铃电路原理图如图4.4所示。图 4.4 室内门铃电路原理图4.5 元件分类和清单基于单片机的多用户门铃的设计,所需要的元件的所属分类和清单列表如表4-2所示。表4-2 所需元件分类元件名称所属类所属子类元件个数AT89C51Microproce Bsor ICs8051 Family1CAPCapacitorsGeneric2CAP-ELECCapacitorsGeneric1CRYST

23、ALMiscellaneous-1RESResistorsGeneric14PNPTransistorsBipolar4SPEAKERERSpeakers & Sounders-5BUTTONSwitches & RelaysSwitches9LED-REDOptoelectronicsLEDs95 系统软件设计5.1 多用户门铃设计的流程图根据设计所要实现的功能,考虑到编程简洁,容易达到要求,多用户门铃的程序流程图如图5.1所示。图5.1 程序流程图5.2 门铃程序的编写程序主要完成的是在运行的时候给端口P1和P3置高电平,并且判断各个开关是否被按下,如若被按下就执行相应的程序,给相应的管脚

24、提供相应的电平,并且调用延时程序并以达到门铃响起或者LED灯点亮的效果。这就是这个程序需要完成的功能,根据电路图需要达到的效果,编写的C语言程序可以满足以上的所有要求。本设计的基于单片机的多用户门铃程序如附录C所示。6 仿真与调试6.1 KeilC51编译软件Keil C51是美国Keil Software公司出品的51系列兼容单片机C语言软件开发系统,与汇编相比,C语言在功能上、结构性、可读性、可维护性上有明显的优势,因而易学易用。用过汇编语言后再使用C来开发,体会更加深刻。Keil C51软件提供丰富的库函数和功能强大的集成开发调试工具,全Windows界面。Keil C51生成的目标代码

25、效率非常之高,多数语句生成的汇编代码很紧凑,容易理解6。首先,打开keil编译软件,然后在菜单栏上找到Project并选择New Project,在给工程命名并且保存工程,保存完成之后会弹出单片机芯片的选择框,找到芯片AT89C51并且这样就完成了在keil中新建工程的操作。如图6.1所示。图6.1 在keil中新建工程工程新建完成之后,在新建一个文本文件,并把程序录入到该文本文件当中。多用户门铃程序录入如图6.2所示。程序录入完成之后在菜单栏上找到File然后选择save保存,在弹出保存框里给文件命名,并且需要将该文件的后缀名修改成.c格式,如图6.3所示。 图6.2 录入门铃程序图6.3

26、保存程序把文件添加到工程中,首先在Source Group1点击右键找到Add Files to Group就把文件添加到工程中了,如图6.4所示。图6.4把文件添加到工程 在Option for Target对话框中,选中“Output”选项卡中的“Create HEX File”选项和“Debug”选项卡中的“Use:Proteus VSM Simula”选项。点击Build target编译C语言程序,检查程序是否有错,没错可以直接调用生成的.HEX文件。有错就改正程序中的错误,直到没有错误提示才能调用生成的HEX文件。本次设计的门铃程序通过编译,没有错误和提醒。如图6.5所示。图6.5

27、 编译程序图6.5编译程序时出现的提示翻译为:(1)Linking:连接中。(2)Program Size: data=13.0 xdata=0 code=552:程序大小:内部数据=13.0字节,外部数据=0字节,代码=552字节。(3)creating hex file from wzh:创建名为“wzh”的HEX文件。(4)wzh - 0 Error(s), 0 Warning(s) :“wzh”文件有0个错误,0个警告。6.2 PROTEUS仿真软件Proteus软件是英国Labcenter electronics公司出版的EDA工具(仿真软件)。它不仅具有其它仿真软件的仿真功能,还能

28、仿真单片机及外围器件。它是目前最好的仿真单片机的工具。虽然目前国内推广刚起步,但已受到从事单片机教学的教师、致力于单片机开发应用的科技工作者和单片机爱好者的青睐。在编译方面,它支持IAR、Keil和MPLAB等多种编译器7。Proteus 软件除了可以编辑设计电路原理图,还可以进行电路仿真。首先在画好的电路原理图中选中需要编写程序的芯片,并单击鼠标左键,打开Edition Component对话框,设置单片机晶振频率为12MHZ,在此窗口中的program file栏中,选择之前用keil软件生成的KEIL生成的HEX文件。在Proteus的菜单栏中选择file并Save Desig选项,保存

29、设计。在Proteus的菜单栏中,打开 Debug下拉菜单,在菜单中选中Use start/restart debugging选项,这样proteus中绘制的电路原理图就可以链接上,keil中生成的HEX文件进行仿真了。打开proteus软件,在File的下拉菜单中找到New Design新建Proteus并选择A4版面,然后保存,这样就完成proteus的新建了。如图6.6所示。图6.6 新建proteus A4版面把元件排布好后,使用导线将各个元件连接起来,最后绘制完成电路原理图,本设计的门铃电路原理图如图6.7所示。图6.7在proteus中绘制电路原理全图6.3 仿真说明与分析在pro

30、teus里仿真时,首先把画好的电路原理图,链接上keil中生成的.HEX文件进行仿真。在Proteus的菜单栏中,打开 Debug下拉菜单,在菜单中选中Use start/restart debugging选项。准备就绪可以直接仿真。按下相应的开关,观察电路的相应状态。当按下开关k1时,LS1就会相应的响起。按下开关k2时门铃LS2就会相应的响起,以此类推。当按下开关k5至k8的任意一个时LED灯就会点亮,并且延时0.5s,LED灯点亮就表示大门的开启。当按下连接外部中断INT0的按钮时,扬声器LS5会发出警报的响声,8个红色led灯也会顺时针旋转闪烁,每次都是点亮3个红色LED灯,仿真运行时

31、然后会不停循环点亮。在整个仿真中,已经实现了各个功能和达到了预期的效果。仿真结果如图6.8所示。图6.8软件仿真结果7 电路板制作7.1 PCB的制作过程7.1.1 PCB的布局和3D视图在Proteus软件中提供了从原理图设计到简单PCB制作以及仿真11,因为我的PCB涉及的元器件不多,所以我们选择Proteus中的ARES套件来进行绘制PCB,从Proteus中的ISIS套件中编译网表连接到ARES中进行布局,经过半个小时的小心布局,我的布局情况具体如下图7.1:图7.1 布局全图为了清楚的看到我们的布局是否合理与美观,Proteus软件提供了3D视图功能12,大家可以很直观的看到自己的布

32、局情况,我的3D视图如下图7.2:图7.2 3D视图效果7.1.2 PCB的布线与铺地铜布好局就要开始布线了,虽然在Proteus软件中提供了自动布线功能,但是自动布线之后还是要自己手动修改一些不如意的地方,因为我的设计不复杂,所以我选择自己手动布线,然后给PCB的顶层和底层进行铺地网络的铜皮,这是为了增加电路板的抗干扰性,布好线与铺好铜之后的效果图分别如下图7.3和7.4:图7.3 布线效果图图7.4 铺地效果图7.2 电路元器件的搜集为了更好的完成毕业设计,我特意从实习公司带回一些小器件,列如:电阻、电容、LED灯等等,但是还缺少AT89C51芯片、万能板、按钮、蜂鸣器等等,所以我利用周六

33、到北京的中发电子市场去配了这些,顺便了解一下电子世界,去了之后确实有很大的见识和收获。尽管我尽力的想把毕业设计做得更好一点,但是做出实物确实有点困难,对于我的这个设计而言,最大的困难是制造PCB板实物和烧写程序到单片机中,没能做出实物是毕业设计的一大遗憾,但是通过此次设计,我收获真的很大。下面我将我搜集的一些主要电子元器件通过图片放上来,具体如下图:图7.5 万能板图7.6 AT89C52芯片图7.7 电子元器件参考文献1 何立民.MCS-51系列单片机应用系统设计M.北京:航空航天大学出版社,1990:5-6.2 杨文龙.单片机原理与应用J.西安:西安电子科技大学出版社,1999:22-28

34、.3 潘永雄.新编单片机原理与应用M.西安电子科技大学出版社,2007:9-16.4 彭为.单片机典型系统设计实例精讲J.北京:电子工业出版社,2006:55-62.5 马忠梅.单片机的C语言应用程序设计M. 北京:航天航空大学出版社,2002:87-155.6 刘明. Keil Vision单片机技术与实践J.清华大学出版社,2010:6-27.7 江世明.基于Proteus的单片机应用技术M.电子工业出版社,2009:12-43.8 臧春华.电子线路设计与应用M.北京:高等教育出版社,2006:132-167.9 杨帮文.使用电子小制作精选J.人民邮电出版社,2006:89-109.10

35、冯育长.单片机系统设计与实例分析M.西安电子科技大学出版社,2005:74-95.11 Myke Predko著张晓林等译.电路原理与设计实例解析J,2003:36-78.12 杨帮文.使用电子小制作精选J.人民邮电出版社,2006:104-123. 致谢本设计是在老师的指导下完成的。首先,感谢老师在论文的选题、设计方案的确定、设计的进行以及最后的设计说明书的撰写整个过程中给予我细心的指引和教导,使我能顺利完成毕业设计。老师渊博的知识、敏锐的学术思维、严谨的治学态度、求实的科学态度和工作作风以及创新的工作精神,令我终身受益,是我毕生学习的典范,值此论文完成之际,谨向王少杰老师致以崇高的敬意和衷

36、心的感谢!除此以外,我还要感谢我实习公司各位给我技术帮助的各位前辈,在他们的帮助下我少走很多弯路,大大减少了我的设计工作量,以致我能准时完成毕业设计,在此次设计中,我真的收获很大,对51单片机的认识和了解比以前提升了很多很多最后,感谢培养教育我的大学,其浓厚的学习氛围,舒适的学习环境,我将终生难忘。在四年的大学生涯里,还得到众多老师的关心支持和帮助。在此,谨向老师们致以忠心的感谢和崇高的敬意!附 录附录A:英文原文Structure and function of the MCS-51 series Structure and function of the MCS-51 series one

37、-chip computer MCS-51 is a name of a piece of one-chip computer series which Intel Company produces. This company introduced 8 top-grade one-chip computers of MCS-51 series in 1980 after introducing 8 one-chip computers of MCS-48 series in 1976. It belong to a lot of kinds this line of one-chip comp

38、uter the chips have,such as 8051, 8031, 8751, 80C51BH, 80C31BH,etc., their basic composition, basic performance and instruction system are all the same. 8051 daily representatives- 51 serial one-chip computers . An one-chip computer system is made up of several following parts: (1) One microprocesso

39、r of 8 (CPU). (2) At slice data memory RAM (128B/256B),it use not depositting not can reading /data that write, such as result not middle of operation, final result and data wanted to show, etc. (3) Procedure memory ROM/EPROM (4KB/8KB ), is used to preserve the procedure , some initial data and form

40、 in slice. But does not take ROM/EPROM within some one-chip computers, such as 8031 , 8032, 80C ,etc. (4) Four 8 run side by side I/O interface P0 four P3, each mouth can use as introduction , may use as exporting too. (5) Two timer / counter, each timer / counter may set up and count in the way, us

41、ed to count to the external incident, can set up into a timing way too, and can according to count or result of timing realize the control of the computer. (6) Five cut off cutting off the control system of the source . (7) One all duplexing serial I/O mouth of UART (universal asynchronous receiver/

42、transmitter (UART) ), is it realize one-chip computer or one-chip computer and serial communication of computer to use for. ( 8) Stretch oscillator and clock produce circuit, quartz crystal finely tune electric capacity need outer. Allow oscillation frequency as 12 megahertas now at most. Every the

43、above-mentioned part was joined through the inside data bus .Among them, CPU is a core of the one-chip computer, it is the control of the computer and command centre, made up of such parts as arithmetic unit and controller , etc. The arithmetic unit can carry on 8 persons of arithmetic operation and

44、 unit ALU of logic operation while including one, the 1 storing device temporarilies of 8, storing device 2 temporarily, 8s accumulation device ACC, register B and procedure state register PSW, etc. Person who accumulate ACC count by 2 input ends entered of checking etc. temporarily as one operation

45、 often, come from person who store 1 operation is it is it make operation to go on to count temporarily , operation result and loopback ACC with another one. In addition, ACC is often regarded as the transfer station of data transmission on 8051 inside . The same as general microprocessor, it is the

46、 busiest register. Help remembering that agreeing with A expresses in the order. The controller includes the procedure counter , the order is depositted, the order decipher, the oscillator and timing circuit, etc. The procedure counter is made up of counter of 8 for two, amounts to 16. It is a byte

47、address counter of the procedure in fact, the content is the next IA that will carried out in PC. The content which changes it can change the direction that the procedure carries out . Shake the circuit in 8051 one-chip computers, only need outer quartz crystal and frequency to finely tune the elect

48、ric capacity, its frequency range is its 12MHZ of 1.2MHZ. This pulse signal, as 8051 basic beats of working, namely the minimum unit of time. 8051 is the same as other computers, the work in harmony under the control of the basic beat, just like an orchestra according to the beat play that is comman

49、ded. There are ROM (procedure memory , can only read ) and RAM in 8051 slices (data memory, can is it can write ) two to read, they have each independent memory address space, dispose way to be the same with general memory of computer. Procedure 8051 memory and 8751 slice procedure memory capacity 4

50、KB, address begin from 0000H, used for preserving the procedure and form constant. Data 8051- 8751 8031 of memory data memory 128B, address false 00FH, use for middle result to deposit operation, the data are stored temporarily and the data are buffered etc. In RAM of this 128B, there is unit of 32

51、byteses that can be appointed as the job register, this and general microprocessor is different, 8051 slice RAM and job register rank one formation the same to arrange the location. It is not very the same that the memory of MCS-51 series one-chip computer and general computer disposes the way in ad

52、dition. General computer for first address space, ROM and RAM can arrange in different space within the range of this address at will, namely the addresses of ROM and RAM, with distributing different address space in a formation. While visiting the memory, corresponding and only an address Memory un

53、it, can ROM, it can be RAM too, and by visiting the order similarly. This kind of memory structure is called the structure of Princeton. 8051 memories are divided into procedure memory space and data memory space on the physics structure, there are four memory spaces in all: The procedure stores in

54、one and data memory space outside data memory and one in procedure memory space and one outside one, the structure forms of this kind of procedure device and data memory separated form data memory, called Harvard structure. But use the angle from users, 8051 memory address space is divided into thre

55、e kinds: (1) In the slice, arrange blocks of FFFFH , 0000H of location , in unison outside the slice (use 16 addresses). (2) The data memory address space outside one of 64KB, the address is arranged from 0000H 64KB FFFFH (with 16 addresses ) too to the location. (3) Data memory address space of 256

56、B (use 8 addresses). Three above-mentioned memory space addresses overlap, for distinguishing and designing the order symbol of different data transmission in the instruction system of 8051: CPU visit slice, ROM order spend MOVC , visit block RAM order uses MOVX outside the slice, RAM order uses MOV

57、 to visit in slice. 8051 one-chip computer have four 8 walk abreast I/O port, call P0, P1, P2 and P3. Each port is 8 accurate two-way mouths, accounts for 32 pins altogether. Every one I/O line can be used as introduction and exported independently. Each port includes a latch (namely special functio

58、n register ), one exports the driver and a introduction buffer . Make data can latch when outputting, data can buffer when making introduction , but four function of passway these self-same. Expand among the system of memory outside having slice, four port these may serve as accurate two-way mouth o

59、f I/O in common use. Expand among the system of memory outside having slice, P2 mouth see high 8 address off; P0 mouth is a two-way bus, send the introduction of 8 low addresses and data / export in timesharing Output grade , P3 of mouth , P1 of P1 , connect with inside have load resistance of drawi

60、ng , every one of they can drive 4 Model LS TTL load to output. As while inputting the mouth, any TTL or NMOS circuit can drive P1 of 8051 one-chip computers as P3 mouth in a normal way . Because draw resistance on output grade of them have, can open a way collector too or drain-source resistance is

61、 it urge to open a way, do not need to have the resistance of drawing outerly . Mouths are all accurate two-way mouths too. When the conduct is input, must write the corresponding port latch with 1 first . As to 80C51 one-chip computer, port can only offer milliampere of output electric currents, is

62、 it output mouth go when urging one ordinary basing of transistor to regard as, should contact a resistance among the port and transistor base , in order to the electricity while restraining the high level from exporting P1P3 Being restored to the throne is the operation of initializing of an one-chip computer. Its main function is to turn PC into 0000H initially , make the one-chip computer begin to hold the conduct procedure from unit 0000H. Except that the ones that enter the system are initialized normally,as because

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。