数字电子技术第三版第三章课件

数字电子技术第三版第三章课件

《数字电子技术第三版第三章课件》由会员分享,可在线阅读,更多相关《数字电子技术第三版第三章课件(104页珍藏版)》请在装配图网上搜索。

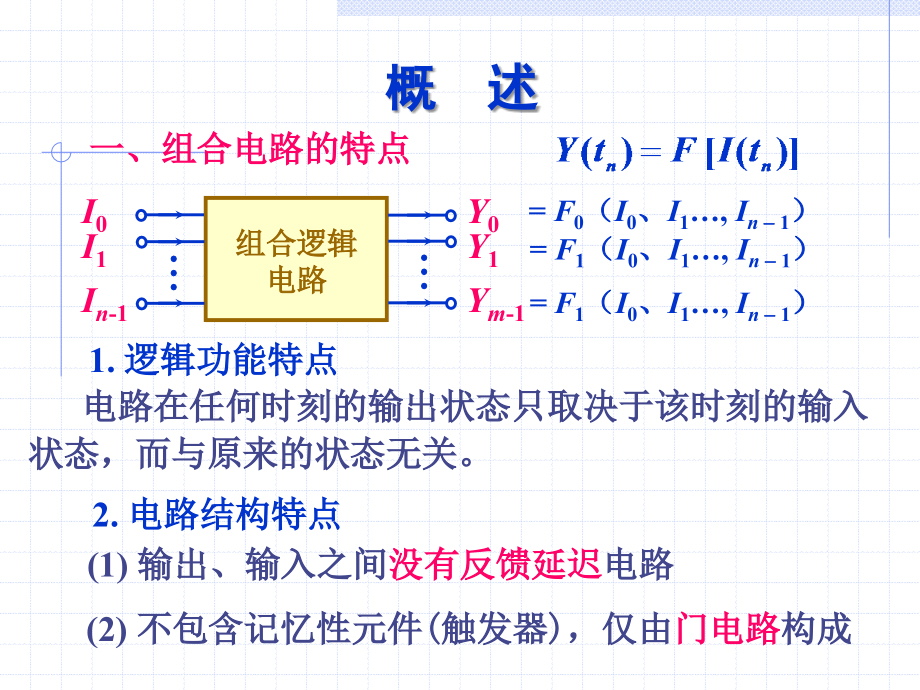

1、概概 述述一、组合电路的特点一、组合电路的特点=F0(I0、I1,In-1)=F1(I0、I1,In-1)=F1(I0、I1,In-1)1.逻辑功能特点逻辑功能特点 电路在任何时刻的输出状态只取决于该时刻的输入电路在任何时刻的输出状态只取决于该时刻的输入 状态,而与原来的状态无关。状态,而与原来的状态无关。2.电路结构特点电路结构特点(1)输出、输入之间输出、输入之间没有反馈延迟没有反馈延迟电路电路(2)不包含记忆性元件不包含记忆性元件(触发器触发器),仅由,仅由门电路门电路构成构成I0I1In-1Y0Y1Ym-1组合逻辑组合逻辑电路电路二、组合电路逻辑功能表示方法二、组合电路逻辑功能表示方法

2、真值表,卡诺图,逻辑表达式,时间图真值表,卡诺图,逻辑表达式,时间图(波形图波形图)三、组合电路分类三、组合电路分类1.按逻辑功能不同:按逻辑功能不同:加法器加法器 比较器比较器 编码器编码器 译码器译码器 数据选择器和分配器数据选择器和分配器 只读存储器只读存储器2.按开关元件不同:按开关元件不同:CMOS TTL3.按集成度不同:按集成度不同:SSI MSI LSI VLSI3.1 组合电路的分析方法和设计方法组合电路的分析方法和设计方法3.1.1 组合电路的基本分析方法组合电路的基本分析方法一、一、分析步骤分析步骤逻辑图逻辑图逻辑表达式逻辑表达式化简化简真值表真值表说明功能说明功能分析目

3、的:分析目的:(1)确定输入变量不同取值时功能是否满足要求;确定输入变量不同取值时功能是否满足要求;(3)得到输出函数的标准与或表达式,以便用得到输出函数的标准与或表达式,以便用 MSI、LSI 实现;实现;(4)得到其功能的逻辑描述,以便用于包括该电路的系得到其功能的逻辑描述,以便用于包括该电路的系 统分析。统分析。(2)变换电路的结构形式变换电路的结构形式(如:如:与或与或 与非与非-与非与非);二、二、分析举例分析举例 例例 分析图中所示电路的逻辑功能分析图中所示电路的逻辑功能表达式表达式真值表真值表A B CY0 0 00 0 10 1 00 1 1A B CY1 0 01 0 11

4、1 01 1 111000000功能功能判断输入信号极性是否相同的电路判断输入信号极性是否相同的电路 符合电路符合电路ABC&1 解解 例例 3.1.1 分析图中所示电路的逻辑功能,输入信号分析图中所示电路的逻辑功能,输入信号A、B、C、D是一组二进制代码。是一组二进制代码。&ABCDY 解解 1.逐级写输出函数的逻辑表达式逐级写输出函数的逻辑表达式WX&ABCDYWX2.化简化简3.列真值表列真值表A B C DA B C DYY0 0 0 00 0 0 10 0 1 00 0 1 10 1 0 00 1 0 10 1 1 00 1 1 11 0 0 01 0 0 11 0 1 01 0 1

5、 11 1 0 01 1 0 11 1 1 01 1 1 111111111000000004.功能说明:功能说明:当输入四位代码中当输入四位代码中 1 的个数为奇数时输出的个数为奇数时输出为为 1,为偶数时输出为,为偶数时输出为 0 检奇电路检奇电路。例:分析如下逻辑电路并加以改进例:分析如下逻辑电路并加以改进。逻辑图逻辑图逻辑表达逻辑表达式式例:例:例:例:最简与或最简与或表达式表达式真值表真值表用与非门实现用与非门实现电路的输出Y只与输入A、B有关,而与输入C无关。Y和A、B的逻辑关系为与非运算的关系。电路的逻辑功能电路的逻辑功能3.1.2 组合电路的基本设计方法组合电路的基本设计方法一

6、、一、设计步骤设计步骤逻辑抽象逻辑抽象列真值表列真值表写表达式写表达式化简或变换化简或变换画逻辑图画逻辑图逻辑抽象:逻辑抽象:1.根据根据因果关系因果关系确定输入、输出变量确定输入、输出变量2.状态赋值状态赋值 用用 0 和和 1 表示信号的不同状态表示信号的不同状态3.根据功能要求列出根据功能要求列出真值表真值表 根据所用元器件根据所用元器件(分立元件分立元件 或或 集成芯片集成芯片)的情况将的情况将函数式进行化简或变换。函数式进行化简或变换。化简或变换:化简或变换:(1)设定变量:)设定变量:二、二、设计举例设计举例 例例 3.1.2 设计一个表决电路,要求输出信号的电平设计一个表决电路,

7、要求输出信号的电平与三个输入信号中的多数电平一致。与三个输入信号中的多数电平一致。解解 输入输入 A、B、C ,输出输出 Y(2)状态赋值:)状态赋值:A、B、C=0 表示表示 输入信号为低电平输入信号为低电平Y=0 表示表示 输入信号中多数为低电平输入信号中多数为低电平1.逻辑抽象逻辑抽象A、B、C=1 表示表示 输入信号为高电平输入信号为高电平Y=1 表示表示 输入信号中多数为高电平输入信号中多数为高电平2.列真值表列真值表ABCY0 0 00 0 10 1 00 1 11 0 01 0 11 1 01 1 1000101113.写输出表达式并化简写输出表达式并化简最简与或式最简与或式最简

8、与非最简与非-与非式与非式4.画逻辑图画逻辑图 用与门和或门实现用与门和或门实现 用与非门实现用与非门实现ABYC&1&例例 设计一个监视交通信号灯工作状态的逻辑电设计一个监视交通信号灯工作状态的逻辑电路。正常情况下,红、黄、绿灯只有一个亮,否则视路。正常情况下,红、黄、绿灯只有一个亮,否则视为故障状态,发出报警信号,提醒有关人员修理。为故障状态,发出报警信号,提醒有关人员修理。解解 1.逻辑抽象逻辑抽象输入变量:输入变量:1-亮亮0-灭灭输出变量:输出变量:R(红红)Y(黄黄)G(绿绿)Z(有无故障有无故障)1-有有0-无无列真值表列真值表R Y GZ0 0 00 0 10 1 00 1 1

9、1 0 01 0 11 1 01 1 1100101112.卡诺图化简卡诺图化简RYG0100 01 11 10111113.画逻辑图画逻辑图&1&111RGYZ 组合逻辑电路部件组合逻辑电路部件 组组合合逻逻辑辑部部件件是是指指具具有有某某种种逻逻辑辑功功能能的的中中规规模模集集成成组组合合逻逻辑辑电电路路芯芯片片。常常用用的的组组合合逻逻辑辑部部件件有有加加法法器器、数数值值比比较较器器、编编码码器器、译译码码器器、数据选择器和数据数据选择器和数据分配器分配器等。等。3.2 加法器和数值比较器加法器和数值比较器3.2.1 加法器加法器一、半加器和全加器一、半加器和全加器1.半加器半加器(H

10、alf Adder)两个两个 1 位二进制数相加不考虑低位进位。位二进制数相加不考虑低位进位。0 00 11 01 10 01 01 00 1真真值值表表函数式函数式Ai+Bi=Si(和和)Ci(进位进位)逻逻辑辑图图曾曾用用符符号号国国标标符符号号半加器半加器(Half Adder)Si&AiBi=1CiCOSiAiBiCiHASiAiBiCi函函数数式式2.全加器全加器(Full Adder)两个两个 1 位二进制数相加,考虑低位进位。位二进制数相加,考虑低位进位。Ai+Bi +Ci-1 (低位进位低位进位)=Si (和和)Ci (向高位进位向高位进位)1 0 1 1-A 1 1 1 0-

11、B+-低位进位低位进位100101111真真值值表表标准标准与或式与或式A B Ci-10 0 00 0 10 1 00 1 11 0 01 0 11 1 01 1 1SiCiA B Ci-1SiCi0 01 01 00 11 00 10 11 1-S高位进位高位进位0卡诺图卡诺图全加器全加器(Full Adder)ABC0100 01 11 101111SiABC0100 01 11 101111Ci最简与或式最简与或式逻辑图逻辑图(a)用用与门与门、或门或门和和非门非门实现实现曾用符号曾用符号国标符号国标符号COCISiAiBiCi-1CiFASiAiBiCi-1Ci&1111AiSiCi

12、BiCi-11(b)用用与或非门与或非门和和非门非门实现实现&1&1111CiSiAiBiCi-13.集成全加器集成全加器TTL:74LS183CMOS:C661双全加器双全加器1 2 3 4 5 6 714 13 12 11 10 9 8C661C661VDD 2Ai2Bi 2Ci-1 1Ci 1Si 2Si 1Ci-1 2Ci 1Ai1Bi VSS 7474LS183LS183VCC 2Ai2Bi 2Ci-1 2Ci 2Si VCC 2A 2B 2CIn 2COn+1 2F1A1B 1CIn1FGND1Ai1Bi1Ci-11Si地地1Ci1COn+1 二、加法器二、加法器(Adder)实现

13、多位二进制数相加的电路实现多位二进制数相加的电路1.4 位串行进位加法器位串行进位加法器特点:特点:电路简单,连接方便电路简单,连接方便速度低速度低=4 tpdtpd 1位全加器的平均位全加器的平均 传输延迟时间传输延迟时间C0S0B0A0C0-1CO CIC1S1B1A1CO CIC2S2B2A2CO CIC3S3B3A3CO CI2.超前进位加法器超前进位加法器 作加法运算时,总进位信号由输入二进制数直接作加法运算时,总进位信号由输入二进制数直接产生。产生。特点特点优点:速度快优点:速度快缺点:电路比较复杂缺点:电路比较复杂超前进位电路超前进位电路 S3 S2 S1 S0C3A3B3A2B

14、2A1B1A0B0C0-1CICICICIC0C1C2集成芯片集成芯片CMOS:CC4008TTL:74283 74LS283应用举例应用举例8421 BCD 码码 余余 3 码码3.2.2 数值比较器数值比较器(Digital Comparator)一、一、1 位数值比较器位数值比较器0 00 11 01 10 1 00 0 11 0 00 1 0真真值值表表函数式函数式逻辑图逻辑图 用用与非门与非门和和非门非门实现实现Ai Bi Li Gi MiLi(A B)Gi(A=B)Mi(A BL=1A=BM=1A 1 0 0=1 0 0=1 0 0=1 0 0=0 1 0 0 0 1=0 0 1=

15、0 0 1=0 0 1B=B3B2B1B0LGM4 4位数值比较器位数值比较器A3 B3 A2 B2 A1 B1 A0 B0&1&1&1&1&1&1&1 1&1&1&1 1 MLGA2A1B3A3B2B1B01 A0G=(A3 B3)(A2 B2)(A1 B1)(A0 B0)4 位数值比较器位数值比较器M=A3B3+(A3 B3)A2B2 +(A3 B3)(A2 B2)A1 B1+(A3 B3)(A2 B2)(A1 B1)A0B0L=M+G1 位数值比较器位数值比较器AiMiBiAi BiAiBiLiGiAiBi&1&1&比比 较较 输输 入入级级 联联 输输 入入输输 出出A3B3A2B2A

16、1B1A0B0ABFA B 001=001=001=001=001001=010010=100100 100=100 4 位集成数值比较器的真值表位集成数值比较器的真值表级联输入:级联输入:供扩展使用,一般接低位芯片的比较输出,即供扩展使用,一般接低位芯片的比较输出,即 接低位芯片的接低位芯片的 FA B。扩展:扩展:级级联联输输入入 集成数值比较器集成数值比较器 74LS85(TTL)两片两片 4 位位数值比较器数值比较器74LS85 AB74LS85 ABVCC A3 B2 A2 A1 B1 A0 B0B3 AB FAB FA=B FAB地地1 2 3 4 5 6 7 816 15 14

17、13 12 11 10 97485 74LS851 8 位位数值比较器数值比较器低位比较结果低位比较结果高位比较结果高位比较结果 FAB FAB B7 A7 B6 A6 B5 A5 B4 A4 B3 A3 B2 A2 B1 A1 B0 A0 比较输出比较输出CMOS 芯片设置芯片设置 A B 只是为了电路对称,不起判断作用只是为了电路对称,不起判断作用B7 A7 B6 A6 B5 A5 B4 A4 FAB CC14585 ABB3 A3 B2 A2 B1 A1 B0 A0 FAB CC14585 AB 集成数值比较器集成数值比较器 CC15485(CMOS)扩展:扩展:两片两片4 位位 8 位

18、位VDDA3 B3 FAB FABA BA=BA1VSS1 2 3 4 5 6 7 816 15 14 13 12 11 10 9CC14585 C6631低位比较结果低位比较结果高位比较结果高位比较结果13.3 编码器和译码器编码器和译码器3.3.1 编码器编码器(Encoder)编码:编码:用文字、符号或者数字表示特定对象的过程用文字、符号或者数字表示特定对象的过程(用二进制代码表示不同事物)(用二进制代码表示不同事物)二进制编码器二进制编码器二二十进制编码器十进制编码器分类:分类:普通编码器普通编码器优先编码器优先编码器2nn104或或Y1I1编编 码码 器器Y2YmI2In代代码码输输

19、出出信信息息输输入入编编 码码 器器 框框 图图一、二进制普通编码器一、二进制普通编码器用用 n 位二进制代码对位二进制代码对 N=2n 个信号进行编码的电路个信号进行编码的电路1.3 位二进制编码器位二进制编码器(8 线线-3 线线)编码表编码表函函数数式式Y2=I4+I5+I6+I7Y1=I2+I3+I6+I7Y0=I1+I3+I5+I7输输入入输输出出 I0 I7 是一组互相排斥的输入变是一组互相排斥的输入变量,任何时刻只能有一个端输入有效量,任何时刻只能有一个端输入有效信号。信号。输输 入入输输 出出0 0 00 0 10 1 00 1 11 0 01 0 11 1 01 1 1Y2

20、Y1 Y0I0I1I2I3I4I5I6I73 位位二进制二进制编码器编码器I0I1I6I7Y2Y1Y0I2I4I5I3函数式函数式逻辑图逻辑图 用用或门或门实现实现 用用与非门与非门实现实现Y2 Y1 Y0111I7 I6 I5 I4 I3I2 I1I0&Y2 Y1 Y0优先编码:优先编码:允许几个信号同时输入,但只对优先级别最高允许几个信号同时输入,但只对优先级别最高的进行编码。的进行编码。优先顺序:优先顺序:I7 I0编码表编码表输输 入入输输 出出 I7 I6 I5 I4 I3 I2 I1 I0 Y2 Y1 Y0 1 1 1 1 0 1 1 1 0 0 0 1 1 0 1 0 0 0 1

21、 1 0 0 0 0 0 0 1 0 1 1 0 0 0 0 0 1 0 1 0 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 0 1 0 0 0函数式函数式2.3 位二进制优先编码器位二进制优先编码器输入输入输出输出为原为原变量变量逻逻辑辑图图输入输入输出输出为反为反变量变量Y2Y1Y0111&111111111111111I7I6I5I4I3I2I1I03.3.集成的优先编码器集成的优先编码器TTL:74LS148TTL:74LS148CMOS:74HC148CMOS:74HC148和和7474HC147HC147线线优先编码器线线优先编码器7474LS148LS148

22、简化真值表简化真值表(逻辑变量上的非号表示低电平有效)(逻辑变量上的非号表示低电平有效)7474LS148LS148的逻辑功能描述:的逻辑功能描述:(1)(1)编码输入端:逻辑符号输入端编码输入端:逻辑符号输入端 上面均有上面均有“”“”号,这表示编码号,这表示编码输入低电平有效。输入低电平有效。I I0 0II7 7低电平低电平有效有效优先权优先权最高最高允许编允许编码,但码,但无有效无有效编码请编码请求求(2)(2)编码输出端编码输出端 :从功能表可以:从功能表可以看出,看出,7474LS148LS148编码器的编码编码器的编码输出是反码输出是反码。Y Y2 2、Y Y1 1、Y Y0 0

23、 (3 3)选通输入端:只有在选通输入端:只有在 =0 =0时,编码器才时,编码器才处于处于工作状态工作状态;而在;而在 =1 =1时,编码器处于时,编码器处于禁止状态禁止状态,所有输出端均被封锁为高电平。所有输出端均被封锁为高电平。STST禁止禁止状态状态工作工作状态状态STST 允许编码,允许编码,但无有效但无有效编码请求编码请求正在优正在优先编码先编码(4 4)扩展输出端)扩展输出端Y YEXEX和选通输出端和选通输出端Y YS S:为扩展编码器功为扩展编码器功能而设置。能而设置。用74LS148接成的16线4线优先编码器 优先权最高(2)片无有效编码请求时才允许(1)片编码编码输出的最

24、高位编码输出为原码设计一电路:设计一电路:某机关有某机关有8 8个老板和一个秘书,每个老板房间有一个按扭,个老板和一个秘书,每个老板房间有一个按扭,在秘书房间中有一优先编码器电路,该电路可以用数码管显示老板的编在秘书房间中有一优先编码器电路,该电路可以用数码管显示老板的编码。老板的位权是不同的,秘书依照老板的位权,优先对位权高的老板码。老板的位权是不同的,秘书依照老板的位权,优先对位权高的老板进行服务。并且设计一蜂鸣器发声,以提醒有老板按下了按扭。进行服务。并且设计一蜂鸣器发声,以提醒有老板按下了按扭。解:使用解:使用8-38-3线优先编码器。假设老板位权最高为线优先编码器。假设老板位权最高为

25、8 8,次之为,次之为7 7,依次,依次类推,位权最低的老板为类推,位权最低的老板为1 1。用用 4 位二进制代码对位二进制代码对 0 9 十个信号进行编码的电路十个信号进行编码的电路1.8421 BCD 编码器编码器2.8421 BCD 优先编码器优先编码器3.集成集成 10线线-4线线优先编码器优先编码器(74147 74LS147)三、几种常用编码三、几种常用编码1.二二-十进制编码十进制编码8421 码码 余余 3 码码 2421 码码5211 码码 余余 3 循环码循环码 右移循环码右移循环码循环码(反射码或格雷码)循环码(反射码或格雷码)ISO码码ANSCII(ASCII)码码二、

26、二二、二-十进制编码器十进制编码器2.其他其他二二-十进制十进制编码器编码器I0I2I4I6I8I1I3I5I7I9Y0Y1Y2Y374147的流行符号和的流行符号和IEEE符号符号真值表:真值表:输入为输入为1-91-9九个数字,输出是九个数字,输出是BCDBCD码,数字码,数字0 0不是输入信号。不是输入信号。输入与输出都是低电平有效。输入与输出都是低电平有效。设计一电路可以将设计一电路可以将0-9十个按扭信号转换成编码。当没有按扭按下十个按扭信号转换成编码。当没有按扭按下时,按扭按下信号时,按扭按下信号Y=0。若有按扭按下,则按扭按下信号若有按扭按下,则按扭按下信号Y=1。3.3.2 译

27、码器译码器(Decoder)编码的逆过程,将二进制代码翻译为原来的含义编码的逆过程,将二进制代码翻译为原来的含义一、二进制译码器一、二进制译码器(Binary Decoder)输入输入 n 位二位二进制代码进制代码如:如:2 线线 4 线译码器线译码器 3 线线 8 线译码器线译码器4 线线 16 线译码器线译码器A0Y0A1An-1Y1Ym-1二进制二进制译码器译码器输出输出 m 个个信号信号 m=2n1.3位二进制译码器位二进制译码器(3 线线 8 线线)真值表真值表函数式函数式A0Y0A1A2Y1Y73 位位二进制二进制译码器译码器0 0 0 0 0 0 0 1 0 0 0 0 0 0

28、1 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 00 0 10 1 00 1 11 0 01 0 11 1 01 1 13 线线-8 线译码器逻辑图线译码器逻辑图000 输出低电平有效输出低电平有效工作原理:工作原理:11111101&Y7&Y6&Y5&Y4&Y3&Y2&Y1&Y0A2A2A1A1A0A0111111A2A1A00011111011101010111111011111011111001111101110111111110

29、11011011111111011111112.集成集成 3 线线 8 线译码器线译码器-74LS138引脚排列图引脚排列图功能示意图功能示意图输入选通控制端输入选通控制端芯片芯片禁止禁止工作工作芯片芯片正常正常工作工作VCC 地地1324567816 15 14 13 12 11 10974LS138Y0 Y1 Y2 Y3 Y4 Y5 Y6 A0 A1 A2 S3 S2 S1 Y7 74LS138Y0 Y1 Y2 Y3 Y4 Y5 Y6 A0 A1 A2 S3 S2 S1 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 A0 A1 A2 STB STC STA Y7 7474LS138LS1

30、38的功能表的功能表译中为0高电平有效低电平有效禁止禁止译码译码译译码码工工作作3.二进制译码器的级联二进制译码器的级联 两片两片3 线线 8 线线4 线线-16 线线Y0Y7Y8Y1574LS138Y0 Y1 Y2 Y3 Y4 Y5 Y6 A0 A1 A2 STB STC STA 高位高位Y7 A0 A1 A2 A3 74LS138Y0 Y1 Y2 Y3 Y4 Y5 Y6 A0 A1 A2 STB STC STA 低位低位Y7 10工作工作禁止禁止有输出有输出无输出无输出 1禁止禁止工作工作无输出无输出有输出有输出0 78 15三片三片 3 线线-8 线线5 线线-24 线线(1)()(2)

31、()(3)输输 出出工工 禁禁 禁禁禁禁 工工 禁禁禁禁 禁禁 工工0 00 11 01 1禁禁 禁禁 禁禁全为全为 174LS138(1)Y0 Y1 Y2 Y3 Y4 Y5 Y6 A0 A1 A2 STB STC STA Y0Y7 Y774LS138(3)Y0 Y1 Y2 Y3 Y4 Y5 Y6 A0 A1 A2 STB STC STA Y16Y7 Y2374LS138(2)Y0 Y1 Y2 Y3 Y4 Y5 Y6 A0 A1 A2 STB STC STA Y8Y7 Y15A0A1A2A3A41功能特点:功能特点:输出端提供全部最小项输出端提供全部最小项电路特点:电路特点:与门与门(原变量输

32、出原变量输出)Y Yi i=M=Mi i与非门与非门(反变量输出反变量输出)Y Yi i=M=Mi i4.二进制译码器的主要特点二进制译码器的主要特点二、二二、二-十进制译码器十进制译码器(Binary-Coded Decimal Decoder)将将 BCD 码翻译成对应的码翻译成对应的十个十个输出信号输出信号集成集成 4 线线 10 线线译码器:译码器:7442 74LS42二二-十进制译码器十进制译码器7474LS42LS42的功能表的功能表译中为0拒绝伪码在数字测量仪表和各种数字系统中,都需要将数字量在数字测量仪表和各种数字系统中,都需要将数字量直观地显示出来,一方面供人们直接读取测量

33、和运算的结直观地显示出来,一方面供人们直接读取测量和运算的结果,另一方面用于监视数字系统的工作情况。果,另一方面用于监视数字系统的工作情况。数字显示电路是数字设备不可缺少的部分。数字显示数字显示电路是数字设备不可缺少的部分。数字显示电路通常由电路通常由译码器、驱动器译码器、驱动器和和显示器等显示器等部分组成,如图所部分组成,如图所示。示。数字显示电路的组成方框图 三、显示译码器三、显示译码器1.数码显示器数码显示器 LED LCDLED:半导体材料构成,供电电压仅几伏,可以和半导体材料构成,供电电压仅几伏,可以和TTL集成电路匹配,集成电路匹配,单个发光二极管的电流从几毫安到十几个毫安。单个发

34、光二极管的电流从几毫安到十几个毫安。LCD:液晶(有机化合物)构成,在电场作用下会产生各种光电效应。它的显液晶(有机化合物)构成,在电场作用下会产生各种光电效应。它的显示控制电路比较复杂,不过现在有专用的集成电路与液晶显示器件配套示控制电路比较复杂,不过现在有专用的集成电路与液晶显示器件配套。(a)笔划段型(b)点阵型半导体显示半导体显示(LED)每字段是一只每字段是一只发光二极管发光二极管七段显示七段显示LEDLED数码管数码管(a)a)外形图外形图 (b)b)共阴型共阴型 (c)c)共阳型共阳型公共阴极公共阴极公共阳极公共阳极高电平驱动高电平驱动低电平驱动低电平驱动aebcfgd七段字形显

35、示方式七段字形显示方式LEDLED数码管通常采用图所示的七段字形显示方式数码管通常采用图所示的七段字形显示方式来表示来表示0-90-9十个数字。十个数字。7474LS49LS49的逻辑符号的逻辑符号2.2.七段显示译码器七段显示译码器灭灯灭灯控制端控制端84218421B BCDCD码码七段七段代码代码七段显示器译码器把输入的七段显示器译码器把输入的BCDBCD码,翻译成驱动七码,翻译成驱动七段段LEDLED数码管各对应段所需的电平。数码管各对应段所需的电平。7474LS49LS49是一种七段显示译码器。是一种七段显示译码器。表表74LS49的功能表的功能表8421BCD码禁止码灭灯状态共阴极

36、共阴极abcdefgR+5 VYaA3A2A1A0+VCC显示显示译码器译码器共阴共阴YbYcYdYeYfYg 高电平高电平驱动驱动00001111110000100100110000110110100110100010101100111100010011111001011001110110111011111111000011111111111011aebcfgd共阳极共阳极abcdefgR+5 VYaA3A2A1A0+VCC+VCC显示显示译码器译码器共阳共阳YbYcYdYeYfYg0000000000100010010100111100100100011010001010110000011

37、0100110001001000100000 低电平低电平驱动驱动011100011111000000000010010000100数数据据传传输输方方式式0110发送发送0110并行传送并行传送0110串行传送串行传送并并-串转换:串转换:数据选择器数据选择器串串-并转换:并转换:数据分配器数据分配器3.4 数据选择器和分配器数据选择器和分配器接收接收0110 在发送端和接收端不需要在发送端和接收端不需要数据数据 并并-串串 或或 串串-并并 转换装置,转换装置,但每位数据各占一条传输线,当但每位数据各占一条传输线,当传送数据位数增多时,成本较高,传送数据位数增多时,成本较高,且很难实现。且

38、很难实现。3.4.1 数据选择器数据选择器 (Data Selector)能够从能够从多路多路数据输入中数据输入中选择一路选择一路作为输出的电路作为输出的电路一、一、4 选选 1 数据选择器数据选择器输输入入数数据据输输出出数数据据选择控制信号选择控制信号A0Y4选选1数据选择器数据选择器D0D3D1D2A11.工作原理工作原理0 0 0 1 1 0 1 1 D0D1D2D3D0 0 0D0D A1 A0 2.真值表真值表D1 0 1D2 1 0D3 1 1Y D1D2D33.函数式函数式 一、一、4 选选 1 数据选择器数据选择器3.函数式函数式4.逻辑图逻辑图1&11YA11A0D0D1D

39、2D30 0 0 1 1 0 1 1 =D0=D1=D2=D3 二、集成数据选择器二、集成数据选择器1.8 选选 1 数据选择器数据选择器74151 74LS151 74251 74LS251引引脚脚排排列列图图功功能能示示意意图图VCC 地地1324567816 15 14 13 12 11 10 974LS151D4 D5 D6 D7 A0 A1 A2 D3 D2 D1 D0 Y Y SMUXD7A2D0A0A1SYY禁止禁止使能使能1 0 0 0 0D0 D0 D1 D1 D2 D2 D3 D3 D4 D4 D5 D5 D6 D6 D7 D7 0 0 10 1 00 1 11 0 01

40、0 11 1 01 1 11 0 A2 A0 地址端地址端D7 D0 数据输入端数据输入端2.集成数据选择器的扩展集成数据选择器的扩展两片两片 8 选选 1(74151)16 选选 1数据选择器数据选择器A2 A1 A0 A3 D15 D81Y1S74151(2)D7A2D0ENA0A1YY2D7 D074151(1)D7A2D0ENA0A1SYY1低位低位高位高位0 禁止禁止使能使能0 70 D0 D7 D0 D7 1 使能使能禁止禁止D8 D15 0 D8 D15 方法方法 2:74LS153 双双 4 选选 1 数据选择器数据选择器(1)(2)(3)(4)输出信号输出信号0 0工工 禁禁

41、 禁禁 禁禁0 1禁禁 工工 禁禁 禁禁1 0禁禁 禁禁 工工 禁禁1 1禁禁 禁禁 禁禁 工工方法方法 1:四片四片 8 选选 1(74151)32 选选 1 数据选择器数据选择器四路四路 8 位位并行数据并行数据四片四片8选选1四路四路 1 位位串行数据串行数据一片一片4选选1一路一路 1 位位串行数据串行数据(电路略)(电路略)真值表真值表(使用(使用 74LS139 双双 2 线线-4 线译码器)线译码器)0 四片四片 8 选选 1(74151)32 选选 1 数据选择器数据选择器1/2 74LS139SA4A3A2A1A0&Y方法方法 1:74LS139 双双 2 线线-4 线译码器

42、线译码器74151(4)D7A2D0ENA0A1S4Y374151(1)D7A2D0ENA0A1D0S1Y074151(2)D7A2D0ENA0A1S2Y174151(3)D7A2D0ENA0A1S3Y2D7D8D15D16D23D24D311 1 1 1 1 0 7禁止禁止 禁止禁止 禁止禁止 禁止禁止 0 0 01 1 1 0 禁止禁止 禁止禁止 禁止禁止 使能使能 0 1禁止禁止 禁止禁止 使能使能 禁止禁止 禁止禁止 使能使能 禁止禁止 禁止禁止 使能使能 禁止禁止 禁止禁止 禁止禁止 1 01 1D0 D7 D8 D15 D16 D23 D24 D311 1 0 1 1 0 1 1

43、0 1 1 1 3.4.2 数据分配器数据分配器(Data Demultiplexer)将将 1 路路输入数据,根据需要分别传送到输入数据,根据需要分别传送到 m 个个输出端输出端一、一、1 路路-4 路数据分配器路数据分配器数据数据输入输入数据输出数据输出选择控制选择控制0 00 11 01 1D 0 0 00 D 0 00 0 D 00 0 0 D&Y0&Y1&Y2&Y31A11A1DDA01 路路-4 路路数据分配器数据分配器Y0Y3Y1Y2A1真真值值表表函函数数式式逻辑图逻辑图二、集成数据分配器二、集成数据分配器用用 3 线线-8 线译码器线译码器可实现可实现 1 路路-8 路路数据

44、分配器数据分配器数据输出数据输出 S1 数据输入(数据输入(D)地址码地址码 数据输入数据输入(任选一路任选一路)S3 数据输入(数据输入(D)74LS138Y0 Y1 Y2 Y3 Y4 Y5 Y6 A0 A1 A2 S3 S2 S1 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 A0 A1 A2 STB STC STA Y7 3.5 用用 MSI 实现组合逻辑函数实现组合逻辑函数3.5.1 用数据选择器实现组合逻辑函数用数据选择器实现组合逻辑函数一、基本原理和步骤一、基本原理和步骤1.原理:原理:选择器输出为标准与或式,含地址变量的选择器输出为标准与或式,含地址变量的全部最小项。例如全部最

45、小项。例如 而任何组合逻辑函数都可以表示成为最小项之和而任何组合逻辑函数都可以表示成为最小项之和的形式,故可用数据选择器实现。的形式,故可用数据选择器实现。4 选选 18 选选 12.步骤步骤(1)根据根据 n=k-1 或或n=k 确定数据选择器的规模和型号确定数据选择器的规模和型号(n 选择器选择器地址码地址码,k 函数的函数的变量个数变量个数)(2)写出函数的写出函数的标准与或式标准与或式和选择器和选择器输出信号表达式输出信号表达式(3)对照比较确定选择器各个输入变量的表达式对照比较确定选择器各个输入变量的表达式 (4)根据采用的根据采用的数据选择器数据选择器和和求出的表达式求出的表达式画

46、出连线图画出连线图二、应用举例二、应用举例 例例 3.5.1 用数据选择器实现函数用数据选择器实现函数 解解(2)标准与或式标准与或式(1)n=k-1=3-1=2 可用可用 4 选选 1 数据选择器数据选择器 74LS153数据选择器数据选择器(3)确定输入变量和地址码的对应关系确定输入变量和地址码的对应关系令令 A1=A,A0=B则则 D0=0 D1=D2=C D3=1方法一:公式法方法一:公式法FA BY1/2 74LS153D3D2D1D0A1A0ST1C(4)画连线图画连线图(4)画连线图画连线图(与方法一相同与方法一相同)方法二:图形法方法二:图形法按按 A、B 顺序写出函数的标准与

47、或式顺序写出函数的标准与或式含变量含变量 C 的的 F 的卡诺图的卡诺图含变量含变量 Di 的的 Y 的卡诺图的卡诺图AB0101A1A001010CC1D0D1D2D3令令 A1=A,A0=B则则 D0=0 D1=D2=C D3=1例例 3.5.3 用数据选择器实现函数用数据选择器实现函数 解解(2)函数函数 Z 的标准与或式的标准与或式8 选选 1(3)确定输入变量和地址码的对应关系确定输入变量和地址码的对应关系(1)n=k-1=4-1=3若令若令A2=A,A1=B,A0=C(4)画连线图画连线图则则D2=D3=D4=1D0=0用用 8 选选 1 数据选择器数据选择器 74LS151ZA

48、B C1DD1D1=DY 74LS151D7D6D5D4D3D2D1D0A2A1A0S方法一:公式法方法一:公式法则则方法二:图形法方法二:图形法ABCD0001111000 01 11 100011111001111100令令 A2=A A1=B A0=C3.5.2 用二进制译码器实现组合逻辑函数用二进制译码器实现组合逻辑函数一、基本原理与步骤一、基本原理与步骤1.基本原理:基本原理:二进制译码器又叫变量译码器或最小项二进制译码器又叫变量译码器或最小项译码器译码器,它的它的输出端提供了其输入变量的输出端提供了其输入变量的全部最小项全部最小项。任何一个函数都可以任何一个函数都可以写成最小项之和

49、的形式写成最小项之和的形式74LS138Y0 Y1 Y2 Y3 Y4 Y5 Y6 A0 A1 A2 S3 S2 S1 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 A0 A1 A2 STB STC STA Y7 2.基本步骤基本步骤(1)选择集成二进制译码器选择集成二进制译码器(2)写函数的标准与非写函数的标准与非-与非式与非式(3)确认变量和输入关系确认变量和输入关系例例 3.5.5用集成译码器实现函数用集成译码器实现函数(1)三个输入变量,三个输入变量,选选 3 线线 8 线译码器线译码器 74LS138(2)函数的标准与非函数的标准与非-与非式与非式(4)画连线图画连线图 解解(4)画

50、连线图画连线图(3)确认变量和输入关系确认变量和输入关系令令则则74LS138Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 A0 A1 A2 STB STC STA&Z3ABC1在输出端需增加一个与非门在输出端需增加一个与非门3.6 只读存储器只读存储器(ROM)分类分类掩模掩模 ROM可编程可编程 ROM(PROM Programmable ROM)可擦除可编程可擦除可编程 ROM(EPROM Erasable PROM)说明说明:掩模掩模 ROMPROM生产过程中在掩模板控制下写入,内容固定,生产过程中在掩模板控制下写入,内容固定,不能更改不能更改内容可由用户编好后写入,一经写入不能更改

51、内容可由用户编好后写入,一经写入不能更改紫外光擦除(约二十分钟)紫外光擦除(约二十分钟)EPROM存储数据可以更改,但改写麻烦,工作时只读存储数据可以更改,但改写麻烦,工作时只读EEPROM 或或 E2PROM电擦除(几十毫秒)电擦除(几十毫秒)3.6.1 ROM 的结构和工作原理的结构和工作原理1.基本结构基本结构一、一、ROM 的结构示意图的结构示意图地址输入地址输入数据输出数据输出 n 位地址位地址 b b 位数据位数据A0A1An-1D0D1Db-1D0D1Db-1A0A1An-12nb ROM最最高高位位最最低低位位2.内部结构示意图内部结构示意图存储单元存储单元数据输出数据输出字字

52、线线位线位线地址译码器地址译码器ROM 存储容量存储容量=字线数字线数 位线数位线数=2n b(位)位)地地址址输输入入0单元单元1单元单元i 单元单元2n-1单元单元D0D1Db-1A0A1An-1W0W1WiW2n-13.逻辑结构示意图逻辑结构示意图(1)中大规模集成电路中门电路的简化画法中大规模集成电路中门电路的简化画法连上且为硬连接,不能通过编程改变连上且为硬连接,不能通过编程改变编程连接,可以通过编程将其断开编程连接,可以通过编程将其断开断开断开A BDCABDY&ABCY1与门与门或门或门 AY=AY=AAZ=AY=AAYA1A1YA1YZ缓冲器缓冲器同相输出同相输出反相输出反相输

53、出互补输出互补输出(2)逻辑结构示意图逻辑结构示意图m0A0A1An-1m1mim2n-1译译码码器器Z0(D0)或门或门Z1(D1)或门或门Zb-1(Db-1)或门或门2n个与门构成个与门构成 n 位位二进制译码器二进制译码器,输输出出2n 个最小项。个最小项。.n个个输输入入变变量量b 个输出函数个输出函数或门阵列或门阵列与门阵列与门阵列W0(m0)W2(m2)D 0=W0+W2=m0+m2二、二、ROM 的基本工作原理的基本工作原理1.电路组成电路组成二极管或门二极管或门二极管与门二极管与门W0(m0)+VCC1A111A01VccEND3END2END1END0D3 D2 D1 D0

54、W0(m0)W1(m1)W2(m2)W3(m3)与与门门阵阵列列(译码器译码器)或或门门阵阵列列(编码器编码器)位位线线字线字线输出输出缓冲缓冲2.工作原理工作原理输出信号的逻辑表达式输出信号的逻辑表达式1A111A01VccEND3END2END1END0D3 D2 D1 D0 W0(m0)W1(m1)W2(m2)W3(m3)与与门门阵阵列列(译码器译码器)或或门门阵阵列列(编码器编码器)位位线线输出输出缓冲缓冲字线字线字线:字线:位线:位线:输出信号的真值表输出信号的真值表0 00 11 01 10 1 0 1A1 A0D3 D2 D1 D01 0 1 00 1 1 11 1 1 03.功

55、能说明功能说明(1)存储器存储器(2)函数发生器函数发生器地址地址存储存储数据数据输入变量输入变量输出函数输出函数(3)译码编码译码编码字线字线编码编码0 1 0 11 0 1 00 1 1 11 1 1 0A1 A00 00 11 01 1输入输入变量变量输出输出函数函数3.6.2 ROM 应用举例及容量扩展应用举例及容量扩展一、一、ROM 应用举例应用举例用用 ROM 实现实现以下逻辑函数以下逻辑函数例例 3.6.2Y1=m(2,3,4,5,8,9,14,15)Y2=m(6,7,10,11,14,15)Y3=m(0,3,6,9,12,15)Y4=m(7,11,13,14,15)A1B1C1

56、D1m0m1m2m3m4m5m6m7m8m9m10m11m12m13m14m15Y2Y3Y4Y1译译码码器器编编码码器器二、二、ROM 容量扩展容量扩展1.存储容量存储容量存储器存储数据的能力,为存储器含存储单元存储器存储数据的能力,为存储器含存储单元的总位数。的总位数。存储容量存储容量=字数字数 位数位数字字 word位位 bit1k 1:1024 个字个字 每个字每个字 1 位位 存储容量存储容量 1 k1k 4:1024 个字个字 每个字每个字 4 位位 存储容量存储容量 4 k256 8:256 个字个字 每个字每个字 8 位位 存储容量存储容量 2 k64 k 16:64 k 个字个

57、字 每个字每个字 16 位位 存储容量存储容量 1024k(1M)2.存储容量与地址位数的关系存储容量与地址位数的关系存储容量存储容量 256 48 位地址位地址256=284 位数据输出位数据输出存储容量存储容量 8k 88k=8 210=21313 位地址位地址8 位数据输出位数据输出3.常用常用 EPROM2764:27128:A0 A128k 8 (64k)13 位地址输入:位地址输入:8 位数据输出:位数据输出:O0 O7输出使能端输出使能端1 输出呈高阻输出呈高阻0 使能使能片选端片选端ROM 工作工作(任意)任意)ROM 不工作输出呈高阻不工作输出呈高阻16k 8 (128k)1

58、6k=16 210=21427256:32k 8 (256k)32k=32 210=2152764VPPPGMA0A1A2A3A4A5A6A7A8A9A10A11A12CSOEO0O1O2O3O4O5O6O7VCCVIH(PGM)CSOE地地址址输输出出01其他常用的其他常用的 EPROM 4.ROM 容量的扩展容量的扩展地地址址总总线线8位数据总线位数据总线16位位数数据据总总线线D(70)D(158)8 位位 16 位位地址线合并(共用)地址线合并(共用)输出使能端、片选端合并(共用)输出使能端、片选端合并(共用)数据输出端分为高数据输出端分为高 8 位和低位和低 8 位位方法方法(1)字

59、长的扩展(位扩展):字长的扩展(位扩展):27256A0A14O7O0CSOE27256A0A14O7O0CSOECSOE(2)字线的扩展(地址码的扩展字线的扩展(地址码的扩展 字扩展字扩展)两片两片 4 4 8 4:四片四片 32 k 8 4 32 k 8:15 位地址输入位地址输入增加两位地址增加两位地址经过经过 2 线线-4 线译码控制四个芯片的线译码控制四个芯片的ROM44位位A1 A0 D1 D0 D2 D3 ROM44位位A1 A0 D1 D2 D3 D0 1增加一位地址增加一位地址 A2(电路略)(电路略)3.7 组合电路中的竞争冒险组合电路中的竞争冒险3.7.1 竞争冒险的概念

60、及其产生原因竞争冒险的概念及其产生原因一、竞争冒险的概念一、竞争冒险的概念 在组合逻辑电路中,当输入信号改变状态时,输出端可能在组合逻辑电路中,当输入信号改变状态时,输出端可能出现虚假信号出现虚假信号 过渡干扰脉冲过渡干扰脉冲的现象,叫做竞争冒险。的现象,叫做竞争冒险。二、产生竞争冒险的原因二、产生竞争冒险的原因1.原因分析原因分析&ABY0110ABY 信号信号 A、B 不可能突变,需要经不可能突变,需要经历一段极短的过渡时间。而门电路历一段极短的过渡时间。而门电路的传输时间也各不相同,故当的传输时间也各不相同,故当A、B同时改变状态时可能在输出端产生同时改变状态时可能在输出端产生虚假信号。

61、虚假信号。2.电路举例电路举例&Y3&Y1&Y2&Y0A1B1 2 位二进制译码器位二进制译码器 假设信号假设信号 A 的变化规律如的变化规律如表中所示表中所示A B0 00 11 01 11 11 00 10 010000001产生干扰脉冲的时间:产生干扰脉冲的时间:3.7.2 消除竞争冒险的方法消除竞争冒险的方法一、引入封锁脉冲一、引入封锁脉冲&Y3&Y1&Y2&Y0A1B1ABP1存在的问题:存在的问题:对封锁脉冲的宽度和产生时间有严格的要求。对封锁脉冲的宽度和产生时间有严格的要求。P1&Y3&Y1&Y2&Y0A1B1AB二、引入选通脉冲二、引入选通脉冲P2P2存在的问题:存在的问题:对

62、选通脉冲的宽度和产生时间也有严格的要求。对选通脉冲的宽度和产生时间也有严格的要求。&Y3&Y1&Y2&Y0A1B1AB存在的问题:存在的问题:三、接入滤波电容三、接入滤波电容CfCf输出波形的边沿变坏。输出波形的边沿变坏。四、修改逻辑设计增加冗余项四、修改逻辑设计增加冗余项3.7.2 消除竞争冒险的方法消除竞争冒险的方法&ABCAG1G2G4G3Y&G5ABC010001 11 1011100100例如:例如:由于修改设计方案得当,收到了较好的效果。由于修改设计方案得当,收到了较好的效果。111例例 F=ACD+BC+BD将相切的部分均用多余的将相切的部分均用多余的卡诺圈包含起来,则可消卡诺圈包含起来,则可消除险象,得到:除险象,得到:F=ACD+BC+BD+ABD+ABC+CD11111 ABCD000111100001111011

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。