VHDL语言数据类型及相互转换

VHDL语言数据类型及相互转换

《VHDL语言数据类型及相互转换》由会员分享,可在线阅读,更多相关《VHDL语言数据类型及相互转换(7页珍藏版)》请在装配图网上搜索。

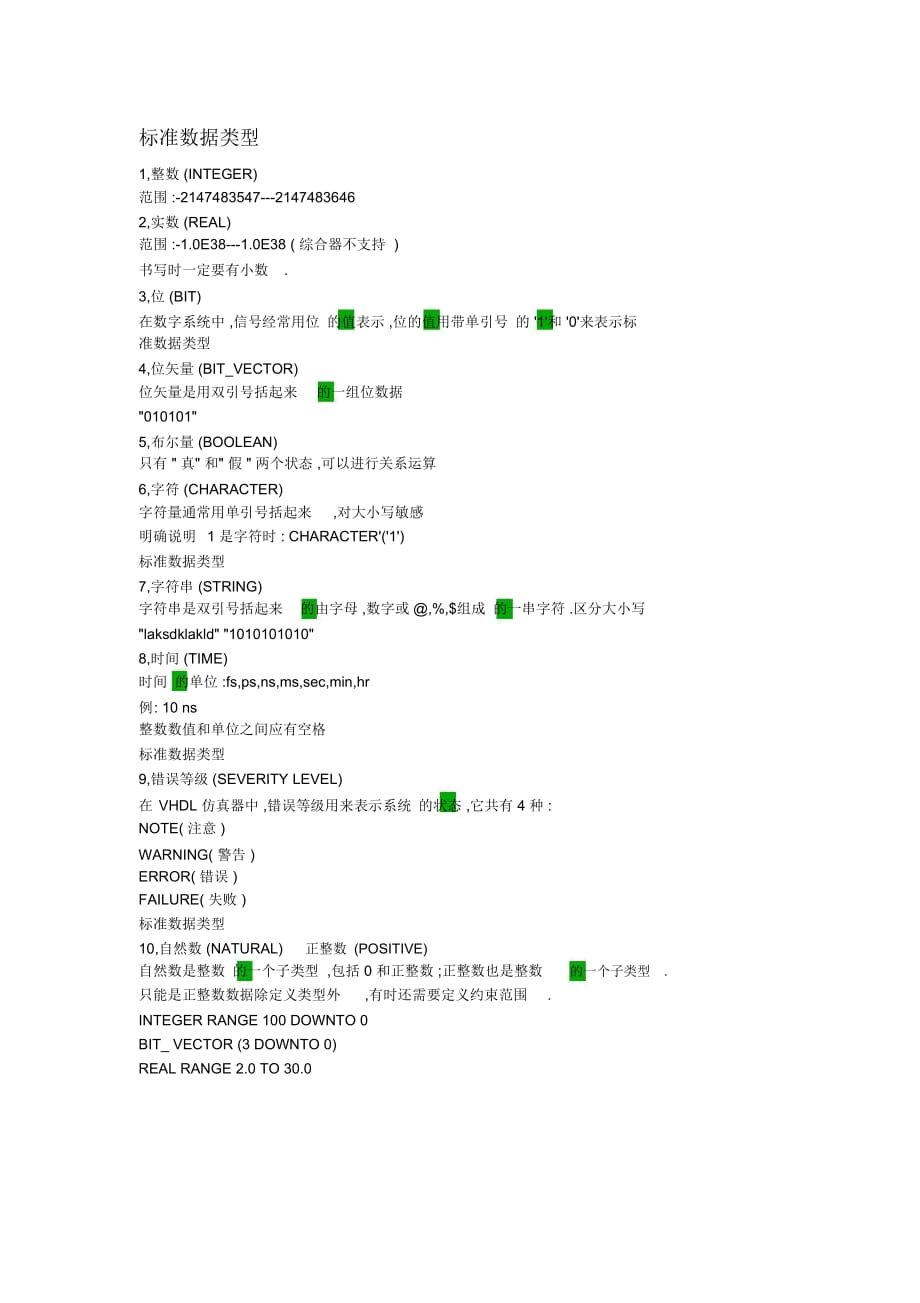

1、标准数据类型1,整数 (INTEGER)范围 :-2147483547-21474836462,实数 (REAL)范围 :-1.0E38-1.0E38 ( 综合器不支持 )书写时一定要有小数.3,位 (BIT)在数字系统中 ,信号经常用位 的值表示 ,位的值用带单引号 的 1和 0来表示标准数据类型4,位矢量 (BIT_VECTOR)位矢量是用双引号括起来的一组位数据0101015,布尔量 (BOOLEAN)只有 真 和 假 两个状态 ,可以进行关系运算6,字符 (CHARACTER)字符量通常用单引号括起来,对大小写敏感明确说明1 是字符时 : CHARACTER(1)标准数据类型7,字符串

2、 (STRING)字符串是双引号括起来的由字母 ,数字或 ,%,$组成 的一串字符 .区分大小写laksdklakld 10101010108,时间 (TIME)时间 的单位 :fs,ps,ns,ms,sec,min,hr例 : 10 ns整数数值和单位之间应有空格标准数据类型9,错误等级 (SEVERITY LEVEL)在 VHDL 仿真器中 ,错误等级用来表示系统 的状态 ,它共有 4 种 : NOTE( 注意 )WARNING( 警告 ) ERROR( 错误 )FAILURE( 失败 )标准数据类型10,自然数 (NATURAL)正整数 (POSITIVE)自然数是整数 的一个子类型 ,

3、包括 0 和正整数 ;正整数也是整数的一个子类型 .只能是正整数数据除定义类型外,有时还需要定义约束范围.INTEGER RANGE 100 DOWNTO 0BIT_ VECTOR (3 DOWNTO 0)REAL RANGE 2.0 TO 30.0IEEE 定义的逻辑位与矢量在 IEEE 的程序包 std_logic_1164 中定 了两个非常重要的数据 型 :1 ,std_logic取 :0,1,Z,X,W,L,HZ:高阻X: 不定W: 弱信号不定L:弱信号 0 H:弱信号 12,Std_logic_vector注 意1,在使用std_logic和 std_logic_vector时 ,

4、在程序中必 声明 及 程 序 包 说 明 句, 即LIBRARY ieee和 std_logic_1164.ALL 两句在程序中必不可少.2, std_logic 有多个取 ,与 BIT 不同 ,在 程 特 注意,需要考 全所有情况.用户自定义的数据类型1,枚 型格式 :TYPE数据 型名IS( 元素 ,元素 , );TYPE STD_LOGIC IS(U,X,0,1,Z,W,L,H,-);TYPE week IS (Sun,Mon,Tue,wed,Thu,Fri,Sat);TYPE color IS (red,green,yellow,blue)TYPE lift_state IS(stop

5、on1,doorpeen,doorclose,doorwait1,doorwait5,up,down,stop)doorwait2,doorwait3,doorwait4,枚 型 的声明TYPE color IS (red,green,yellow,blue);VARIABLE A:COLOR;SIGNAL B:COLOR;A:=RED;B=YELLOW;TYPE lever IS (0,1,z);SIGNAL V:lever;V=1;用 自定 的数据 型2,整数 (INTEGER)格式 :TYPE数据 型名IS 数据 型定 束范 例 TYPE digit IS INTEGER RANGE 0

6、 TO 9VARIABLE A:DIGIT;A:=5;A:=28;用 自定 的数据 型3, 数 (REAL)格式 :TYPE数据 型名IS 数据 型定 束范 TYPE current IS REAL RANGE -1E4 TO 1E4VARIABLE A:CURRENT;A:=1E3;A:=1E10;用户自定义 的数据类型4,数组 (ARRAY)格式 :TYPE数据类型名IS ARRAY范围OF 原数据类型名;例 :TYPE word IS ARRAY (1 TO 8) OF STD_LOGIC;TYPE word IS ARRAY (INTEGER 1 TO 8) OF STD_LOGIC;

7、数组常在总线 ,ROM 和 RAM 中使用 .用户自定义 的数据类型5,记录 (RECODE)类型将不同 的数据类型放在一块,就是记录类型数据格式 :TYPE记录类型名IS RECORD元素名 :数据类型名 ;元素名 :数据类型名 ;:END RECORD 记录类型名 ;记录 (RECODE)类型例 :TYPE bank IS RECORDaddr0: STD_LOGIC_VECTOR(7 DOWNTO 0);addr1: STD_LOGIC_VECTOR(7 DOWNTO 0);r0: INTEGER;END RECORD;记录 (RECODE)类型例 :CONSTANT LEN:integ

8、er:=100;TYPE array logic IS ARRAY (99 downto 0)OF STD_LOGIC_VECTOR(7 DOWNTO 0)TYPE table IS RECORDa: array logic;b: STD_LOGIC_VECTOR(7 DOWNTO 0);c: integer RANGE 0 to len ;END RECORD;数据类型的转换数据类型转换函数有VHDL例如 :STD_LOGIC_1164,语言 的包提供STD_LOGIC_ ARITHSTD_LOGIC_UNSIGNED等等函数说明1、 STD_LOGIC_1164包TO_STDLOGIC_V

9、ECTOR(A)TO_BITVECTOR(A)TO_LOGIC(A)TO_BIT(A)由 BIT_VECTOR 转换成 STD_LOGIC_VECTOR由 STD_LOGIC_VECTOR 转换成 BIT_VECTOR由 BIT 转换成 STD_LOGIC由 STD_LOGIC 转换成 BIT2、 STD_LOGIC_ARITH包CONV_STD_LOGIC_VECTOR(A,位长 )CONV_INTEGER(A)由 INTEGER,UNSIGNED 和 SIGNED 转换成STD_LOGIC_VECTOR由 UNSIGNED 和 SIGNED 转换成 INTEGER3、 STD_LOGIC_

10、UNSIGNED包CONV_INTEGER(A)_STD_LOGIC_VECTOR转换成 INTEGERVHDL 属性VHDL 没有一般程序 语言中 的那些运算类标准函数 ,取而代之 的是多种能反映和影响硬件行为的属性 .属性在描述时序电路 的 VHDL 设计文件中几乎处处可见 ,如检测上升沿 ,下降沿 ,知道前一次发生 的事件 .VHDL 属性属性指 的是关于实体 ,结构体 ,类型及信号 的一些特征 .有的属性对综合 (设计 ) 非常有用 . VHDL 的属性可分为数值类属性 ,函数类属性 ,范围类属性 ,信号类属性 ,类型类属性 .其引用 的一般形式为 :对象 属性 .数值类属性数值类属性

11、用于返回数组,块或一般数据的有关值 ,如边界 ,数组长度等信息.对一般 的数据有4 种 数 值 类 属 性 : 对 象 类 型 的 左 边 界 , 右 边 界 , 上 边 界 , 下 边 界 , 对 应 的 关 键 字是:LEFT,RIGHT,HIGH,LOW. 数组在加一个长度属性 LENGTH.数值类属性sdown:IN std_logic_vector(8 DOWNTO 0);sup:IN std_logic-vector(0 to 8);这两个信号 的各属性值如下 :sdownleft=8; sdownright=0; sdownlow=0; sdownhigh=8; sdownlen

12、gth=9;supleft=0; supright=8; suplow=0; suphigh=8; suplength=9;数值类属性TYPE bit32 IS ARRAY (63 DOWNTO 32)OF BITVARIABLE:left_range,right_range,up_range,low_range,len:INTEGER;BEGINleft-range:=bit32LEFT; -return 63right-range:=bit32RIGHT; -return 32up-range:=bit32HIGH; -return 63low-range:=bit32LOW; -retu

13、rn 32len:=bit32LENGTH; -return 32函数类属性信号属性函数属于函数类属性,用来返回有关信号行为功能的信息 .共有5 种信号属性函数 ,分别是 : EVENT( 事件 ) ; ACTIVE(活跃 ); LAST_EVENT (最近一次事件到现在经过多少时间);LAST_ACTIVE( 最近一次活跃到现在经过多少时间 ); LAST_V ALUE( 信号变化前 的取值是什么 )EVENTEVENT: 它的值为布尔型 ,取值为 TRUE 或 FALSE;如果刚好有事件发生在该属性所附着的信号上 (即信号有变化 ),取值为 TRUE.利用此属性可决定时钟边沿是否有效,即时

14、钟是否发生 .EVENTSIGNAL clk: IN std_logic;clk EVENT AND clk=1clk=1 AND clk EVENTclk EVENT AND clk=0clk=0 AND clk EVENTrising_edge(clk) falling_edge(clk)EVENT和 ACTIVEEVENT要求信号值发生变化;1 到 0,0 到 1ACTIVE信号值 的任何变化 ,1 到 1,1 到 0,0 到 1,0 到 0;所有 的事件都是活跃,但并非所有 的活跃都是事件范围类属性RANGE 属性 ,其生成一个限制性数据对象的范围 .例 SIGNAL data_bus

15、:std_logic_vector(15 DOWNTO 0); data_bus RANGE=15 downto 0用 VHDL 语言设计分频电路,把1KHZ 的时钟分至约1HZ 左右的时钟LIBRARY IEEE;USE IEEE.Std_Logic_1164.ALL;ENTITY FreDevider ISPORT(Clkin :IN Std_Logic;Clkout :OUT Std_Logic);END;ARCHITECTURE Devider OF FreDevider ISCONSTANT N:Integer:=499;signal counter :Integer range 0 to N;signal Clk :Std_Logic;BEGINPROCESS(Clkin )beginIF rising_edge(Clkin) THENIF Counter=N thencounter=0;Clk=not clk;elsecounter=counter+1;end if;end if;end process;clkout=clk;end;

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。