实验28线3线优先编码器

实验28线3线优先编码器

《实验28线3线优先编码器》由会员分享,可在线阅读,更多相关《实验28线3线优先编码器(2页珍藏版)》请在装配图网上搜索。

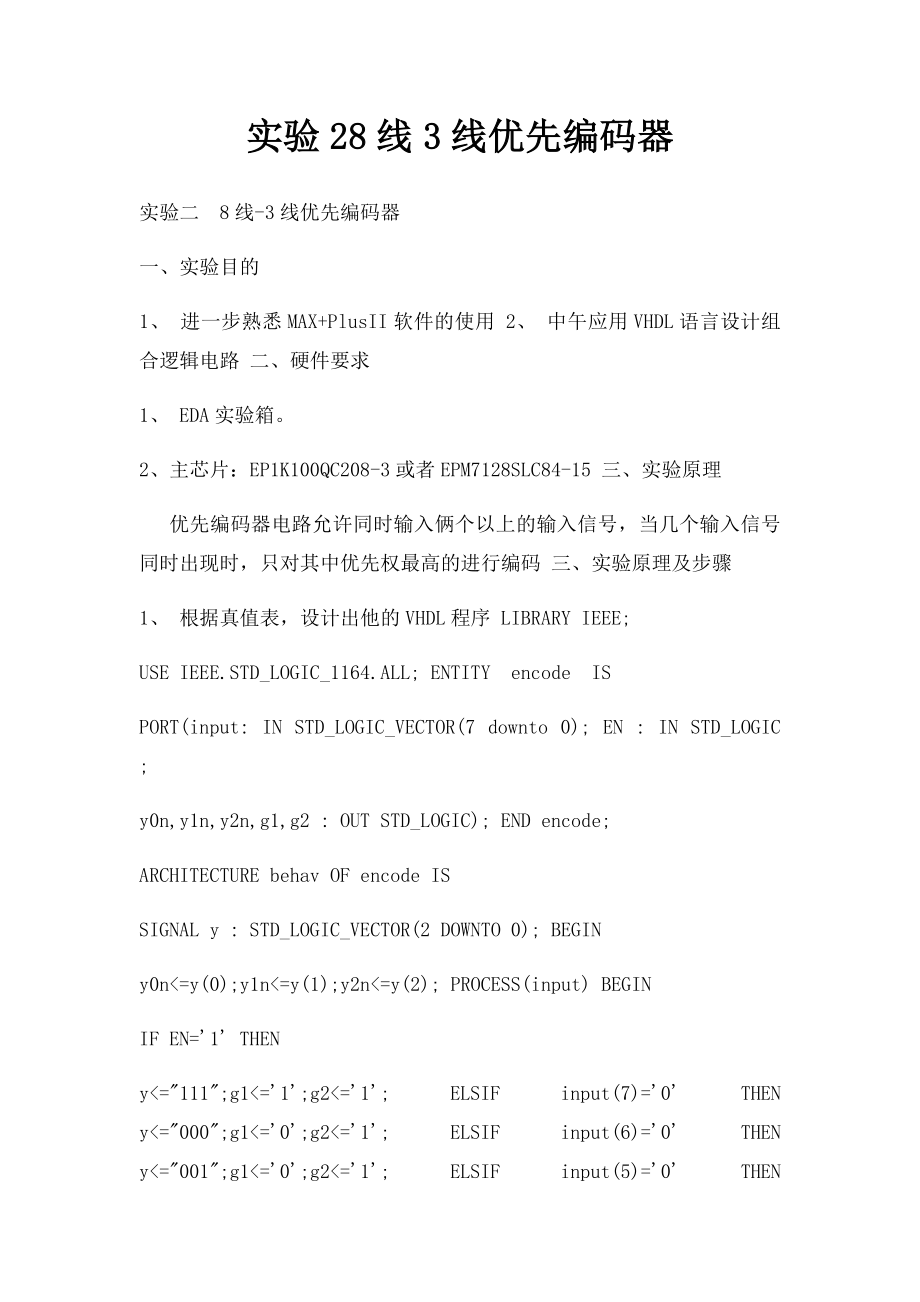

1、实验28线3线优先编码器实验二 8线-3线优先编码器 一、实验目的 1、 进一步熟悉MAX+PlusII软件的使用 2、 中午应用VHDL语言设计组合逻辑电路 二、硬件要求 1、 EDA实验箱。 2、主芯片:EP1K100QC208-3或者EPM7128SLC84-15 三、实验原理 优先编码器电路允许同时输入俩个以上的输入信号,当几个输入信号同时出现时,只对其中优先权最高的进行编码 三、实验原理及步骤 1、 根据真值表,设计出他的VHDL程序 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY encode IS PORT(input: IN

2、STD_LOGIC_VECTOR(7 downto 0); EN : IN STD_LOGIC ; y0n,y1n,y2n,g1,g2 : OUT STD_LOGIC); END encode; ARCHITECTURE behav OF encode IS SIGNAL y : STD_LOGIC_VECTOR(2 DOWNTO 0); BEGIN y0n=y(0);y1n=y(1);y2n=y(2); PROCESS(input) BEGIN IF EN=1 THEN y=111;g1=1;g2=1; ELSIF input(7)=0 THEN y=000;g1=0;g2=1; ELSIF

3、 input(6)=0 THEN y=001;g1=0;g2=1; ELSIF input(5)=0 THEN y=010;g1=0;g2=1; ELSIF input(4)=0 THEN y=011;g1=0;g2=1; ELSIF input(3)=0 THEN y=100;g1=0;g2=1; ELSIF input(2)=0 THEN y=101;g1=0;g2=1; ELSIF input(1)=0 THEN y=110;g1=0;g2=1; ELSIF input(0)=0 THEN y=111;g1=0;g2=1; ELSIF input=11111111 THEN y=111;g1=1;g2=0; END if; END PROCESS; END behav; 2、 对程序进行编译仿真,观察是否符合要求 3、选择恰当的芯片CPLD FPGA芯片,并锁定引脚。 4、蒋*。Pof文件下载到实验箱连线后观察实验现象。

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 《认识角》ppt教学讲解课件

- 《从数据谈节水》数据的收集、整理与描述优秀教学ppt课件

- 人员配置-公司组织架构与人员配置计划课件

- 《认识分式》ppt课件

- 《从百草园到三味书屋》第一课时ppt课件

- 公路工程概预算三课件

- 中考物理专题突破-综合能力题教学课件

- 《创新设计》高考英语二轮复习(江苏专用)ppt课件:第二部分-基础语法巧学巧练-专题八-非谓语动词

- 中考物理专题复习课件:滑轮及滑轮组

- CIM安全标识统一规划课件

- 中考物理专题复习教学课件-质量和密度

- 《处理民族关系的原则平等团结共同繁荣》ppt课件

- 中考物理专题复习之物理实验和探究题复习指导教学课件

- 《十二人人都会有挫折》初中心理健康教育闽教版《中学生心理健康》七级课件

- Cisco无线网络-安全-Brief课件