EDA复习要点 全

EDA复习要点 全

《EDA复习要点 全》由会员分享,可在线阅读,更多相关《EDA复习要点 全(11页珍藏版)》请在装配图网上搜索。

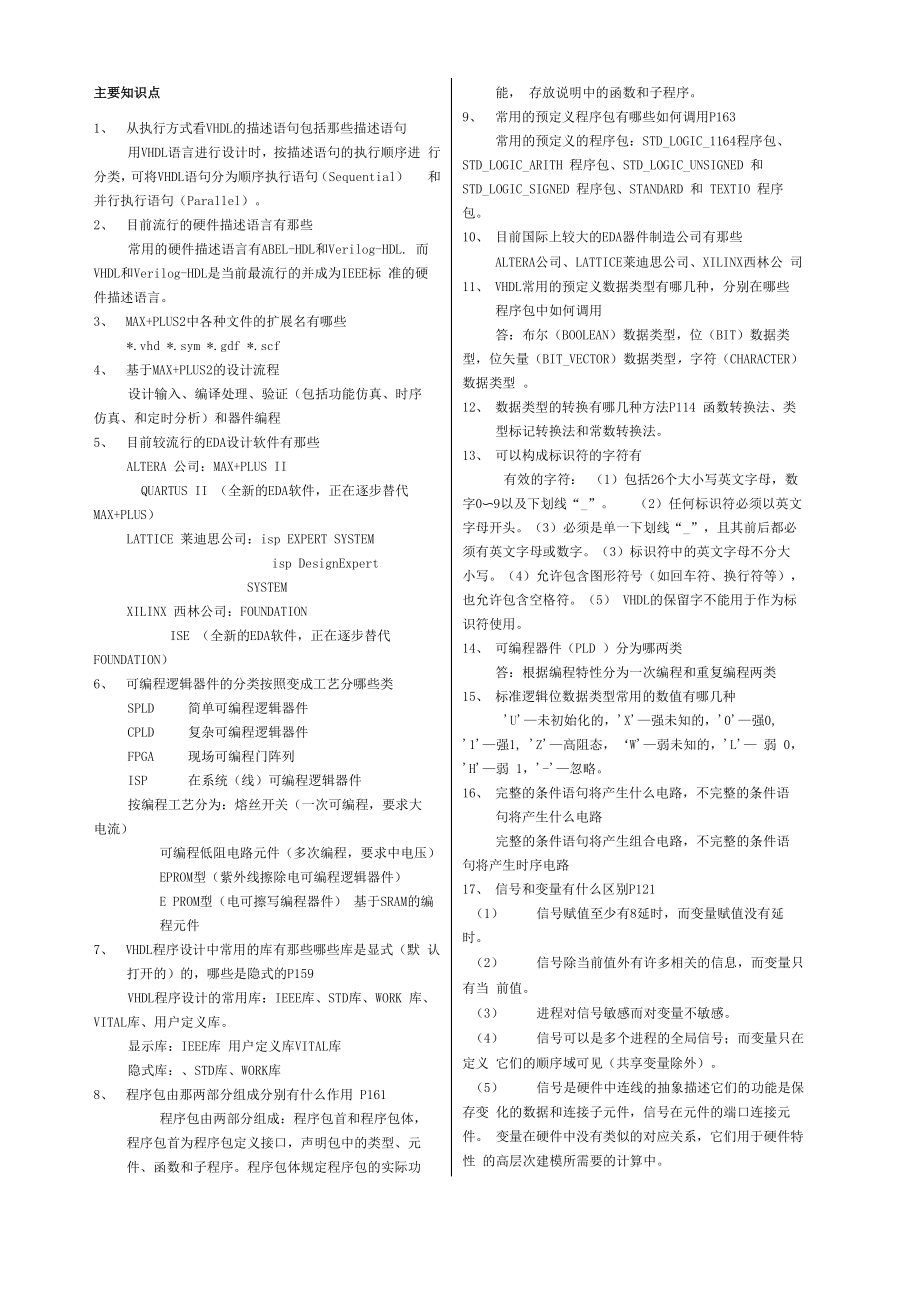

1、主要知识点1、从执行方式看VHDL的描述语句包括那些描述语句用VHDL语言进行设计时,按描述语句的执行顺序进 行分类,可将VHDL语句分为顺序执行语句(Sequential) 和并行执行语句(Parallel)。2、目前流行的硬件描述语言有那些常用的硬件描述语言有ABEL-HDL和Verilog-HDL. 而VHDL和Verilog-HDL是当前最流行的并成为IEEE标 准的硬件描述语言。3、MAX+PLUS2中各种文件的扩展名有哪些*.vhd *.sym *.gdf *.scf4、基于MAX+PLUS2的设计流程设计输入、编译处理、验证(包括功能仿真、时序 仿真、和定时分析)和器件编程5、目

2、前较流行的EDA设计软件有那些ALTERA 公司:MAX+PLUS IIQUARTUS II (全新的EDA软件,正在逐步替代 MAX+PLUS)LATTICE 莱迪思公司:isp EXPERT SYSTEMisp DesignExpertSYSTEMXILINX 西林公司:FOUNDATIONISE (全新的EDA软件,正在逐步替代 FOUNDATION)6、可编程逻辑器件的分类按照变成工艺分哪些类SPLD简单可编程逻辑器件CPLD复杂可编程逻辑器件FPGA现场可编程门阵列ISP在系统(线)可编程逻辑器件按编程工艺分为:熔丝开关(一次可编程,要求大 电流)可编程低阻电路元件(多次编程,要求中

3、电压)EPROM型(紫外线擦除电可编程逻辑器件)E PROM型(电可擦写编程器件) 基于SRAM的编程元件7、VHDL程序设计中常用的库有那些哪些库是显式(默 认打开的)的,哪些是隐式的P159VHDL程序设计的常用库:IEEE库、STD库、WORK 库、VITAL库、用户定义库。显示库:IEEE库 用户定义库VITAL库隐式库:、STD库、WORK库8、程序包由那两部分组成分别有什么作用 P161程序包由两部分组成:程序包首和程序包体, 程序包首为程序包定义接口,声明包中的类型、元 件、函数和子程序。程序包体规定程序包的实际功能, 存放说明中的函数和子程序。9、常用的预定义程序包有哪些如何调

4、用P163常用的预定义的程序包:STD_LOGIC_1164程序包、 STD_LOGIC_ARITH 程序包、STD_LOGIC_UNSIGNED 和 STD_LOGIC_SIGNED 程序包、STANDARD 和 TEXTIO 程序包。10、目前国际上较大的EDA器件制造公司有那些ALTERA公司、LATTICE莱迪思公司、XILINX西林公 司11、VHDL常用的预定义数据类型有哪几种,分别在哪些 程序包中如何调用答:布尔(BOOLEAN)数据类型,位(BIT)数据类 型,位矢量(BIT_VECTOR)数据类型,字符(CHARACTER) 数据类型 。12、数据类型的转换有哪几种方法P11

5、4 函数转换法、类型标记转换法和常数转换法。13、可以构成标识符的字符有有效的字符: (1)包括26个大小写英文字母,数 字09以及下划线“_”。(2)任何标识符必须以英文字母开头。(3)必须是单一下划线“_”,且其前后都必 须有英文字母或数字。(3)标识符中的英文字母不分大 小写。(4)允许包含图形符号(如回车符、换行符等), 也允许包含空格符。(5) VHDL的保留字不能用于作为标 识符使用。14、可编程器件(PLD )分为哪两类答:根据编程特性分为一次编程和重复编程两类15、标准逻辑位数据类型常用的数值有哪几种U未初始化的,X强未知的,0强0, 1强1, Z高阻态,W弱未知的,L 弱 0

6、,H弱 1,-忽略。16、完整的条件语句将产生什么电路,不完整的条件语 句将产生什么电路完整的条件语句将产生组合电路,不完整的条件语 句将产生时序电路17、信号和变量有什么区别P121(1)信号赋值至少有8延时,而变量赋值没有延时。(2)信号除当前值外有许多相关的信息,而变量只有当 前值。(3)进程对信号敏感而对变量不敏感。(4)信号可以是多个进程的全局信号;而变量只在定义 它们的顺序域可见(共享变量除外)。(5)信号是硬件中连线的抽象描述它们的功能是保存变 化的数据和连接子元件,信号在元件的端口连接元件。 变量在硬件中没有类似的对应关系,它们用于硬件特性 的高层次建模所需要的计算中。(6 )

7、信号赋值和变量赋值分别使用不同的赋值符号“=”和“:=”,信号类型和变量类型可以完全一致, 也允许两者之间相互赋值,但要保证两者的类型相同。18、VHDL作为工业标准,是由那个机构制定并公布的。IEEE19、实体部分的端口模式有四个类型。OUT 单向输出端口IN单向输入端口INOUT输入输出双向端口BUFFER反馈式双向端口20、从执行方式看VHDL的基本描述语句包括哪两大基本描述语句顺序语句 并行语句21、VHDL文件存盘时,其主文件名应与实体名一致,扩 展名应为什么呢.VHD22、硬件描述语言(HDL)的种类很多ABEL-HDL,AHDL,VHDL,Verilog-HDL.23、EDA技术

8、的含义。EDA技术就是以计算机为工作平台、以EDA软件工具 为开发环境、以硬件描述语言为设计语言、以 ASIC(Application Specific Integrated Circuits)为 实现载体的电子产品自动化设计的过程24、目前较流行的集成EDA开发环境(软件)有那些同第5题25、简述EDA技术的CPLD/FPGA的设计流程。26、写出实体中的PORT语句结构并说明其作用。 实体端口说明的一般书写格式如下:PORT(端口名:端口模式 数据类型;端口名:端口模式 数据类型);作用:由PORT语句引导的端口说明语句是对一个设计实 体界面的说明。端口为设计实体和外部环境的动态通信 提供

9、通道。27、简述EDA技术经历了那几个发展阶段。1). CAD (计算机辅助设计)阶段2). CAE(计算机辅助工程)阶段3). ESDA (电子系统设计自动化)阶段28、写出元件例化语句语句格式,并说明其作用。元件例化语句由两部分组成,第一部分是对一个现 成的设计实体定义为一个元件,语句的功能是对待调用 的元件作出调用声明,它的最简表达式如下所示:COMPONENT 元件名 ISPORT (端口名表) ;END COMPONENT 文件名 ;元件例化语句的第二部分则是此元件与当前设计 实体(顶层文件)中元件间及端口的连接说明。语句的表 达式如下:例化名:元件名PORTMAP(端口名= 连接端

10、口名,);29、试比较图形输入法和文本输入法有何优缺点30、结构体的语言格式与作用。ARCHITECTURE结构体名OF实体名IS(说明语句) 用来说明和定义数据对象,类型等, 可省略BEGIN(功能描述语句) 用来描述内部电路功能的,不 可省略END ARCHITECTURE 结构体名; 结构体用来描述设计实体的结构或行为,即描述一 个实体的功能,把设计实体的输入和输出之间的联系建 立起来。31、写出PROCESS语句结构的一般表达格式PROCESS语句格式PROCESS语句的表达格式如下:进程标号:PROCESS (敏感信号参数表)IS进程说明部分BEGIN顺序描述语句END PROCES

11、S 进程标号;32、进程语句的设计(或使用)要点P140(1)虽然同一结构体中的进程之间是并行运行的, 但同一进程中的逻辑描述语句则是顺序运行的,因而在 进程中只能设放置顺序语句。(2)进程的激活必须由敏感信号表中定义的任一 敏感信号的变化来启动,否则必须有一显式的WAIT语句 来激活。(3)结构体中多个进程之所以能并行同步运行,一 个很重要的原因是进程之间的通信是通过传递信号和共 享变量值来实现的。(4)进程是重要的建模工具。进程结构不但为综合 器所支持,而且进程的建模方式将直接影响仿真和综合 结果。33、并行信号赋值语句有哪几种其语句格式为何1)简单信号赋值语句赋值目标=表达式;2)条件信

12、号赋值语句 赋值目标=表达式1 WHEN 赋值条件1 ELSE表达式2 WHEN赋值条件2ELSE表达式n;3)选择信号赋值语句的语句格式如下:WITH选择表达式SELECT 赋值目标信号=表达式1 WHEN 选择值1, 表达式2 WHEN选择值2,表达式n WHEN选择值n;34、EDA技术常用的输入方法有原理图输入HDL文本输入eda设计输入的三种形式:原理图输入,状态输入,波形输入35、什么是实体和结构体,其功能是什么实体是一个设计实体的表层设计单元,其功能是对 这个设计体与外部电路进行接口描述。它规定了设计单 元的输入输出接口信号或引脚,是设计实体经封装后对 外界的一个通信界面。结构体

13、用来描述设计实体的结构 或行为,即描述一个实体的功能,把设计实体的输入和 输出之间的联系建立起来。36、MAX+pulsII的原理图输入法、文本输入法、波形输入法生成的文件扩展名为原理图输入法生成的文件扩展名为*.gdf 文本输入法生成的文件扩展名为*.vhd 波形输入法生成的文件扩展名为*.scf37、VHDL的操作符有那几大类每一类的操作符分别是什么每一类操作符可以对那些数据进行操作(运算) 见最后的图38、VHDL操作符的优先级最后的图39、结构体常见的功能语句有那些信号(SIGNA)、数据类型(TYPE)、常数(CONSTANT)、 元件(COMPONENT)、函数(FUNCTION)

14、和过程(PROCEDURE ) 等加以说明的语句。40、子程序分为那两类,其结构为什么。P152-153子程序包括过程和函数,包括过程(可单独存在,多 个返回值,有输入/出、双向参数,一般看做一种语句结 构)和函数(作为语句的一部分调用,一个返回值,所有 参数都是输入参数,看作表达式的一部分),可在VHDL 的结构体或程序包中任何位置调用子程序。41、VHDL的标识符由什么构成。.同13题42、CASE语句的一般形式在使用当中的注意事项。P125-126CASE语句的一般形式为:CASE表达式ISWHEN值1=语句A;WHEN值2=语句B;WHEN OTHERS= 语句 C;END CASE注

15、意事项:(1)WHEN条件句中的选择值或标识符所 代表的值必须在表达式的取值范围内。2)除非所有条件句中的选择值能完整覆盖CASE语 句中表达式的取值,否则最后一个条件句中的选择必须 用关键词OTHERS表示以上已列的所有条件句中未能列出 的其它可能的取值。(3)CASE语句中的选择值只能出现一次,不允许 有相同选择值的条件语句出现。(4)CASE语句执行中必须选中,且只能选中所列 条件语句中的一条。43、试着比较IF和CASE语句的差异P127与IF语句相比,CASE语句组的程序可读性比较好,这是 因为它把条件中所有可能出现的情全部列出来了,可执 行条件比较清晰。而且CASE程序的执行过程不

16、像IF语 句中那样有一个逐项条件条件顺序比较的过程。CASE语 句中条件句的次序是不重要的,它的执行过程更接近于 并行方式。但是在一般情况下,经过综合后,对相同的 逻辑功能,CASE语句比IF语句的描述耗用更多的硬件资 源,而且有的逻辑功能CASE语句无法描述,只能使用IF 语句来描述.44、FOR循环语句的一般形式P127FOR循环语句的一般形式为:循环标号: FOR 循环变量 IN 循环次数范围LOOP顺序处理语句END LOOP循环标号;45、VHDL数据对象有哪几种P101在VHDL中,数据对象有三种(1)常量(CONSTANT)(2)变量(VARIABLE) (3)信号(SIGNAL

17、)。46、变量和信号的区别P105同18题47、赋值语句分哪些类,分别写出一句赋值语句。 赋值语句分为信号赋值语句和变量赋值语句。变量赋值语句和信号赋值语句的语法格式如 下:变量赋值目标 :=赋值源;信号赋值目标 =赋值源;48、实现时序电路和逻辑组合电路分别用什么语句实 现,分别写出他们的一般表式。完整的条件语句将产生组合电路,不完整的条件语 句将产生时序电路完整的条件语句格式:49、写出实体、结构体的一般语句结构并说明其作用。50、简述VHDL中顺序语句有哪些1、赋值语句2、转向控制语句语句4、子程序调用语句5、返回语句6、NULL语句7.其他语句51、简述VHDL中并行语句有哪些1、进程

18、语句2、并行信号赋值语句3、块语句结构(BLOCK)4、并行过程调用语句5、元件例化 语句6、 生成语句52、试写出三种IF语句的语句结构。IF语句是一种条件语句,它根据语句中所设置的一 种或多种条件,有选择地执行指定的顺序语句,常见的 IF语句有以下3种形式。(1)IF 条件 THEN语句END IF;(2)IF 条件 THEN语句ELSE语句END IF;(3) IF 条件 THEN语句ELSIF 条件 THEN语句ELSE语句END IF;53 转向控制语句有哪几种 P123转向控制语句共有五种:(1) IF语句(2) CASE语 句(3) LOOP语句(4) next语句(5) exi

19、t语句54 什么是重载操作符常用的重载操作符定义在那 个程序包中为了方便各种不同数据类型间的运算,VHDL允 许用户对原有的基本操作符重新定义, 赋予新的含义 和功能,从而建立一种新的操作符,这就是重载操作 符。常用的重载操作符程序包:STD_LOGIC_UNSIGNED、 STD_LOGIC_ARITH 、STD_LOGIC_SIGNED55 什么是重载函数,什么是重载过程同样名称的函数可以用不同的数据类型作为此函数的参数定义多次,以此定义的函数称为重载函数56 VHDL设计的有限状态机从信号输出方式上分为哪 两类主要区别是什么有限状态机从信号输出方式上分为Mealy(米立)型 和Moore

20、(摩尔)型两种状态机。57 一般有限状态机的的组成有哪几部分 一般的状态机通常包含说明部分、时序进程、组合进程、辅助进程等几个部分。58 VHDL的描述风格有哪几种 行为描述、数据流描述和结构描述第四章习题答案2 VHDL的基本结构是什么各部分的功能分别是什么 答:参考课本77页,最下面一段。4、写出3输入与非门的实体描述。ENTITY nand_3 ISPORT (a , b, c: IN STD_LOGIC);q: OUT STD_LOGIC );END nand_3;5、例4-1是2选1的多路选择器的VHDL描述,在结构 体的描述中使用了 “WHEN-ELSE”语句,但也可以用其他 语句

21、来进行描述,试描述之。用IF语句描述:ENTITY mux21a ISPORT (a,b:IN BIT;s:IN BIT;q:OUT BIT);END mux21a;ARCHITECTURE one OF mux21a ISBEGINPROCESS (a,b,s)BEGINIF s=0 THENq=a;ELSEq= b;END IF;END PROCESS;END one;6、试写出4选1多路选择器的VHDL描述。选择控制信 号为si和s0,输入信号为a, b, c, d,输出信号为y。 也可以参考P125页,例5-9那样 使用IF语句LIBRARY IEEE;USE mux4_1 ISPOR

22、T(a,b,c,d,s0,s1:IN STD_LOGIC;y:OUT STD_LOGIC);END mux4_1;ARCHITECTURE behave OF mux4_1 ISSIGNAL sel:STD_LOGIC_VECTOR(1 DOWNTO 0);BEGINsel y y y ynull;END CASE;END PROCESS;END behave;7. 试给出1位全减器的VHDL描述,要求首先设计1位 半减器,然后用例化语句将它们连接起来。设x为被减 数,y为减数,sub_in是借位输入,diff是输出差, sub_out是借位输出。-半减器描述LIBRARY IEEE;USE

23、h_sub ISPORT(a,b:IN STD_LOGIC;co,so:OUT STD_LOGIC);END ENTITY h_sub ;ARCHITECTURE fh1 OF h_sub ISBEGINso=a XOR b;co=NOT a AND b;END ARCHITECTURE fh1;表M2丰减需其值表END ENTITY or2a;ARCHITECTURE one OF or2a ISBEGINc=a OR b;END ARCHITECTURE one;-全减器描述LIBRARY IEEE;USE f_sub1 ISPORT(x,y,sub_in:IN STD_LOGIC; su

24、b_out,diff:OUT STD_LOGIC);END ENTITY f_sub1 ;ARCHITECTURE strl OF f_sub1 ISCOMPONENT h_subPORT(a,b:IN STD_LOGIC;co,so:OUT STD_LOGIC);END COMPONENT;COMPONENT or2aPORT(a,b:IN STD_LOGIC;c:OUT STD_LOGIC);END COMPONENT;SIGNAL d,e,f:STD_LOGIC;BEGINu1:h_sub PORT MAP(x,y,d,e);u2:h_sub PORT MAP(e,sub_in,f,di

25、ff);u3:or2a PORT MAP(d,f,sub_out);END ARCHITECTURE strl ;第五章5-1.试说明实体端口模式BUFFER和INOUT的不同之处答:BUFFER端口:缓冲模式,具有读功能的输出模式,迦 bo山 C10 00 00 11 11 01 01 10 0-或门描述LIBRARY IEEE;USE or2a ISPORT(a,b:IN STD_LOGIC;c:OUT STD_LOGIC); 即信号输出到实体外部,但同时也在内部反馈使用,不 允许作为双向端口使用。而INOUT端口:双向模式,即 信号的流通是双向的,既可以对此端口赋值,也可以通过 此端口读

26、入数据。的数据对象有哪几种它们之间有什么不同答:VHDL的数据对象有三种:信号、变量、常量。它们之间的的区别如下:信号赋值至少有延时,而变量和常量没有;信号除当前 值外,有许多相关信息,变量只有当前值,常量的值在 设计实体中始终不变;进程对信号敏感而对变量及常量 不敏感;信号可以是多个进程的全局信号,变量只在定义 它们的顺序域可见,而常量的使用范围取决于它被定义 的位置;信号是硬件连线的抽象描述信号赋值,赋值符号 = 而变量和常量的赋值符号 :=。5-3.说明下列各定义的意义:答 SIGNAL a , b , c : BIT : = 0;- - 定义 3 个位 数据类型的信号a、b、c,它们取

27、值为0;CONSTANT TIME1 , TIME2 : TIME : 20ns ;- -定义2个 时间数据类型的常量TIME1、TIME2,它们值为20ns;VARIABLE x , y , z : STD_LOGIC : = x ;- -定义 3个标准逻辑位STD_L0GIC数据类型的变量x、y、z,它 们的值是强未知的。5-4.什么是重载函数重载运算符有何用处如何调用 重载运算符函数答:为了方便各种不同数据类型间的运算,VHDL允许用 户对原有的基本操作符重新定义,赋予新的含义和功能, 从而建立一种新的操作符,这就是重载操作符,定义这 种操作符的函数成为重载函数。重载运算符的作用是为 了

28、方便各种不同的数据类型间的运算。要调用重载运算 符函数,先要在程序包中进行函数体的定义,调用的格 式如下:x =函数名(参数1,参数2, )参数个数和类型与所定义的函数要保持一致。5-5.数据类型BIT INTEGER BOOLEAN分别定义 在哪个库中哪些库和程序包总是可见的.答:数据类型BIT INTEGER BOOLEAN均定义在STD 库中。IEEE 库和程序包、STD_LOGIC_UNSIGNED、 STD_LOGIC_SIGNED、STD_LOGIC_ARITH 等总是可见的。5-6.函数和过程有什么区别答:子程序有两种类型,即过程(PROCEDURE)和函数 (FUNCTION)

29、 o它们的区别在于:过程的调用可以通过其 界面获得多个返回值,而函数只能返回一个值;在函数 入口中,所有参数都是输入参数,而过程有输入参数、 输出参数和双向参数;过程一般被看作一种语句结构, 而函数通常是表达式的一部分;过程可以单独存在,而 函数通常作为语句的一部分调用。5-7.若在进程中加入WAIT语句,应注意哪几个方面 的问题 答:应注意以下问题:已列出敏感信号的进程中不能 使用任何形式的WAIT语句;一般情况下,只有WAIT UNTIL格式的等待语句可以被综合器所接受,其余语句格 式只能在VHDL仿真器中使用;在使用WAIT ON语句的 进程中,敏感信号量应写在进程中的WAIT ON语句

30、后面; 在不使用WAIT ON语句的进程中,敏感信号量应在开 头的关键词PROCESS后面的敏感信号表中列出。5-8.哪些情况下需用到程序包STD_LOGIC_UNSIGNED 试举一例。答:调用数据类型变换函数或重载运算符函数时;定 义UNSIGNED类型的数据时。举例如下:LIBRARY IEEE;USE USEELSE temp:=temp+16;END IF; 5-9.为什么说一条并行赋值语句可以等效为一个进 程如果是这样的话,怎样实现敏感信号的检测 答:因为信号赋值语句的共同点是赋值目标必须都是信 号,所有赋值语句与其它并行语句一样,在结构体内的 执行是同时发生的,与它们的书写顺序没

31、有关系,所以 每一信号赋值语句都相当于一条缩写的进程语句。由于 这条语句的所有输入信号都被隐性地列入此缩写进程的 敏感信号表中,故任何信号的变化都将相关并行语句的 赋值操作,这样就实现了敏感信号的检测。5-10.比较CASE语句和WITH_SELECT语句,叙述它 们的异同点 答:相同点:CASE语句中各子句的条件不能有重叠,必 须包容所有的条件;WITH_SECLECT语句也不允许选择值 有重叠现象,也不允许选择值涵盖不全的情况。另外, 两者对子句各选择值的测试都具有同步性,都依赖于敏 感信号的变化。不同点:CASE语句只能在进程中使用, 至少包含一个条件语句,可以有多个赋值目标; WITH

32、_SECLECT语句根据满足的条件,对信号进行赋值, 其赋值目标只有一个,且必须是信号。5-11.将以下程序段转换为WHEN_ELSE语句:PROCESS (a , b ,c ,d)BEGINIF a=0AND b=1THEN NEXT1 =1101;ELSEIFa=0THENNEXT1=d;ELSEIFb=1THENNEXT1=c;ELSE NEXT1 =1011;END IF;END PROCESS;原程序转换如下:ARCHITECTURE one OF mux ISBEGINNEXT1 =1101WHEN a=0AND b=1ELSE d WHEN a=0ELSEc WHEN b=1EL

33、SE 1011;END one;END PROCESS;5-12试给出一位全减器的算法描述、数据流描述 结构描述和混合描述。行为(算法)描述LIBRARY IEEE;USE f_sub ISPORT(x,y,sub_in:IN STD_LOGIC; sub_out,diff:OUT STD_LOGIC); END f_sub ;ARCHITECTURE bhv OF f_sub ISSIGNAL tmp:STD_LOGIC_VECTOR(2 DOWNTO 0); BEGINtmp diff=0;sub_outdiff=1;sub_outdiff=1;sub_outdiff=0;sub_outd

34、iff=1;sub_outdiff=0;sub_outdiff=0;sub_outdiff=1;sub_out NULL;END CASE;END PROCESS;END bhv ;数据流描述LIBRARY IEEE;USE f_sub ISPORT(x,y,sub_in:IN STD_LOGIC; sub_out,diff:OUT STD_LOGIC);END f_sub ;ARCHITECTURE rtl OF f_sub ISBEGINdiff=x XOR y XOR sub_in;sub_out=(NOT x AND y )OR (x XNOR y) AND sub_in);END r

35、tl ; 结构描述:LIBRARY IEEE; - - 半减器 USE h_sub ISPORT(a,b:IN STD_LOGIC; co,so:OUT STD_LOGIC);END h_sub ;ARCHITECTURE fh1 OF h_sub IS BEGINso=a XOR b;co=NOT a AND b; END fh1;LIBRARY IEEE; - -或门描述 USE or2a ISPORT(a,b:IN STD_LOGIC;c:OUT STD_LOGIC);END or2a;ARCHITECTURE one OF or2a IS BEGINc=a OR b;END one;L

36、IBRARY IEEE; - -全减器描述 USE f_sub1 ISPORT(x,y,sub_in:IN STD_LOGIC; sub_out,diff:OUT STD_LOGIC);END f_sub1 ;ARCHITECTURE strl OF f_sub1 ISCOMPONENT h_subPORT(a,b:IN STD_LOGIC;co,so:OUT STD_LOGIC);END COMPONENT;COMPONENT or2aPORT(a,b:IN STD_LOGIC;c:OUT STD_LOGIC);END COMPONENT;SIGNAL d,e,f:STD_LOGIC;BEG

37、INu1:h_sub PORT MAP(x,y,d,e);u2:h_sub PORT MAP(e,sub_in,f,diff); u3:or2a PORT MAP(d,f,sub_out);END strl ;5-13用VHDL描述下列器件的功能:(1)十进制一BCD码编码器,输出使能为低电平有效。 library ieee;use bin_bcd isport(bin : in integer range 0 to 20;ena: in std_logic;BCD_out: out std_logic_vector(7 downto0); end;architecture a of bin_

38、bcd is beginBinary_BCD : BlockBEGINBCD_out =00000000 WHEN BIN = 0 ELSE00000001WHEN BIN = 1 ELSE00000010WHENBIN=2ELSE00000011WHENBIN=3ELSE00000100WHENBIN=4ELSE00000101WHENBIN=5ELSE00000110WHENBIN=6ELSE00000111WHENBIN=7ELSE00001000WHENBIN=8ELSE00001001WHENBIN=9ELSE00010000WHENBIN=10ELSE00010001WHENBIN

39、=11ELSE00010010WHENBIN=12ELSE00010011WHENBIN=13ELSE00010100WHENBIN=14ELSE00010101WHENBIN=15ELSE00010110WHENBIN=16ELSE00010111WHENBIN=17ELSE00011000WHENBIN=18ELSE00011001WHENBIN=19ELSE00100000WHENBIN=20ELSE00000000;end block;end a;(2)时钟(可控)RS触发器。LIBRARY IEEE;USE ffrs ISPORT(s,r: IN std_logic;q,qb: OU

40、T std_logic);END ffrs;ARCHITECTURE rtl OF ffrs ISSIGNAL qn,nqn: std_logic;BEGINqn= r NOR nqn;nqn= s NOR qn;q=qn;qb=nqn;END rtl;(3) 带复位端、置位端、延迟为15ns的响应CP下降沿 触发的JK触发器。library ieee;use jkff isport(j,k,rst,clr : IN bit;clk : in bit;q,nq : out bit);end;architecture a of jkff issignal q_s,nq_s : bit;begin

41、process(j,k,rst,clr,clk)beginif rst=1 thenq_s=1;nq_s=0;elsif clkevent and clk=0 then if clr=1 thenq_s=0;nq_s=1;elsif j=0 and k=1 thenq_s=0;nq_s=1;elsif j=1 and k=0 thenq_s=1;nq_s=0;elsif j=1 and k=1 thenq_s=not q_s;nq_s=not nq_s;end if;elsenull;end if;q=q_s;nq=nq_s;end process;end a;(4)集成计数器74161Lib

42、rary ieee;clk,LDN,CLRNin std_logic;d,c,b,ain std_logic;carryout std_logic;qd,qc,qb,qa);out std_logicuse cnt4 is port( end;architecture a ofcnt4 issignal data_in:std_logic_vector(3 downto 0);begindata_in0);elsif clkevent and clk=1 thenif ldn=0 thencnt:=data_in;elsecnt:=cnt+1;end if;end if;case cnt is

43、when 1111= carry carry=0;end case;qa=cnt(0);qb=cnt(1);qc=cnt(2);qd=cnt(3);end process;end a;程序2LIBRARY IEEE;USE S_C74161 ISPORT(clk, ldn,clrn,enp,ent: IN STD_LOGIC;din:IN STD_LOGIC_VECTOR(3DOWNTO 0);q: OUT STD_LOGIC_VECTOR(3DOWNTO 0) ;rco: OUT STD_LOGIC );END S_C74161 ;ARCHITECTURE behav OF S_C74161

44、 ISSIGNAL q1: STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(clk, clrn)BEGINIF clrn = 0 THENq1 = 0000 ;ELSIF (clkEVENT AND clk = 1) THENIF ldn=0 THEN q1=din ;ELSIF (enp=1 and ent =1 ) THEN q1= q1+1;END IF;END IF;q= q1;END PROCESS;rco = q1(3) and q1(2) and q1(1) and q1(0) and ent;END behav;(5) 集成移位寄存器7419

45、4LIBRARY IEEE;USE S_R74194 ISPORT(clrn, clk, slsi, srsi: IN STD_LOGIC; din:IN STD_LOGIC_VECTOR(3 DOWNTO 0);ss:IN STD_LOGIC_VECTOR(1 DOWNTO 0);q:OUT STD_LOGIC_VECTOR(3 DOWNTO0);END S_R74194 ;ARCHITECTURE bhv OF S_R74194 ISSIGNAL q1:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(clk,clrn)BEGINIF(clrn=0)THE

46、Nq1=0000;ELSIF(clkEVENT AND clk=1)THENIF(ss=11)THENq1=din;ELSIF(ss=01)THENq1=srsi&q1(3 downto 1);ELSIF(ss=10)THENq1=q1(2 downto 0)&slsi;END IF;END IF; q=q1;END PROCESS;END bhv;5-14用VHDL描述一个三态输出的双4选一的数据 选择器,其地址信号共用,且各有一个低电平有效的使 能端。答:程序1,使用两个并行关系的选择信号赋值语句 library ieee;use dual_mux_41 is port(a,b,c,d :

47、 in std_logic;ena_n,enb_n : in std_logic;s : in std_logic_vector(1 downto 0); outa,outb : out std_logic);end; architecture a of dual_mux_41 issignal p,q : std_logic_vector(2 downto 0); beginp=ena_n & s; q=enb_n & s;with p select outa=a when 000, b when 001, c when 010, d when 011, Z when others;with

48、 q select outbq1q1q1q1null;end case;elseq1q2q2q2q2null;end case;elseq2=Z;END IF;End process;End bhv;5-15.试用并行信号赋值语句分别描述下列器件的 功能:(1) 3-8译码器 答:功能描述如下:LIBRARY IEEE;USE ENTITY decoder38 ISPORT(a,b,c,g1,g1a,a2b:IN STD_LOGIC;q:OUT STD_LOGIC_VECTOR(7 DOWNTO0);END decoder38;ARCHITECTURE behave38 OF decoder3

49、8 ISSIGNAL inda: STD_LOGIC_VECTOR(2 DOWNTO 0); BEGINindaqq=XXXXXXXX;END CASE;ELSEEND IF;END PROCESS;END behave38;(2) 8选1数据选择器 答:功能描述如下:LIBRARY IEEE;USE ENTITY mux8 ISPORT(d0,d1,d2,d3,d4,d5,d6,d7:INSTD_LOGIC_VECTOR(7 DOWNTO 0);s0,s1,s2:IN STD_LOGIC;q:OUT STD_LOGIC_VECTOR(7 DOWNTO0);END mux8;ARCHITECT

50、URE behave OF mux8 ISSIGNAL s: STD_LOGIC_VECTOR(2 DOWNTO 0);BEGINs =s2&s1&s0;WITH s SECLECTd =d0 WHEN 000,d1 WHEN 001,d2 WHEN 010,d3 WHEN 011,d4 WHEN 100,d5 WHEN 101,d6 WHEN 110, d7 WHEN 111,XWHEN OTHERS;END behave;5-16利用生成语句描述一个由n个一位全减器构成 的n位减法器,n的默认值为4。library ieee;use f_sub4_2 isGENERIC (n : INTE

51、GER := 4);port(a,b : IN STD_LOGIC_VECTOR(n-1 DOWNTO 0); cin : IN std_logic;diff: out STD_LOGIC_VECTOR(n-1 DOWNTO 0);Cout: OUT std_logic);end;architecture a of f_sub4_2 iscomponent f_sub1 isport( a,b,cin : IN std_logic; diff,Cout : OUT std_logic );end component;signal c :STD_LOGIC_VECTOR(n DOWNTO 0);

52、 beginc(0)=cin;n1: for i in 0 to n-1 generateU1: f_sub1 port map(a(i),b(i),c(i),diff(i),c(i+1);end generate; cout=c(n);end a;5-17用VHDL语言设计实现输出占空比为50%的1000 分频器。library ieee;use div_1000 is port(clk ,clr: in std_logic;div : out std_logic);end; architecture a of div_1000 is signal q : std_logic;begin div=q; process(clk,clr) variable cnt : integer range 0 to 499;beginif clr=1 then cnt:=0; q=0;elsif rising_edge(clk) then if cnt=499 then cnt:=0;q=not q;else cnt:=cnt+1;end if;end if;end process;end a;

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。