DDR的PCB设计要求实例介绍

DDR的PCB设计要求实例介绍

《DDR的PCB设计要求实例介绍》由会员分享,可在线阅读,更多相关《DDR的PCB设计要求实例介绍(9页珍藏版)》请在装配图网上搜索。

1、DDR 的 PCB 设计要求实例介绍随着嵌入式系统处理能的逐步提高,拥有更高时钟频率和更大存储空间的 DDRSDRAM(Double Data Rate SDRAM,以下简称DDR)在新设计中越来越多被使用。DDR虽然能够给设计带来更好的性能,但是设计者必须比以往的SDRAM设计更小心 地处理 DDR 部分的 PCB 布线部分,否则不仅不能实现好的性能,整个系统的稳定性也会 受到影响。DDR比传统的SDR有更短的信号建立保持时间、更干净的参考电压、更紧密的 走线匹配和新的 I/O 口信号,并且需要合适的终端电阻匹配。本文以DDR设计实例为基础,根据EDA方面实际的DDR约束方式,从以下几个方面

2、 介绍DDR设计相关事项。一、信号分组及布局布线要求DDR 信号可分为时钟、数据、地址/命令、控制等四个信号组。各信号组介绍如下:1时钟组:由于采用更高的时钟频率及双沿采样数据的方式, DDR 采用差分时钟。差分时钟的走 线要求如下:以地平面为参考,给整个时钟回路的走线提供一个完整的地平面,给回路电流 提供一个低阻抗的路径。所有的DDR差分时钟信号都必须在关键平面上走线,尽量避免层 到层的转换。线宽和差分间距需要参考DDR控制器的实施细则,信号线的单线阻抗应控制 在5060 Q,差分阻抗控制在100120 Q。时钟信号到其他信号应保持在20 mil*以上, 防止对其他信号的干扰。蛇形走线的间距

3、不应小于20 mil。2数据组:数据组包括DQ、DQS、DM。以低8位数据为例,该数据组包括:DQ7.0、DQS0、 DM0 数据组布线要求如下:以地平面为参考,给信号回路提供完整的地平面。特征阻抗控 制在5060 Q。与其他非DDR信号间距至少隔离20 mil。3 地址、命令组:地址组包括ADD、BANK、RAS、CAS、WE。该组布线要求如下:保持完整的地和电 源平面。特征阻抗控制在5060 Q。信号线宽参考具体设计实施细则。信号组与其他非DDR 信号间距至少保持在20 mil以上。4控制组:控制组包括CS、CKE。该组布线要求如下:需要有一个完整的地平面和电源平面作参 考。为了防止串扰,

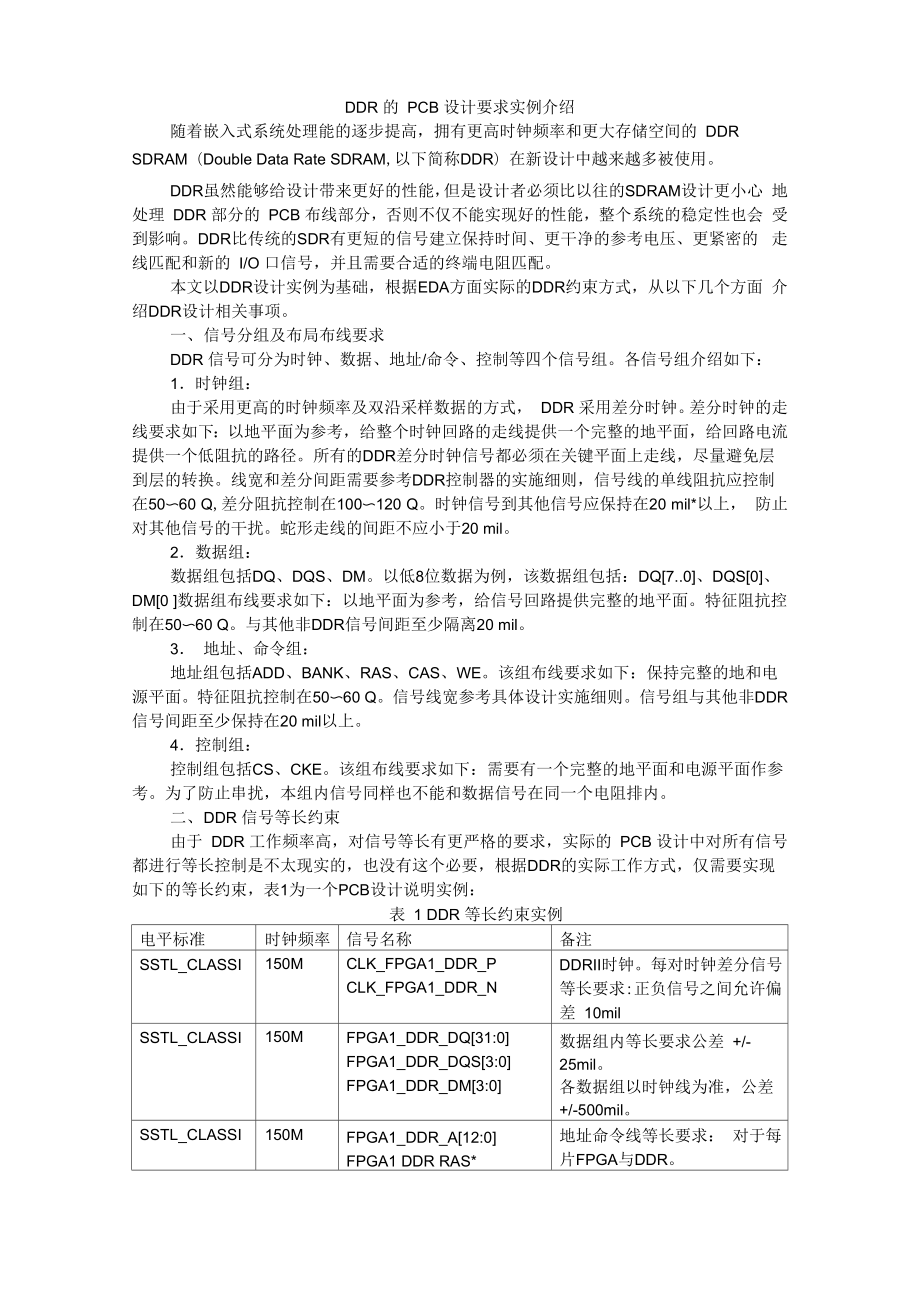

4、本组内信号同样也不能和数据信号在同一个电阻排内。二、DDR 信号等长约束由于 DDR 工作频率高,对信号等长有更严格的要求,实际的 PCB 设计中对所有信号 都进行等长控制是不太现实的,也没有这个必要,根据DDR的实际工作方式,仅需要实现 如下的等长约束,表1为一个PCB设计说明实例:表 1 DDR 等长约束实例电平标准时钟频率信号名称备注SSTL_CLASSI150MCLK_FPGA1_DDR_PCLK_FPGA1_DDR_NDDRII时钟。每对时钟差分信号 等长要求:正负信号之间允许偏 差 10milSSTL_CLASSI150MFPGA1_DDR_DQ31:0FPGA1_DDR_DQS3

5、:0FPGA1_DDR_DM3:0数据组内等长要求公差 +/-25mil。各数据组以时钟线为准,公差 +/-500mil。SSTL_CLASSI150MFPGA1_DDR_A12:0FPGA1 DDR RAS*地址命令线等长要求: 对于每片FPGA与DDR。FPGA1_DDR_CAS*FPGA1_DDR_WE*FPGA1 DDR BANK3:0地址命令组与时钟信号等长公 差+/-150mil。根据表1所示,DDR的等长约束只需要四个参数。具体约束界面如图1、2所示。其中差分时钟之间(CLK_P与CLK_N)等长不大于5mil。地址、控制组中每个信号都以 时钟(本规则中为CLK_N)为基准,等长

6、差范围设置为150mil。数据组内以DQ0为基准,等长控制在25mil以内。各数据组之间,以时钟线为基准,等长差范围设置为0-500mil。 声 CILK FPGiA1 -DOR-N* Z CLrFRGAl_DDRJN/ CLK_FFsiGA1_N曲 T:DS-A6X:D20-KS呵曲回22巩84歼Ih餵 T:D9-A6X:D21-KB-: :-5H-EJ # C1LK FPGA1 -DDR-PxZ CLrFPGAl_DORJPCLK_FFGA1_P曲 T D9-B6J :DZ0-JE-7ll-.餵 T:O?-B6X:D21 J65th/ FPGA1_DOR_A品 1 D5I A12A L32

7、Q M8. : . 1- i. - -.-i宙 T7DA12fL:D21-M8池农,工阳,B*15(y-1EDth图1时钟、地址等长约束 擁 FFCAl-DIiFPALDD田 # FFGA1 _DDR_DMU-FFSALDDE5E 芒 FPGA1FPjAIJZiO25 W FPGA1FFGAL:皿25田 *十JFPGAZ5Q / FPGJVLDDFLDOO厂zFPGAJDQ25田 FPGA1_DDFl_Dlj询旷zFP2AI jzm2nEJ # FPGA1J3DFLI3D刑A-FPGAI 丄i25田 y FPGAl_DDR_OaiJi*FPSALDD田 Z FPGA1_ODR_Q*7AM1 :

8、曰 FPGA1 _DDR_DQSZ FPG*l_DQScn:s占TO9-B4.T:O?1-F?伽嗣.|虫庞DW如卸M图2数据组等长约束三、电源DDR由于电平摆幅小,对参考电压稳定度要求很高,特别是Vref和VTT。VREF电压作为信号接收端的参考,由于叠加在VREF电压的串扰或噪声能直接导致 内存总线发生潜在的时序错误、抖动和漂移。因此要求Vref具有良好的性能,纹波尽量小 (50mV)。目前中兴库中有专用的DDR终端匹配电源芯片(LP2996),既能提供良好的参考 电压,也能满足DDR的上电顺序要求,该芯片的SENSE引脚还能根据负载处的实际压降 进行补偿。布线方面VREF最好和VTT在不同

9、平面,以免VTT产生的噪声干扰VREF。而且无论 是在DDR控制器端还是DDR器端,VREF脚附近都应放置去耦电容,消除高频噪声VREF 的走线宽度应该越宽越好,最好铺铜,如果走线的话宽度应大于20mil。Vtt为终端匹配电阻的电源,由于具有较大的瞬时电流,设计时应考虑电源额定电流, 对于一片DDR负载,往往在2A到3A,布线时需铺平面,如果走线则线宽大于应250mil。 Vtt的去耦电容尽量靠近匹配电阻,一般按照两个电阻对应一个电容,如果空间够考虑增加 电容。四、匹配由于DDR信号具有较高翻转率,为了获得更好的信号完整性(减小信号过冲、反射等), 需要进行传输线阻抗匹配,串连电阻匹配以及终端

10、匹配。以Cyclone系列芯片支持的差分 电平标准SSTL CLASSI和SSTL CLASSII为例,匹配方式分别如图3、4所示:图3 SSTL CLASS I差分信号匹配图4 SSTL CLASS II差分信号匹配其中差分信号阻抗为单端50Q,差分100Q。DDR的所有信号均需要进行阻抗控制。 此外对于时钟信号串联终端电阻RS值在1533Q,可选的并联终端电阻RT值在2568 Q,其他信号串联匹配电阻RS值为033 Q,并联匹配电阻RT值应该在2568 Q。具 体匹配电阻值以及电阻位置放置可根据仿真结果进行选择。五、其他总结1. 有效的利用DDR内置的ODT,这样既节约PCB空间,又能够获

11、得更好的匹配效 果。2. 使用FPGA做控制器时,在允许的情况尽量使用小的I/O 口驱动电流,一方面减小 信号过冲,另一方面可延长 DDR 的使用寿命。3如果 DDR 使用较高时钟频率,可以考虑只使用终端电阻匹配,因为源端串联电阻 会减慢信号翻转速度。4.当使用多片DDR并联工作时,布线应注意走线的STUN(比如过孔的位置等)。5等长要求根据实际时钟频率有关,时钟频率较高的时候需要进行仿真。6.对于多片FPGA并联使用的情况,共用的时钟、地址、控制等信号尽量靠近芯片后 再分支。7在使用排阻进行匹配的时候,数据组信号的排阻内不能有其他信号组的信号。带你进入DDR2的世界:DDR2内存技术解析尽管

12、目前DDR2内存的平台还没有大规模普及,但可以肯定的,由于低价LGA775平台配件不断下降, Intel与AMD的全面支持,DDR2皇朝的到来只是时间问题。另外,值得我们关注的是,如果只是在频率上 进行无休止的竞争的话,那么DDR技术终究会曲终人散,DDR老迈的技术在保持成本不变的情况下其性能 难以有大的突破,而DDR2却满足了一些本质上的问题,随着处理器技术的发展,前端总线对内存带宽的要 求是越来越高,拥有更高更稳定运行频率的DDR2内存将会大行其道。一、什么是DDR2?DDR2(Double Data Rate 2) SDRAM是由JEDEC (电子设备工程联合委员会)进行开发的新生代内存

13、 技术标准(如图1),与上一代DDR内存不同的是,虽然同是采用了在时钟的上升/下降延同时进行数据传 输的基本方式,但DDR2内存却拥有两倍于上一代DDR内存预读取能力(即4bit数据读预取)。也就是说, DDR2内存每个时钟能够以4倍外部总线的速度读/写数据,并且能够以内部控制总线4倍的速度运行。图1,最新DDR2 533内存二、为何要DDR2?内存性能,始终是我们所要追求的,从“速度=位宽X频率”的内存性能计算公式来看,提高内存性能 有两种方式,增加内存总线的位宽或者是提高内存工作的频率。但问题是,现在由于发热量以及设计等方 面的限制,导致内存单元无法提高频率,内存总线位宽也不能轻易增加。尽

14、管DDR400中的存储阵列工作频率是200MHz,目前最快的DDR SDRAM的频率(这里不包括那些超频的 内存)达到了 550MHz,它的内部阵列工作频率达到275MHz,这个频率已经很难再继续提高。此时,就需要 一个新的内存标准保证内存频率和性能可以稳定的提高,那就是DDR2内存。DDR采用了 2位预取(2-bit prefetch),也就是2: 1的数据预取,2bit预取架构允许内部的队列(column) 工作频率仅仅为外部数据传输频率的一半。在SDRAM中数据传输率完全参考时钟信号,因此数据传输率和 时钟频率一样。DDR2采了 4位预取(4-bit prefetch),这就是DDR2提

15、高数据传输率的关键,可以在不提 高内部存储阵列频率的情况下提高数据输出带宽(如图2)。DDR IData Freq = 200 h.dHznnCore frequency =100 MHzGlock Freq =100 h.dHzMemory Wl ArrayP VO _bijirersData SusDDR IILTLTU- MUWmWData SusCore frequency =100 h.ilHz Cloci: Freq 二 200 MHz Djta Freq = 400 MHZMfrnnoryCellArray图2, DDR与DDR2工作原理三、DDR2性能优越DDR2内存所带来的性

16、能提升是明显的,在同等核心频率下,DDR2内存实际工作频率是DDR内的两 倍。这得益于DDR2内存拥有两倍于标准DDR内存的4BIT预读取能力。也就是说,虽然DDR2与DDR 一样,都采用了在时钟的上升延和下降延同时进行数据传输的基本方式,但DDR2拥有两倍于DDR的预 读取系统命令数据的能力。在同样100MHz的工作频率下,DDR的实际频率为200MHz,而DDR2则可以 达到400MHz (如图3)。DDRDDR II数据传誉率200/26S/333/400 MHz400/53/667 MHz总线频率100/133/166/200 MHz.200/266/3? MHz内存频率100/132

17、/166/200 MHz100/133/166 MHzc;atch reading size2/4/84/8StrobeSingle DQSDifferential Strobe:DQSeCAS Latency1.5j 2, 2.5M+泌5Write LatencyITRead Latency-1封装TSOPFBGA-U JSL犬水针脾模塑184PIN240PIN图3,DDR与DDR2区别另夕卜,在同等工作频率下的DDR和DDR2内存中,DDR2内存的延时要慢于DDR内存,比如说,DDR200和DDR2-400具有相同的延迟,而DDR2-400具有高一倍的带宽。实际上,DDR2-400和DDR

18、 400具 有相同的带宽,它们的带宽都是3.2GB/S,但是DDR400的核心工作频率是200MHz,而DDR2-400的核心 工作频率是100MHz,也就是说DDR2-400的延迟要高于DDR400。四、功耗更低的DDR2发热量,一直是急切解决的问题,尽管目前的DDR内存并不需要太高的容量,但对于未来DDR2内 存的散热就不可忽视,举例来说,安装4GB内存到插槽中,在峰值调用下内存的发热量将在35-40W之间, 虽然这样容量的内存很少见,但在DDR2平台中,4GB容量已经不是很希奇的事。因此,需要预先解决这 个问题,减少发热量最好就是使用新的内存标准。而且内存的工作频率(往往发热量是和工作频

19、率共同增长 的)将会得到不断的增加,因此我们也需要尽快解决发热量的问题。尽管DDR内存的FBGA封装形式可以很好的工作在200MHz上,当频率更高时,它过长的管脚就会 产生很高的阻抗和寄生电容,这会影响它的稳定性和频率提升的难度。这也就是DDR的核心频率很难突破 275MHZ的原因,而DDR2内存均采用FBGA封装形式(如图4),FBGA封装可以提供了更为良好的电 气性能与散热性,DDR2内存的接口针脚为240pin,而DDR内存的接口针脚为184pin,DDR2内存的电压 从原来DDR的2.5到2.8v降到了 1.8v,从而提供了明显的更小的功耗与更小的发热量,芯片温度和写入 延迟不定性都得

20、到了下降。为DDR2内存的稳定性、超频性以及未来频率的提升提供了有利条件。图4,DDR2的FBGA封装五、DDR2更新的技术在新技术方面,与普通DDR内存不同的是,DDR2内存使用了更新的技术,其中最主要的是OCD(Off-Chip Driver)、ODT (On Die Terminator)和Post CAS。OCD 被称为离线驱动调整(如图 5),DDR2 通过OCD技术可以提高信号的完整性,DDR2通过调整上拉(pull-up) /下拉(pull-down)的电阻值使两 者电压相等,使用OCD通过减少DQ-DQS的倾斜来提高信号的完整性;通过控制电压来提高信号品质。 在I/O Driv

21、er新增稳压线路,令充电、放电动作的电压值的误差减至最少,以防止电压不稳定的时候引起 资料丢失。I Ht:FC -r&fck |mIii. L atV RKK 星 IHiAfter ()?D IrnpedHirHjciJiQfDQMDQ图5, OCD技术工作原理DDR2内存本身集成了 ODT信号终结器(如图6),在并行总线中,信号传输到一端的尽头之后不会 自动消失,而会沿着相反的方向反射回去,这样就会与后面传送过来的信号发生碰撞,导致传输数据出错。 一般情况下,工作频率越高,信号反射的现象就越严重,终结器就是用来解决这个问题的,它可以有效的 吸收末端信号,防止数据的反射。DDR2内存直接将终结

22、器整合在内存芯片中,以内部逻辑的形态存在。 如果多条模组一起工作,系统可以自动控制每一条模组中ODT功能的开启或关闭,这样我们就不必担忧信 号会在第一条模组中就被终结掉,而在后续模组中无法生效的问题。Imiilniil nr FrmiiiTiaLur Oh图6,ODT信号终结器DDR2通过引入Post CAS功能来解决指令冲突问题,Post CAS是为了提高DDR II内存的利用效率而 设定的。Posted CAS是指将CAS (读/写命令)提前几个周期、直接插到RAS信号后面的一个时钟周期(如 图7)。这样CAS命令可以在随后的几个周期内都能保持有效,但读/写操作并没有因此提前,总的延迟时 间也没有改变。由于CAS信号放在了 RAS信号后面一个时钟周期,它的好处在于可以彻底避免信号冲突、 提高内存使用效率。但这种功能的效果只有在读写极其频繁的环境下才能得到体现,若是普通应用,Posted CAS反而会增加读取延迟、令系统性能下降。用户通过调整主板CMOS中的设置,来控制Posted CAS功 能开启或关闭。图7,Post CAS工作原理

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。