单片机IO端口原理

单片机IO端口原理

《单片机IO端口原理》由会员分享,可在线阅读,更多相关《单片机IO端口原理(9页珍藏版)》请在装配图网上搜索。

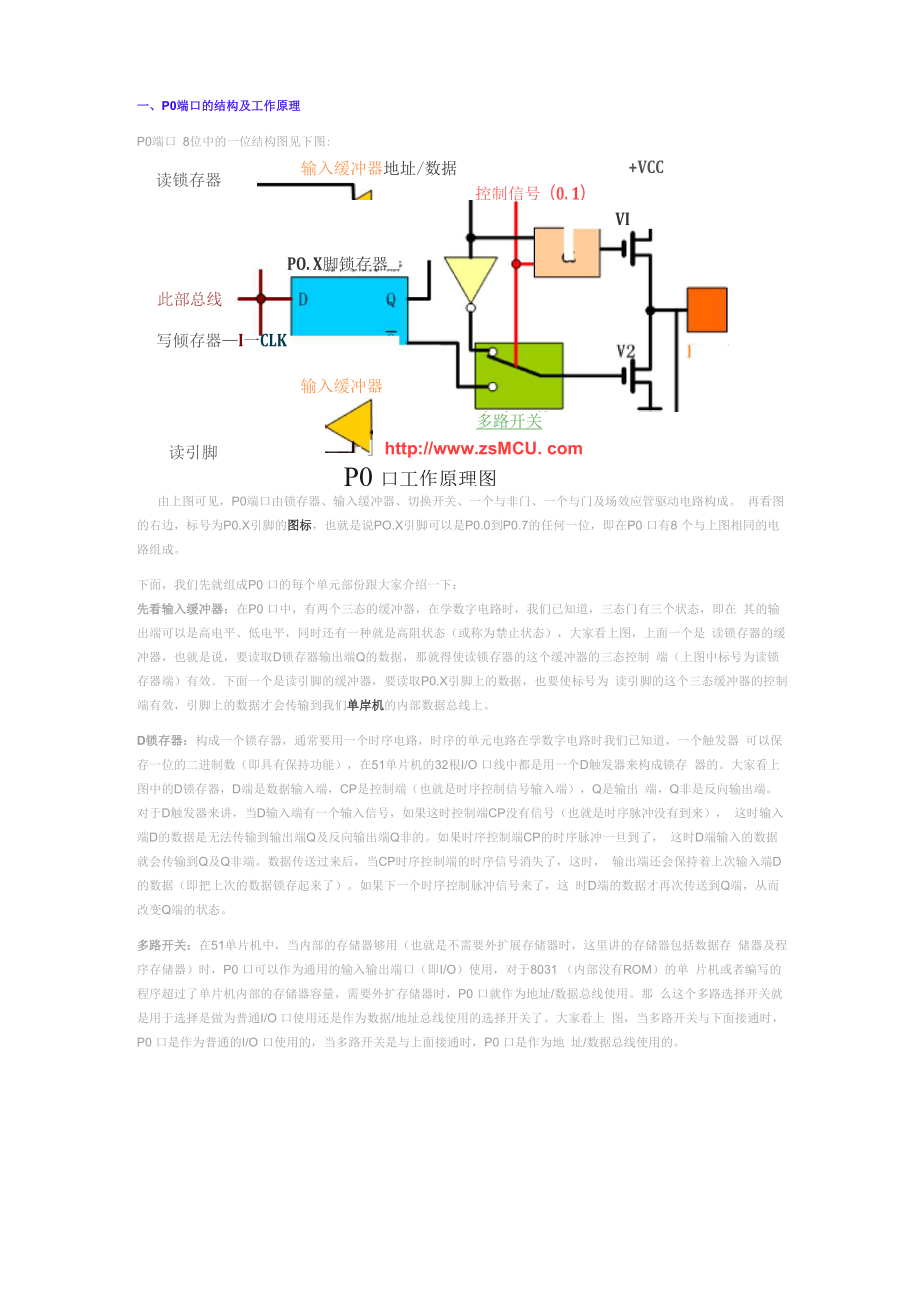

1、一、P0端口的结构及工作原理P0端口 8位中的一位结构图见下图:读锁存器输入缓冲器地址/数据控制信号(0. 1)+VCC此部总线PO. X脚锁存器输入缓冲器VI写倾存器I一CLK读引脚多路开关http:/www.zsMCU. comP0 口工作原理图由上图可见,P0端口由锁存器、输入缓冲器、切换开关、一个与非门、一个与门及场效应管驱动电路构成。 再看图的右边,标号为P0.X引脚的图标,也就是说PO.X引脚可以是P0.0到P0.7的任何一位,即在P0 口有8 个与上图相同的电路组成。下面,我们先就组成P0 口的每个单元部份跟大家介绍一下:先看输入缓冲器:在P0 口中,有两个三态的缓冲器,在学数字

2、电路时,我们已知道,三态门有三个状态,即在 其的输出端可以是高电平、低电平,同时还有一种就是高阻状态(或称为禁止状态),大家看上图,上面一个是 读锁存器的缓冲器,也就是说,要读取D锁存器输出端Q的数据,那就得使读锁存器的这个缓冲器的三态控制 端(上图中标号为读锁存器端)有效。下面一个是读引脚的缓冲器,要读取P0.X引脚上的数据,也要使标号为 读引脚的这个三态缓冲器的控制端有效,引脚上的数据才会传输到我们单岸机的内部数据总线上。D锁存器:构成一个锁存器,通常要用一个时序电路,时序的单元电路在学数字电路时我们已知道,一个触发器 可以保存一位的二进制数(即具有保持功能),在51单片机的32根I/O

3、口线中都是用一个D触发器来构成锁存 器的。大家看上图中的D锁存器,D端是数据输入端,CP是控制端(也就是时序控制信号输入端),Q是输出 端,Q非是反向输出端。对于D触发器来讲,当D输入端有一个输入信号,如果这时控制端CP没有信号(也就是时序脉冲没有到来), 这时输入端D的数据是无法传输到输出端Q及反向输出端Q非的。如果时序控制端CP的时序脉冲一旦到了, 这时D端输入的数据就会传输到Q及Q非端。数据传送过来后,当CP时序控制端的时序信号消失了,这时, 输出端还会保持着上次输入端D的数据(即把上次的数据锁存起来了)。如果下一个时序控制脉冲信号来了,这 时D端的数据才再次传送到Q端,从而改变Q端的状

4、态。多路开关:在51单片机中,当内部的存储器够用(也就是不需要外扩展存储器时,这里讲的存储器包括数据存 储器及程序存储器)时,P0 口可以作为通用的输入输出端口(即I/O)使用,对于8031 (内部没有ROM)的单 片机或者编写的程序超过了单片机内部的存储器容量,需要外扩存储器时,P0 口就作为地址/数据总线使用。那 么这个多路选择开关就是用于选择是做为普通I/O 口使用还是作为数据/地址总线使用的选择开关了。大家看上 图,当多路开关与下面接通时,P0 口是作为普通的I/O 口使用的,当多路开关是与上面接通时,P0 口是作为地 址/数据总线使用的。输出驱动部份:从上图中我们已看出,P0 口的输

5、出是由两个MOS管组成的推拉式结构,也就是说,这两个MOS 管一次只能导通一个,当V1导通时,V2就截止,当V2导通时,V1截止。与门、与非门:这两个单元电路的逻辑原理我们在第四课数字及常用逻辑电路时已做过介绍,不明白的同学请回 到第四节去看看。前面我们已将P0 口的各单元部件进行了一个详细的讲解,下面我们就来研究一下P0 口做为I/O 口及地址/数据 总线使用时的具体工作过程。1、作为I/O端口使用时的工作原理P0 口作为I/O端口使用时,多路开关的控制信号为0 (低电平),看上图中的线线部份,多路开关的控制信 号同时与与门的一个输入端是相接的,我们知道与门的逻辑特点是“全1出1,有0出0”

6、那么控制信号是0的话, 这时与门输出的也是一个0 (低电平),与让的输出是0, V1管就截止,在多路控制开关的控制信号是0 (低电 平)时,多路开关是与锁存器的Q非端相接的(即P0 口作为I/O 口线使用)。P0 口用作I/O 口线,其由数据总线向引脚输出(即输出状态Output)的工作过程:当写锁存器信号CP 有效, 数据总线的信号f锁存器的输入端D锁存器的反向输出Q非端f多路开关V2管的栅极V2的漏极到输 出端P0.X。前面我们已讲了,当多路开关的控制信号为低电平0时,与门输出为低电平,V1管是截止的,所以 作为输出口时,P0是漏极开路输出,类似于OC门,当驱动上接电流负载时,需要外接上拉

7、电阻。下图就是由内部数据总线向P0 口输出数据的流程图(红色箭头)。读锁存器输入缓冲器 地址f数抿控制信号(0. 1) VI写锁存器X脚锁存器输入缓冲器读引脚多路开关http:/www.zsMCU. com&P0 口由内部数据丿电线向引脚输出时的流程图P0 口用作I/O 口线,其由引脚向内部数据总线输入(即输入状态Input)的工作过程:数据输入时(读P0 口)有两种情况1、读引脚读芯片引脚上的数据,读引脚数时,读引脚缓冲器打开(即三态缓冲器的控制端要有效),通过内部数据总线 输入,请看下图(红色简头)。输入缓冲器地址/数据控制信号(0. 1)+VCC内部总线 *1D写锁存器4-CLK输入缓冲

8、器VIT匸读引脚http:/www.zsMCU. comP0 口读引脚时的波程图2、读锁存器通过打开读锁存器三态缓冲器读取锁存器输出端Q的状态,请看下图(红色箭头):读锁存器输入缓冲器地址/数据控制信号(0. 1)+VCCP6 X脚锁存器内部总线 * D写饋存器读引脚VICLK输入緩冲器多路开关PO.xOlHhttp:/www.zsMCU.comP0 口读锁存器时的沫程图在输入状态下,从锁存器和从引脚上读来的信号一般是一致的,但也有例外。例如,当从内部总线输出低电平 后,锁存器Q=0,Q非=1,场效应管T2开通,端口线呈低电平状态。此时无论端口线上外接的信号是低电乎 还是高电平,从引脚读入单片

9、机的信号都是低电平,因而不能正确地读入端口引脚上的信号。又如,当从内部总 线输出高电平后,锁存器Q = 1, Q非=0,场效应管T2截止。如外接引脚信号为低电平,从引脚上读入的信号 就与从锁存器读入的信号不同。为此,8031单片机在对端口 P0 一 P3的输入操作上,有如下约定:为此,8051 单片机在对端口 P0 一 P3的输入操作上,有如下约定:凡属于读-修改-写方式的指令,从锁存器读入信号,其它 指令则从端口引脚线上读入信号。读-修改-写指令的特点是,从端口输入(读)信号,在单片机内加以运算(修改)后,再输出(写)到该端口上。下面是 几条读-修改-写指令的例子。ANL P0,#立即数;P

10、0立即数P0ORL P0,AP0AP0INC P1P1 + P1DEC P3;P3-P3CPL P2P2fP2这样安排的原因在于读-修改-写指令需要得到端口原输出的状态,修改后再输出,读锁存器而不是读引脚,可 以避免因外部电路的原因而使原端口的状态被读错。P0端口是8031单片机的总线口,分时出现数据D7 一 D0、低8位地址A7 一 AO,以及三态,用来接口存储 器、外部电路与外部设备。P0端口是使用最广泛的I/O端口。2、作为地址/数据复用口使用时的工作原理在访问外部存储器时P0 口作为地址/数据复用口使用。这时多路开关控制信号为T,与门解锁,与门输出信号电平由“地址/数据”线信号决定;多

11、路开关与反相器 的输出端相连,地址信号经“地址/数据”线f反相器V2场效应管栅极V2漏极输出。例如:控制信号为1,地址信号为“0”时,与门输出低电平,V1管截止;反相器输出高电平,V2管导通,输出引 脚的地址信号为低电平。请看下图(兰色字体为电平):读锁存器输入缓冲器地址/数据+VCC0控制信号(0、1)1VIT1匸写锁存器读引脚输入缓冲器P0+ X脚锁存器CLK1截止输出为低电平0V2 匸吃导通多路开关 + =http:/www.zsMCU. comP0 口作捋地址线,控制信号为1,地址信号为0时的工作洗程国反之,控制信号为“1”、地址信号为“T, “与门”输出为高电平,V1管导通;反相器输

12、出低电平,V2管截止, 输出引脚的地址信号为高电平。请看下图(兰色字体为电平):输入缓艸-她址/数抿P0- X脚锁存器内部总线T4写锁存器CLK0输入缓冲器+VCC1控制信号(入1)1VI=*多路开关1导通 输出为高电平1http:/www.zsMCU. com读引脚P0口作捋地址线,控制信为1, 地址佶号龙1时的工作洗程图可见,在输出“地址/数据”信息时,VI、V2管是交替导通的,负载能力很强,可以直接与外设存储器相连,无须 增加总线驱动器。P0 口又作为数据总线使用。在访问外部程序存储器时,P0 口输出低8位地址信息后,将变为数据总线,以 便读指令码(输入)。在取指令期间,“控制”信号为“

13、0”,V1管截止,多路开关也跟着转向锁存器反相输出端Q非;CPU自动将OFFH (11111111,即向D锁存器写入一个高电平1)写入P0 口锁存器,使V2管截止,在读引脚信号控制下,通过 读引脚三态门电路将指令码读到内部总线。请看下图读锁存器 内部总线写锁存器读引脚输入缓冲器地址/数掘P0+ X脚锁存器CLK输入缓冲器+VCC1控制信号(0. 1)0VI4斗01截止输出为高电平1P0x引脚P0 口 作为数据#魁线,取指期间工作流程图如果该指令是输出数据,如MOVX DPTR, A (将累加器的内容通过P0 口数据总线传送到外部RAM中), 则多路开关“控制”信号为1, “与门”解锁,与输出地

14、址信号的工作流程类似,数据据由“地址/数据”线反相器 V2场效应管栅极V2漏极输出。如果该指令是输入数据(读外部数据存储器或程序存储器),如MOVX A,DPTR (将外部RAM某一存储单元内容通过P0 口数据总线输入到累加器A中),则输入的数据仍通过读引脚三态缓冲器到内部总线,其过程 类似于上图中的读取指令码流程图。通过以上的分析可以看出,当P0作为地址/数据总线使用时,在读指令码或输入数据前,CPU自动向P0 口 锁存器写入OFFH,破坏了 P0 口原来的状态。因此,不能再作为通用的I/O端口。大家以后在系统设计时务必注 意,即程序中不能再含有以P0 口作为操作数(包含源操作数和目的操作数

15、)的指令。二、P1端口的结构及工作原理P1 口的结构最简单,用途也单一,仅作为数据输入/输出端口使用。输出的信息有锁存,输入有读引脚和读锁 存器之分。pi端口的一位结构见下图.诙锁存器鞘入缓冲器虫部总线写锁存器上拉电阳DCLK引脚谕入缓冲器读引脚sj http : /www. zsmcu. comPg工作原理图由图可见,P1端口与P0端口的主要差别在于,P1端口用内部上拉电阻R代替了 P0端口的场效应管T1, 并且输出的信息仅来自内部总线。由内部总线输出的数据经锁存器反相和场效应管反相后,锁存在端口线上,所 以,P1端口是具有输出锁存的静态口。由上图可见,要正确地从引脚上读入外部信息,必须先使

16、场效应管关断,以便由外部输入的信息确定引脚的状 态。为此,在作引脚读入前,必须先对该端口写入I。具有这种操作特点的输入/输出端口,称为准双向I/O 口。 8051单片机的P1、P2、P3都是准双向口。P0端口由于输出有三态功能,输入前,端口线已处于高阻态,无需 先写入I后再作读操作。P1 口的结构相对简单,前面我们已详细的分析了 P0 口,只要大家认真的分析了 P0 口的工作原理,P1 口我 想大家都有能力去分析,这里我就不多论述了。单片机复位后,各个端口已自动地被写入了 1,此时,可直接作输入操作。如果在应用端口的过程中,已向 P1 一 P3端口线输出过0,则再要输入时,必须先写1后再读引脚

17、,才能得到正确的信息。此外,随输入指令的 不同,H端口也有读锁存器与读引脚之分。三、P2端口的结构及工作原理:P2端口的一位结构见下图:输入缓冲器地址/数据控制信号(0、1)+VCCI上拉电阻P2, X脚锁存器内部总线*D写谶存器CLKQ与门读引脚输入缓冲器多路开关P0.工引脚P2 口工作原理图由图可见,P2端口在片内既有上拉电阻,又有切换开关MUX,所以P2端口在功能上兼有P0端口和P1端 口的特点。这主要表现在输出功能上,当切换开关向下接通时,从内部总线输出的一位数据经反相器和场效应管 反相后,输出在端口引脚线上;当多路开关向上时,输出的一位地址信号也经反相器和场效应管反相后,输出在 端口

18、引脚线上。对于8031单片机必须外接程序存储器才能构成应用电路(或者我们的应用电路扩展了外部存储器),而P2端 口就是用来周期性地输出从外存中取指令的地址(高8位地址),因此,P2端口的多路开关总是在进行切换,分时 地输出从内部总线来的数据和从地址信号线上来的地址。因此P2端口是动态的I/O端口。输出数据虽被锁存, 但不是稳定地出现在端口线上。其实,这里输出的数据往往也是一种地址,只不过是外部RAM的高8位地址。在输入功能方面,P2端口与P0和H端口相同,有读引脚和读锁存器之分,并且P2端口也是准双向口。 可见,P2端口的主要特点包括: 不能输出静态的数据; 自身输出外部程序存储器的高8位地址

19、;执行MOVX指令时,还输出外部RAM的高位地址,故称P2端口为动态地址端口。即然P2 口可以作为I/O 口使用,也可以作为地址总线使用,下面我们就不分析下它的两种工作状态。1、作为I/O端口使用时的工作过程当没有外部程序存储器或虽然有外部数据存储器,但容易不大于256B,即不需要高8位地址时(在这种情况 下,不能通过数据地址寄存器DPTR读写外部数据存储器),P2 口可以I/O 口使用。这时,“控制”信号为“0”, 多路开关转向锁存器同相输出端Q,输出信号经内部总线f锁存器同相输出端Qf反相器f V2管栅极f V2管 9漏极输出。由于V2漏极带有上拉电阻,可以提供一定的上拉电流,负载能力约为

20、8个TTL与非门;作为输出口前,同样 需要向锁存器写入“T,使反相器输出低电平,V2管截止,即引脚悬空时为高电平,防止引脚被钳位在低电平。 读引脚有效后,输入信息经读引脚三态门电路到内部数据总线。2、作为地址总线使用时的工作过程P2 口作为地址总线时,“控制”信号为T,多路开关车向地址线(即向上接通),地址信息经反相器f V2管栅 极漏极输出。由于P2 口输出高8位地址,与P0 口不同,无须分时使用,因此P2 口上的地址信息(程序存 储器上的A15A8)功数据地址寄存器高8位DPH保存时间长,无须锁存。四、P3端口的结构及工作原理P3 口是一个多功能口,它除了可以作为I/O 口外,还具有第二功

21、能,P3端口的一位结构见下图。输入缓冲器第二功能输出+VCCI上拉电阳内部总线写锁存器读引脚CLK与非I、J输入缓冲器P3.X0I 脚I第二功能输入P紡口 工,作原理圉 http : /www. zsMCU. com由上图可见,P3端口和Pl端口的结构相似,区别仅在于P3端口的各端口线有两种功能选择。当处于第一功 能时,第二输出功能线为1此时,内部总线信号经锁存器和场效应管输入/输出,其作用与P1端口作用相同, 也是静态准双向I/O端口。当处于第二功能时,锁存器输出1,通过第二输出功能线输出特定的内含信号,在输 入方面,即可以通过缓冲器读入引脚信号,还可以通过替代输入功能读入片内的特定第二功能

22、信号。由于输出信 号锁存并且有双重功能,故P3端口为静态双功能端口。P3 口的特殊功能(即第二功能):使P3端品各线处于第二功能的条件是:1、串行I/O处于运行状态(RXD,TXD);2、打开了处部中断(INT0,INT1);3、定时器/计数器处于外部计数状态(T0,T1)4、执行读写外部RAM的指令(RD,WR)在应用中,如不设定P3端口各位的第二功能(WR,RD信叼的产生不用设置),则P3端口线自动处于第一功能状 态,也就是静态I/O端口的工作状态。在更多的场合是根据应用的需要,把几条端口线设置为第二功能,而另 外几条端口线处于第一功能运行状态。在这种情况下,不宜对P3端口作字节操作,需采

23、用位操作的形式。端口的负载能力和输入/输出操作:P0端口能驱动8个LSTTL负载。如需增加负载能力,可在P0总线上增加总线驱动器。P1, P2, P3端口各 能驱动4个LSTTL负载。前已述及,由于P0-P3端口已映射成特殊功能寄存器中的P0 一 P3端口寄存器,所以对这些端口寄存器的读 /写就实现了信息从相应端口的输入/输出。例如:MOV A, P1 ;把Pl端口线上的信息输入到AMoV P1, A ;把A的内容由P1端口输出MOV P3, #0FFH ;使P3端口线各位置丨在这节课我们已将51单片机的4个8位的并行口跟大家一起来分析了一下,在后面的章节中我们将还会与外 设一起来与大家学习。

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。