EDA 电子琴课程设计

EDA 电子琴课程设计

《EDA 电子琴课程设计》由会员分享,可在线阅读,更多相关《EDA 电子琴课程设计(17页珍藏版)》请在装配图网上搜索。

1、的简单电子琴电路的设计1.1 课程设计目的本课程设计主要是基于VHDL文本输入法设计乐曲演奏电路,该系统基于计算机中时 钟分频器的原理,采用自顶向下的设计方法来实现,通过按键输入来控制音响或者自动演 奏已存入的歌曲。系统由乐曲自动演奏模块、音调发生模块和数控分频模块三个部分组成。 系统实现是用硬件描述语言 VHDL 按模块化方式进行设计,然后进行编程、时序仿真、电 路功能验证,奏出美妙的乐曲(当然由于条件限制,暂不进行功能验证,只进行编程和时 序仿真)。该设计最重要的一点就是通过按键控制不同的音调发生,每一个音调对应不同 的频率,从而输出对应频率的声音。1.2 课程设计内容(1)设计一个简易的

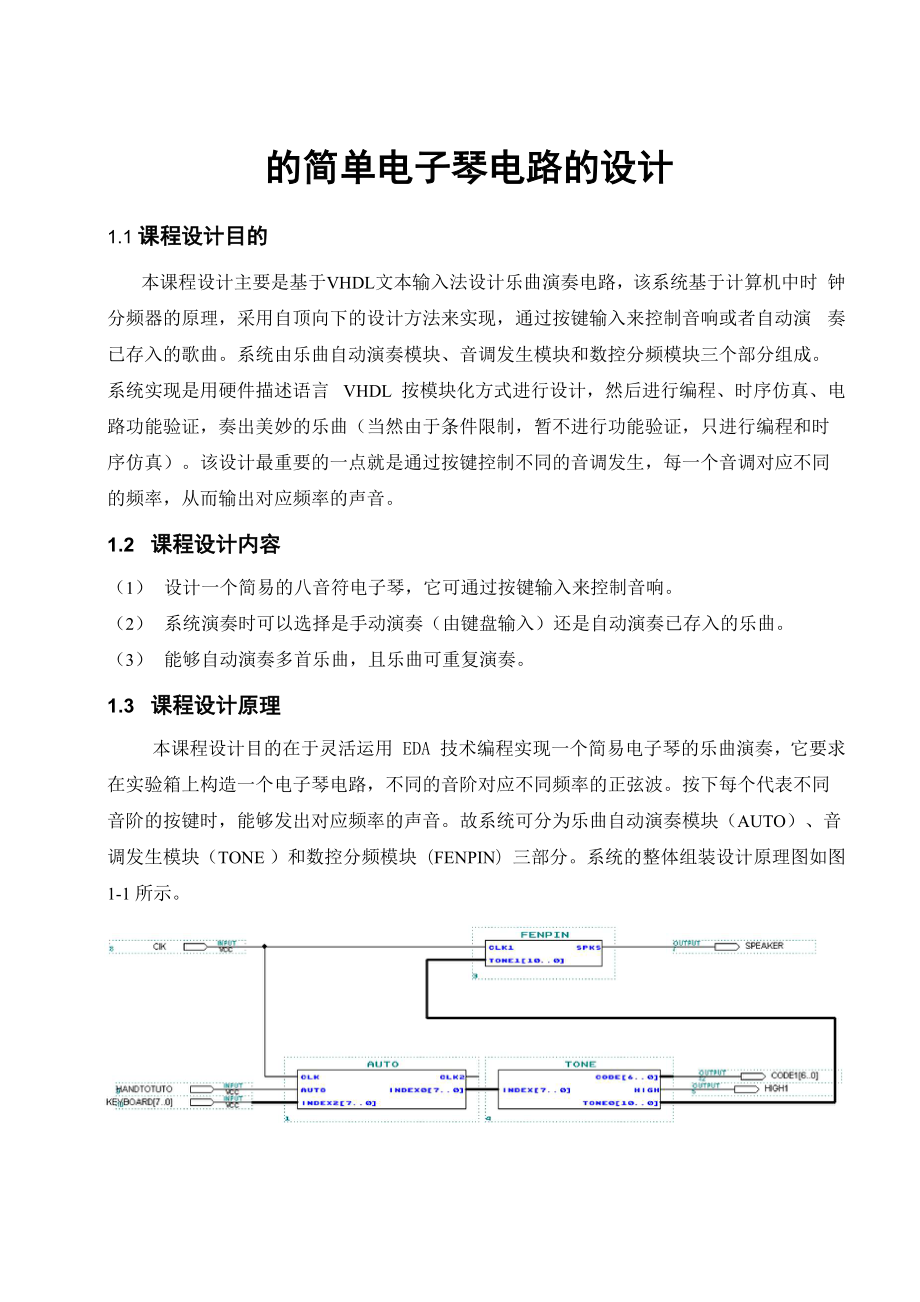

2、八音符电子琴,它可通过按键输入来控制音响。(2)系统演奏时可以选择是手动演奏(由键盘输入)还是自动演奏已存入的乐曲。(3)能够自动演奏多首乐曲,且乐曲可重复演奏。1.3 课程设计原理本课程设计目的在于灵活运用 EDA 技术编程实现一个简易电子琴的乐曲演奏,它要求 在实验箱上构造一个电子琴电路,不同的音阶对应不同频率的正弦波。按下每个代表不同 音阶的按键时,能够发出对应频率的声音。故系统可分为乐曲自动演奏模块(AUTO)、音 调发生模块(TONE )和数控分频模块(FENPIN)三部分。系统的整体组装设计原理图如图 1-1 所示。图1-1系统的整体组装设计原理图由于设计分模块组成,每个单独的模块

3、都是一个完整的源程序,分别实现不同性质的 功能,但是每个模块又是紧密关联的,前一个模块的输出很可能是后一模块的输入。如 AUTO模块的音符信号输出就是TONE模块的音符信号输入。另外,时钟脉冲信号在本课 程设计中用的最多,用处也最大,一般情况下时钟信号处上升沿有效,判断和控制各个计 数器计数多少。2 简易电子琴的设计过程根据系统设计要求,系统该系统基于计算机中时钟分频器的原理,设计采用自顶向下 的设计方法,通过按键输入来控制音响或者自动演奏已存入的歌曲。它由乐曲自动演奏模 块、音调发生模块和数控分频模块三部分组成。2.1 乐曲自动演奏模块乐曲自动演奏模块的作用是产生 8位发生控制输入信号。当进

4、行自动演奏时,由存储 在此模块的 8 位二进制数作为发声控制输入,从而自动演奏乐曲。该模块的VHDL源程序主要由3个工作进程组成,分别为PULSEO, MUSIC和COM1。PULSE0的作用是根据键盘输入(自动演奏)的值(0或1)来判断计数器COUNT以及脉 冲 CLK2 的输出值。部分源程序如下:PULSE0:PROCESS(CLK,AUTO)-工作进程开始VARIABLE COUNT:INTEGER RANGE 0 TO 8;-定义计数器变量,值从 0到 8IF AUTO=1THEN-键盘输入为 1COUNT:=0;CLK2INDEX0INDEX0=00010000; -5该模块最主要的

5、用途就是将输入二进制数转化为发声控制输入,是产生音符的重要步骤,AUTO模块的源程序符号编辑图如图3-1。AUTO:CLKCLK2AUTO1HDEXO7-O1HDEX27-O3图3-1 AUTO模块的符号编辑图2.1.1 乐曲演奏模块文本程序:-程序名称:AUTO.VHD -程序功能:采用VHDL语言编程产生8位发声控制输入信号。-电子班 张目(12007243818)-LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY AUTO

6、 ISPORT(CLK: IN STD_LOGIC; AUTO: IN STD_LOGIC; CLK2: BUFFER STD_LOGIC;-系统时钟信号-键盘输入/自动演奏-时钟输出INDEX2: IN STD_LOGIC_VECTOR(7 DOWNTO 0);-键盘输入信号INDEX0: OUT STD_LOGIC_VECTOR(7 DOWNTO 0); -音符信号输出END AUTO;ARCHITECTURE BEHAVIORAL OF AUTO ISSIGNAL COUNT0:INTEGER RANGE 0 TO 31; -定义信号计数器,有 32个信号元素 BEGINPULSE0:P

7、ROCESS(CLK,AUTO)-PULSE0 工作进程开始VARIABLE COUNT:INTEGER RANGE 0 TO 8;-定义变量计数器,从 0到8BEGINIF AUTO=1THEN-键盘输入为 1COUNT:=0;CLK2=0;-计数器值为 0,时钟信号 2幅值为 0ELSIF(CLKEVENT AND CLK=1)THEN-输入的时钟信号为其他值COUNT:=COUNT+1;-计数器加 1即为 1IF COUNT=4 THENCLK2=1;ELSIF COUNT=8 THENCLK2=0;COUNT:=0;END IF;END IF;-MUSIC 工作进程开始END PROC

8、ESS;MUSIC:PROCESS(CLK2)BEGINIF(CLK2EVENT AND CLK2=1)THENIF(COUNT0=31)THENCOUNT0=0;-时钟信号 2为 1-计数器值为 31-计数器清 0ELSECOUNT0INDEX0INDEX0INDEX0INDEX0INDEX0INDEX0INDEX0INDEX0INDEX0INDEX0INDEX0INDEX0INDEX0INDEX0INDEX0INDEX0INDEX0INDEX0INDEX0INDEX0INDEX0INDEX0INDEX0INDEX0INDEX0INDEX0INDEX0INDEX0INDEX0INDEX0IN

9、DEX0INDEX0NULL;END CASE;ELSE INDEX0TONE0=912;CODE=0010010;HIGHTONE0=1372;CODE=0001111;HIGHTONE0=2047;CODE=0000001;HIGHTONE0=773;CODE=1001111;HIGHTONE0=912;CODE=0010010;HIGHTONE0=1036;CODE=0000110;HIGHTONE0=1116;CODE=1001100;HIGHTONE0=1197;CODE=0100100;HIGHTONE0=1290;CODE=0100000;HIGHTONE0=1372;CODE=

10、0001111;HIGHTONE0=1410;CODE=0000000;HIGHTONE0=2047;CODE=0000001;HIGH=0;END CASE;END PROCESS;END ART;2.3数控分频模块数控分频模块是对时基脉冲进行分频,得到与0、1、2、3、4、5、6、7八个音符相对应的频率。FENPIN模块的源程序符号编辑图如图3-3。FENPINCLK 1SPKS TOHEZ1 1O_ - O33 FENPIN模块符号编辑图该模块主要由4个工作进程组成。首先,根据系统时钟信号的输入得到时基脉冲以及 计数器的值,而时钟信号在AUTO模块中便已给出,两者之间的设置关系类似于AU

11、TO 模块中第一个工作进程的设置。第二个PROCESS是此模块的核心,即由时基脉冲值转化 为音符的频率。部分源程序如下:VARIABLE COUNT11:INTEGER RANGE 0 TO 2047;-时基脉冲为1时定义频率计数器,从0到2047HzIF(PRECLKEVENT AND PRECLK=1)THENIF COUNT11TONE1 THEN-频率计数器小于音符分频系数COUNT11:=COUNT11+1;FULLSPKS=1; - 计数加 1,扬声器音频为 1ELSECOUNT11:=0;FULLSPKS=0;最后一个PROCESS则是用来设置扬声器输出信号的,扬声器信号由0和1

12、控制,当 且仅当前一个 PROCESS 中的 FULLSPKS 输出为 1 时,扬声器才有输出,再根据计数器取 值来确定输出是1还是0。部分源程序如下:IF(FULLSPKSEVENT AND FULLSPKS=1)THEN-扬声器音频信号为 1COUNT2:=NOT COUNT2;IF COUNT2=1THENSPKS=1;-扬声器输出为 1ELSE SPK=0;.2.3.1 数控分频模块文本程序:-电子班 张目(12007243818)-LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEE

13、E.STD_LOGIC_UNSIGNED.ALL;ENTITY FENPIN ISPORT(CLK1: IN STD_LOGIC;-系统时钟信号TONE1: IN INTEGER RANGE 0 TO 2047; -音符分频系?SPKS: OUT STD_LOGIC);-驱动扬声器的音频信?END ENTITY FENPIN;ARCHITECTURE ART OF FENPIN ISSIGNAL PRECLK:STD_LOGIC;-定义时基脉冲信号SIGNAL FULLSPKS:STD_LOGIC;BEGINPROCESS(CLK1)VARIABLE COUNT:INTEGER RANGE 0

14、 TO 8:=0;-定义变量计数器,从 0到8BEGINIF(CLK1EVENT AND CLK1=1)THEN-据时钟信号为 1时COUNT:=COUNT+1;-判断计数器取值为 1IF COUNT=2 THENPRECLK=1;ELSIF COUNT=4 THEN-若计数器计 4PRECLK=0;COUNT:=0; -时基脉冲为 0,计数器清零ELSEEND IF;END IF;END PROCESS;PROCESS(PRECLK,TONE1)VARIABLE COUNT11:INTEGER RANGE 0 TO 2047; -定义变量频率计数器 11,从 0到 2047HzBEGINIF

15、(PRECLKEVENT AND PRECLK=T)THEN-PRECLK 脉冲上升沿触发IF COUNT11TONE1 THEN-若计数器 11值小于音符信号1COUNT11:=COUNT11+1;FULLSPKS=1;-计数器加 1,音频信号为 1ELSECOUNT11:=0;FULLSPKS=0;END IF;END IF;END PROCESS;PROCESS(FULLSPKS)-音频信号输出进程开始 -VARIABLE count2:integer range 0 to 1 :=0;-定义变量计数器 2,初值为 0-BEGINIF (FULLSPKSEVENT AND FULLSPK

16、S=1) THENif count2=1 then count2:= 0;elsecount2:=1;end if;IF COUNT2=1 THENSPKS=1;ELSESPKSCLK32MHZ,INDEX2=INDEX1,INDEX0=INDX,AUTO=HANDTOAUTO);-调用自动演奏模块U1:TONE PORTMAP(INDEX=INDX,TONE0=TONE2,CODE=CODE1,HIGH=HIGH1); -调 用音调 发 生模块U2:FENPIN PORT MAP(CLK1=CLK32MHZ,TONE1=TONE2,SPKS=SPKOUT); END ART;-调用数控分频模

17、块3 系统仿真系统仿真是在实际系统上进行实验研究比较困难时适用的必不可少的工具,它是指通 过系统模型实验去研究一个已经存在或正在设计的系统的过程,通俗地讲,就是进行模型 实验。因而,系统仿真的结果决定整个课程设计任务完成的到位程度。3.1 时序仿真编译完成后,可以对所进行的设计进行仿真,下面介绍一下仿真的步骤。(1)在file下拉菜单中选择new,再在其弹出的对话框中点选,也做E迎.总,点击 OK确定,则进入了文本编辑器,在编辑区输入程序,然后保存为.vhd文件(注意保存时 实体名要与文件名一致,否则编译时会出错);接下来在file下来菜单选择project,在其下 拉菜单中选 迢毗吋讥问汨1

18、已Ctrl+5hiFt+J ,建立工程文件。第三步,在菜单栏里选择Assign,在其下拉菜单中选device,最后选择Device Familv:FLEX10K,再选HHESEH唾,确定即可;第四步,在菜单栏中点击MAX+plusII再用下拉菜单中选compiler进行编译。(2) 打开波形编辑器,在Node菜单中选择Enter Nodes from SNF项,列出所有的信 号,选择所需要的信号,然后画出输入信号的波形,最后将该文件以.scf的扩展名 存盘。(3) 在MAX+plusII菜单中打开仿真器窗口,单击Start按钮,当仿真器结束工作时, 单击 Open SCF 按钮,就可以看到仿真

19、的结果。本课程设计的仿真平台是MAX+plusl,通过对VHDL源程序进行编译检错,然后创建 波形文件(后缀名为.scf),加入输入输出变量,选择适用的芯片(EPF10K10LC84-3)以及 设定仿真结束时间(100us),设置好输入初值进行仿真,得到仿真波形图。由于电子琴4个模块都是独立的程序,可分别对各个程序仿真,验证输入输出的正确性,但在最终能演 奏出乐曲的则是顶层设计模块。3.1.1乐曲自动演奏模块的仿真如图 3-1所示。图 3-1 乐曲自动演奏模块的仿真图该图输入系统时钟信号 CLK 初值设为 0,自动演奏 AUTO 设为 1,键盘输入信号 INDEX2为00, INDEX0为音符

20、信号输出,是8位的二进制代码它根据COUNTO的值改变 而改变。3.1.2音调发生模块的仿真如图3-2所示。图 3-2 音调发生模块的仿真图该图输入音符信号INDEX初值为00,输出是音符显示信号CODE为01,高低音显示信号为 0,音符的分频系数为 11111111即 2047Hz。Name:E-CLK13.1.3 数控分频模块的仿真如图 3-3 所示。Time: 34ieInterval:3ieSPKSSTONEI抄 COUNT酬 C0UNT11图 3-3 数控分频模块的仿真图该图输入系统时钟信号CLK1初值为0 (各输出值都是在时钟信号的下降沿有效),音符分频系数TONE1为001000

21、00即1290Hz,驱动扬声器的音频信号SPKS输出为1。3.1.4简易电子琴整个系统的仿真如图3-4 所示。Ref: O.iJns|+| + | Time: |725.0nsO.OnsrIlJU.lJris 200.0ns 300.| IntervalIns 400.0nsi|725.0ns|500.Uns 600.IJns 700JJns 800.0ns 900.Uns1,0us1.11js1.2usiiiiiiii1.3 usi1.4 usi1.5 usi1.6usi17usi1.EName:valueE- ANDTOAUTO1rIrIr11E- CLK32MHZIJ1rIrIr11P

22、SPKOUT01P HIGH11u1r1IIi1II1CODE1HOGIJB肚01册06 漱 01$ CEJ. 06X 0106 I01!01黑1INDEX1H00IJIJX 0102 I03 :04J 0506(”08 109 :0AX阳(oc X0D :(OE OF(10 11to:U0|INDEX2H0000X 0102 X03 :04X 0506(Ros J!09 :0AX 08oc X0D :(0E %OF10 11dF o:ULI|COUNTLIH00on抄 to:UlJ|COUNTH IJ0u 0X0K0JoT0t-nr刖 pin:U2|COUN7HIJuX1X2X3X1X2X3

23、XX:U2|C0UNT11H000000urn002图 3-4 简易电子琴整个系统的仿真图该图输入系统时钟信号CLK32MHZ初值为0,自动演奏信号HANDTOAUTO初值为 0,键盘输入信号 INDEX1 为 00000000;输出音符信号 CODE1 则为 0110000,高低音节信 号HIGH1变为1,即高音,音频信号SPKOUT即输出0,输出为1时CODE1变为0110100, 这时出现10ns的延时。在仿真时由于系统各方面原因影响,出现延时属于正常现象。3.2原理图综合时序仿真步骤:1、在 file 下拉菜单里面选择 new, 再在其弹出的对话框中点选烛EEE亟亟M ”,即可进入原理

24、图编辑界面,右击鼠标选择(enter symbol.)然后左键分别双击对话框中Symbol File栏中的AUTO、FENPIN和TONE则会调入相应模块 的原理图,然后按照电子琴设计要求将各个模块连接起来,组成完整的电子琴演奏系统, 如图 3-5 所示。3-5 系统的整体组装设计原理图将绘制好的原理图保存,确保无误后运行进行仿真。2、时序仿真:(1)建立波形文件。(2)输入信号近点。(3)设置波形参数。(4)设置仿真时间宽度。(5)加上输入信号。(6)波形文件存盘。(7)运行仿真器。(8)观察分析波形。之后得到的仿真时序图如图3-6所示。Ref: 10.0戊;| |*M Time: Q.CI

25、ns| Interval: |0.0ns|Name:厂Value:rZl100.0ns200.0ns300.0ns400.0ns500. Ons600.0ns700.0ns800.0ns900.0 ns1 .Ous1/lus1.2us1.3us1 4us1,5us1 .Bus17us1.8us1ANDTOAUTO0rCLK32MHZ0IIIjIIIP SPKOUT0IQ HIGH11IIIIIIIIIIIIIL悲 CODE1H IJEi06I.066M 0106I606A 01INDEX1H IJIJ00 :01X020340506k08)l09XA IOBJ octo:U0|INDE:2H

26、IJIJ00 ;:;01020304Ji0506J! w08)l09K0A I0EIy. ocF o:UO|COUNTOH 0000刖 to:UO|COUNTHO0r0r0r0DC0r0r0酬 pin:U2|COUN7HO0123DC01*2F : U2|COUNT11H000000001002图 3-6 系统原理图仿真时序图3.3 问题分析在此次课程理论设计中,不可避免地遇到许多棘手的问题,一是对 EDA 技术的不太了解,二是对理论知识的学习不够扎实,初涉VHDL语言以致很多语法和语言基本结构、算法生疏,运用不灵活。因此,在编写源程序上遇到极大的难题,而且在编译运行程序时 对出错的语句理解不

27、到位,导致难于下手修正错误语句、语法,这使得在设计程序时遇到 更大的很大的麻烦。还有就是 VHDL 语言的数据类型和语法结构都很容易造成混淆,比如 IN STD_LOGIC_VECTOR(7 DOWNTO 0)语句,它有时既可以认为是从 7下降到0,也可 认为是从 0 上升到 7,当输入有多位时,这就容易造成在读懂仿真波形图时读位数倒置, 使仿真现象与理论结果相出入。在分频模块程序设计时遇到了编译不出来,图形错误等编译时总是出现非法的错误, 经过老师修改和指正,最后终于编译成功,完成了该系统的文本设计。4 设计小结通过这本的 HDL 课程设计,既锻炼了我的动手能力,也让我加深了对课堂上所学到

28、的理论知识的理解,这给我提供了一个在学习生活中很难得的理论联系实际的机会 ,让了 深刻体验到在对于设计时遇到的不同问题时,首先应该理解问题关键所在,因为用语言编 写程序需要仔细认真的态度,一点点错误漏洞将导致整个源程序无法编译运行,阻碍下一 步工作完成进度。还有我也发现了在平时学习过程中难于发现的许多缺点不足。比如实践的机会过少, 所学的理论知识不能够灵活运用,因此在遇到实际的问题时无法正确处理;再者在课堂上 获得的专业知识过于浅显,很多的有关基本操作原理、操作方法都理解不了;课外知识了 解的也过少,导致在课程设计初期,面对完全陌生的设计课题无从下手,不知所措。这就 提醒我在注重学好理论的同时

29、,更要加强动手的能力,不要一味的照搬课本上的知识,要 创新,才能在当今竞争激烈的社会中立足,记住,命运掌握在自己手里,一切都只能靠我 们自己。学 院:物电学院班 级: 07 级电子一班 指导老师:马玉韬姓 名:张目学 号: 12007243818目录1 课程设计1.1 课程设计目的 11.2 课程设计内容11.3 课程设计原理12 简易电子琴的设计过程2.1 乐曲自动演奏模块22.1.1乐曲演奏模块文本程序32.2 音调发生模块42.2.1 音调发生模块文本程序 52.3 数控分频模块6 .2.3.1 数控分频模块文本程序 72.4 顶层设计82.4.1 顶层模块文本程序 93 系统仿真3.1 时序仿真103.1.1乐曲自动演奏模块的仿真113.1.2音调发生模块的仿真113.1.3数控分频模块的仿真113.1.4简易电子琴整个系统的仿真113.2原理图综合时序仿真123.3 问题分析134 设计小结 14

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。