实验二60秒倒计时电路设计的实验报告

实验二60秒倒计时电路设计的实验报告

《实验二60秒倒计时电路设计的实验报告》由会员分享,可在线阅读,更多相关《实验二60秒倒计时电路设计的实验报告(3页珍藏版)》请在装配图网上搜索。

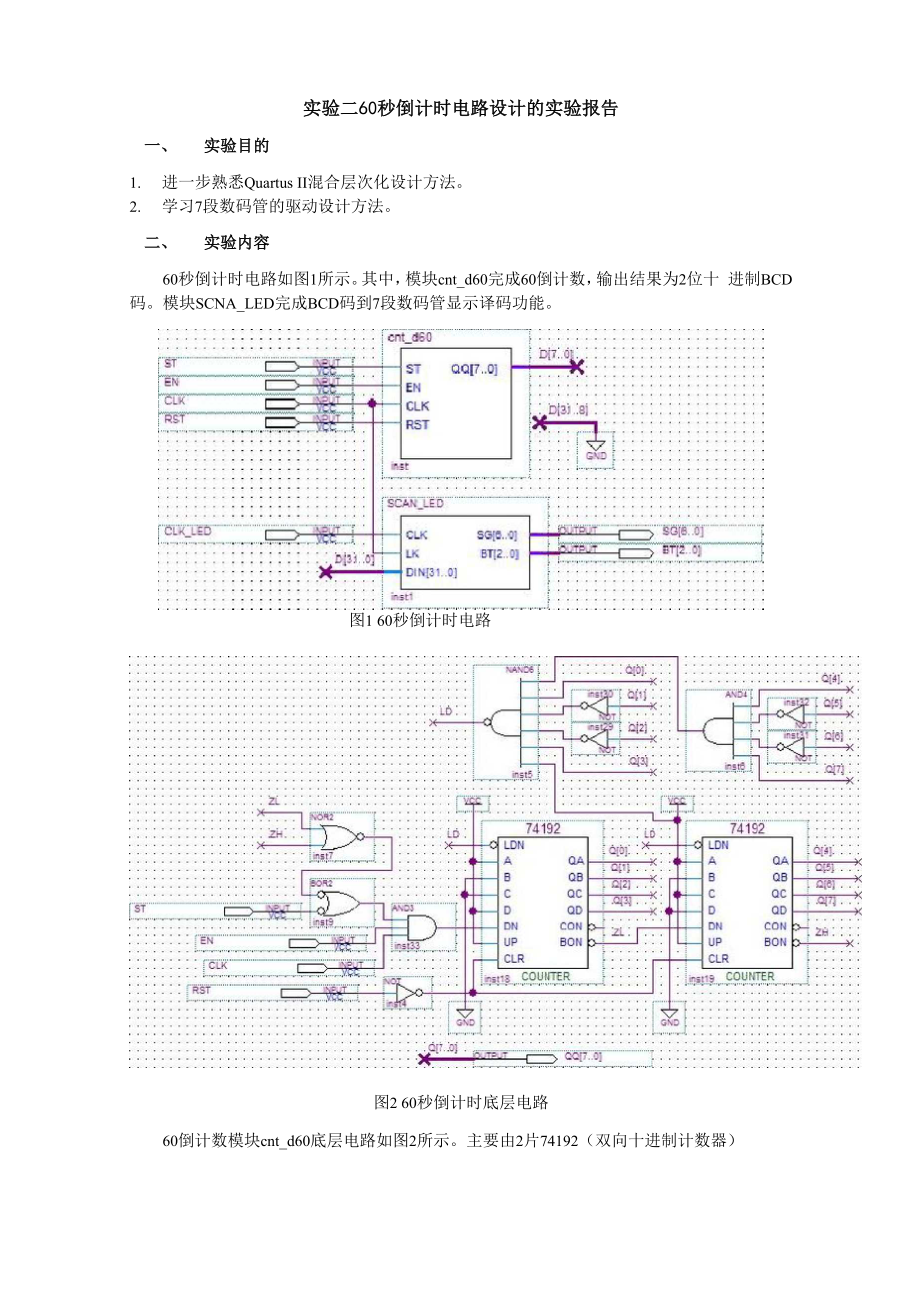

1、实验二60秒倒计时电路设计的实验报告一、实验目的1. 进一步熟悉Quartus II混合层次化设计方法。2. 学习7段数码管的驱动设计方法。二、实验内容60秒倒计时电路如图1所示。其中,模块cnt_d60完成60倒计数,输出结果为2位十 进制BCD码。模块SCNA_LED完成BCD码到7段数码管显示译码功能。图1 60秒倒计时电路图2 60秒倒计时底层电路60倒计数模块cnt_d60底层电路如图2所示。主要由2片74192(双向十进制计数器)构成。模块cnt_d60和SCNA_LED的源设计文档(cnt_d60.bdf和SCAN_LED.vhd)提供给大 家。要求大家建立新工程,为模块cnt_

2、d60和SCNA_LED新建封装(*.bsf),并根据图1完 成顶层60秒倒计时电路设计。完成以上程序设计,编译时器件选择Cyclone系列的EP1C12Q240C8。引脚锁定参考表 1内容。注意:应把未分配管脚置为三态输入,切记!表1实验连线信号引脚号实验箱上连线信号引脚号实验箱上连线信号引脚号实验箱上连线CLK_LEDPIN_285KHzBT2PIN_126SEL2SG4PIN_6数码管e段CLKPIN_23ADJ_CLK (1Hz)SG0PIN_2数码管a段SG5PIN_7数码管f段ENPIN_15按键输入K1SG1PIN_3数码管b段SG6PIN_8数码管g段BT0PIN_124SEL

3、0SG2PIN_4数码管c段RSTPIN_16按键输入K2BT1PIN_125SEL1SG3PIN_5数码管d段STPIN_17按键输入K3三.实验步骤1.原理图设计输入(1)首先将模块cnt_d60和SCNA_LED的源文件放在等一下需要建立的文件中,打开 QuartusII 软件。(2)选择路径。选择File/New Project Wizard。添写后以后,单击“NEXT”进入下一步。(3)添加设计文件,在File name中选择路径然后添加模块cnt_d60和SCNA_LED的源 文件,点击“ Next”。(4)选择 FPGA 器件。Family 选择 Cyclone,先在 Packg

4、e 选择 Any QFP, Pin Count 选 择 240, Speed grade 选择 8;然后在 Available device 中选择 EP1C12Q240C8,点击“Next”。(5)选择外部综合器、仿真器和时序分析器。设置好后,单击“ NEXT ”进入下一步。(6)结束设置。“工程设置统计”窗口,列出了工程的相关设置情况。最后单击“Finish”, 结束工程设置。(7)建立原理图文件。点击 cnt_d60 文件,然后点击 File/Crete/Update/Create Symbol Files For Current file以新建原理图封装文件方式,然后以同样的方式创建原

5、理图 SCNA_LED封装文件,文件格式都为*bdf。保存原理图文件。选择File/Save As.菜 单,存为testone文件,选择Edit/Insert Symbol.(或直接双击原理图空白处)打开 元器件库窗口,选择合理的器件(封装好的cnt_d60文件和SCNA_LED文件都在里 面)按图1完成60秒倒计时电路原理图设计,完成后选择File/Save.保存原理图。(8)综合编译。编译之前,打开原理图文件,选择Project/Set as Top-Level Ent以确保当前编译的文件为顶层的实体文件。然后选择Processing/Start Compilation,进行 综合分析,直

6、至编译通过为止。(9)保护设计中没有使用到的引脚。对于 FPGA 芯片(包括 EP1C12Q240C8),在做 Quartus II工程时必须将未分配的管脚置为三态输入。选择 AssignmentsDevice. 打开工程设置窗口。在Category中选择Device项,然后在Available Devices栏中, 诜中EP1C12Q240器件,再单击Device & Pin Options按钮,在弹出窗口(中选 择 Unused Pins 栏,然后设置 Reserve all unused pins 为 AS input tri-stated。推荐 把未分配管脚置为三态输入。如未将未分配管

7、脚置为三态输入,将可能导致主芯片 或外围芯片损坏,切记!(10)添加管脚信息(主要是分配引脚号)。当综合完成后,网表信息才会生成。选择 Assignments/Pin Planner 菜单,打开 Pin Planner 窗口。下方表格 Node Name 栏中列 出了设计中所有引脚名,在Location栏中双击输入引脚号。完成后关闭Pin Planner 窗口。(11)再次选择Processing/Start Compilation,进行全局编译综合,使引脚三态保护和引脚 号分配设置生效。编译成功后,生成最终的下载文件JTAG下载方式的*.sof和AS 下载方式的*.pof文件)。注意,在Co

8、mpilation Report窗口中选择Fitter栏下的 Device Options 项,观察 Reserve all unused pins 属性是否成功配置成了 As input tri-stated (三态输入)。如果没有,必须重新完成第(11)步,再全局综合编译。(12)建立仿真文件。在下载之前在QuartusII软件环境下进行设计的功能仿真。选择 File/New.。选择Vector Waveform File文件类型,建立仿真文件。(13)选择仿真节点信号。选择 View/Utility Windows/Node Finder,弹出 Node Finder 窗口, 单击Lis

9、t按钮)。将需要观察的节点直接用鼠标左键拖放至仿真文件的Name栏中。(14)设置仿真输入波形。选择Edit/End Time.设置仿真时长为10us,选择Edit/Grid Size. 设置最小仿真步长为1us。对输入信号的波形设置,利用窗口左侧的快速工具栏来 完成。最后存盘仿真文件(如EXAM),其扩展名为*.vwf。(15)设置仿真类型为时序仿真。选择Assignment/Settings.,弹出的窗口中在Category 栏中选择Simulator Settings项,然后选择Simulation mode (仿真类型)为Timing (时 序仿真),选择Simulation inpu

10、t (仿真输入文件)为EXAM.vwf)。完成,单击OK。(16)观察仿真结果。选择Processing/Start Simulation开始仿真。本例仿真结果如图2-1-20 所示,由于仿真类型为时序仿真,所以能够观察到由于器件延时所带来的毛刺现象。 如果仿真结果不正确,说明此前的程序可能存在功能上的设计错误,必须修改源程 序以使仿真结果正确为止。(17)下载前的硬件连线。下载可以选择JTAG方式和AS方式。为了方便调试,选用JTAG 下载方式,对于FPGA器件,这种下载方式的配置信息会掉电丢失。下载之前必须 先完成硬件测试的连线(不要带电操作),按照表1实验连线中的各个接口连线。(18)下

11、载。选择Tools/Programmer,弹出窗口 Mode栏选择JTAG下载方式。一般情况下, 系统会自动添加一个SOF下载配置文件。若没有,则选择Add File,添加*.sof文件(AS下载方式,添加*.pof文件),。同时,选中Program/Configure复选框,点击“Start” 后开始下载。下载成功后,进行硬件功能的测试。四. 实验现象及效果分析8个数码管全亮,同时最后两个数码管从59开始倒计时,当倒计时为00时,按键k3 可以对其置位为59;按键k2可以将其复位为00。由于接线问题使实验效果并不是很理想,数码管经常没有显示。五. 实验拓展1. 分析模块cnt_d60的工作原理,说明各引脚的功能。2. 如果要设计24秒倒计时电路,将如何操作?1. 解:该模块最主要的部分是由两片74192芯片构成,其主要工作原理如下:(1) 第一片的借位输出BON连接到第二片的减计数时钟输入端。网 同时加 计数时钟输入UP接高电平。(2)74192有四个输入D, C, B, A,其中D为最高位。把把第一片的四位依次 置为1,0,0,1,第二片依次置为0,1,0,1,则模值为60的倒计时计数器完成,从 59开始倒计时。2.

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。