外文翻译-D触发器

外文翻译-D触发器

《外文翻译-D触发器》由会员分享,可在线阅读,更多相关《外文翻译-D触发器(9页珍藏版)》请在装配图网上搜索。

1、低功耗高效的D触发器电路摘要本文列举了低功耗高速率D触发器的设计。它提出了各种技术,以尽量减少次临 界漏电功率与CMOS电路的功耗。本文提出的D触发器的一种设计以提高系统的 整体速率,与其他电路相比。这种技术可以让电路来实现最低功耗和最小的晶体 管数量。1.引言品体管特征尺寸的缩放技术已经提供了一个在过去三十年中硅行业的显著的 创新方法。设计师们正努力使硅面积更小,更高速率,低功耗和可靠性,由于便 携式电子产品的需求不断增加和普及。动态功耗是数字系统的功耗主要因素之 一。为了减少动态功耗,已经取得了更小的几何尺寸,结果影响了静态功耗。动 态功耗与电源电压的平方成正比,因此显著降低电压以降低能耗

2、。器件尺寸的连 续缩放,导致今天的超大规模集成电路的阈值电压显着增加,亚阈值漏电流成倍 增长。这大大增加了整体的总功耗。在最近的纳米CMOS技术,如90-、45-nm,漏 电流是几乎占了一半的总功耗这是并不少见。在90nm节点,漏功率可高达35% 的芯片功率。由于便携式设备的使用和无线系统日益增强,减少这种功耗是非常 必要的。这些设备比单一的超大规模集成电路芯片的复杂得多。他们有几个组 成部分,可能是数字的或非数字的。延长电池寿命为嵌入式应用,是在系统级 完成的。高功耗减少了电池使用寿命。因此,电源最优化技术 应适用于不同 层次的数字化设计。这些技术之一是使用低功耗的逻辑模式,这应该运用在逻辑

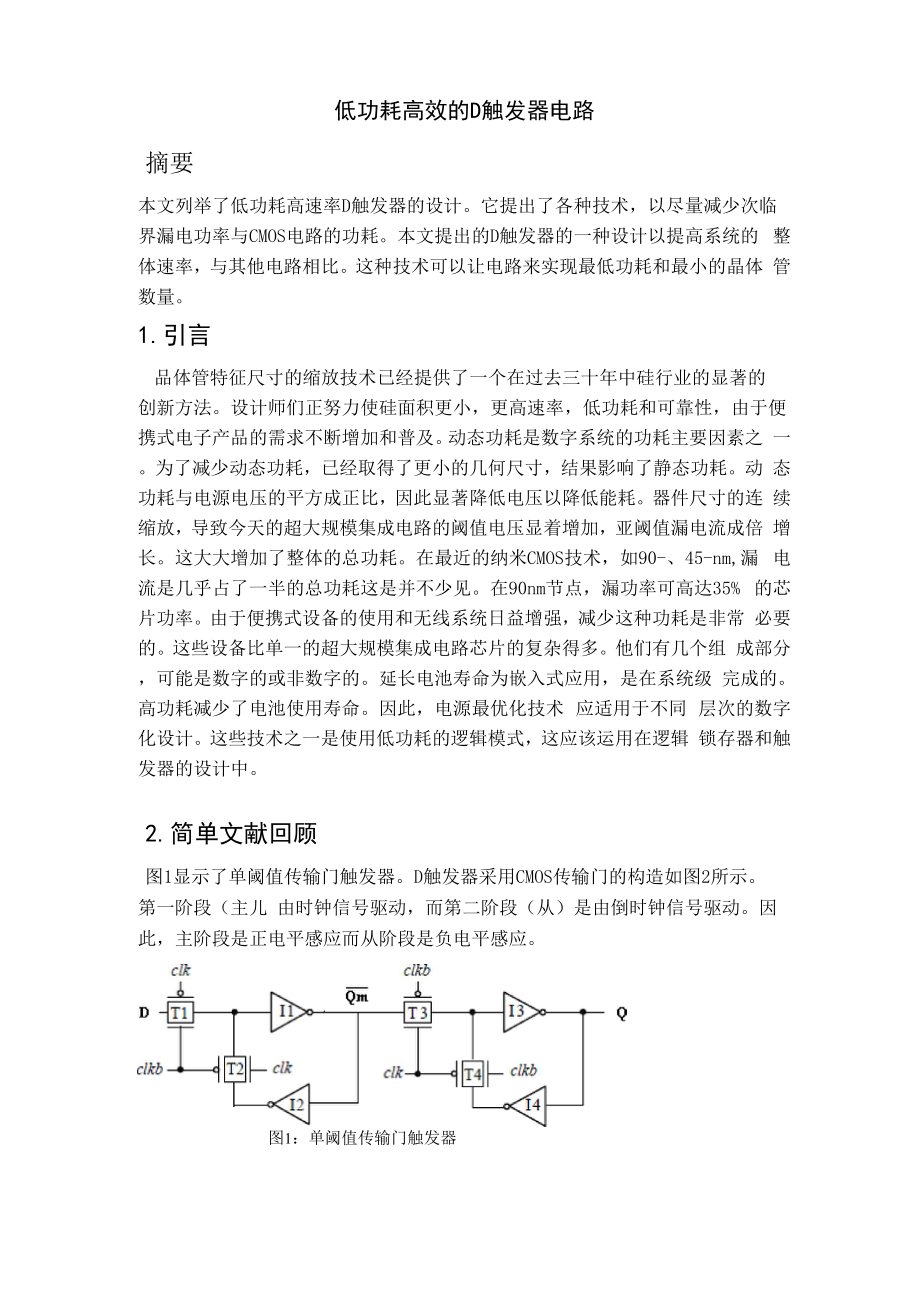

3、 锁存器和触发器的设计中。2.简单文献回顾图1显示了单阈值传输门触发器。D触发器采用CMOS传输门的构造如图2所示。 第一阶段(主儿 由时钟信号驱动,而第二阶段(从)是由倒时钟信号驱动。因 此,主阶段是正电平感应而从阶段是负电平感应。图1:单阈值传输门触发器图2: CMOS D型触发器的实现时钟为高电平时,D输入主传输门,而从传输门保持有以前的值。当时钟,从 逻辑“1”变化到逻辑“0”时,主锁存器停止采样输入,存储在时钟过渡期间的 D值。在同一时间,从锁存器变得透明,传递存储的主Qm值到从传输门的输出。 输入不能影响输出,因为主传输门与输入D断开。当时钟再次,从逻辑“0”变 化到逻辑“ 1”时

4、,从锁存器锁住主锁存器的输出,和主传输门再次开始采样输 入。它也被称为单阈值传输门触发器。框图如图1.1。ST-TG触发器广泛用于 连续系统,因此,它作为一个基准电路与本文中的触发器的表现相比较。TG-FF 是一种最快的、低功耗触发器的设计之一。LFBFF是一个多阀值CMOS(MTCMOS) 存储器件,保留其状态,即使在睡眠模式下选择性地保持电源或接地路径MTCMOS 逻辑使用高电平器件作为功率门控开关设备以在睡眠模式降低漏电流。LFBFF在 MTCMOS电路睡眠模式中切断高漏路径的能力,就是只指任何从备用电压调整节 约的能量附加到进入睡眠模式节约的能量。MTCMOS睡眠模式与备用电压调整的

5、结合使用可以显著地减少能耗。LFB触发器应用了传统的主从触发器的泄漏反馈 门原理。图3漏反馈触发器这是一个栅极长度偏置触发器显示在图4,用CMOS反相器和三态反相器来实 现。随着CMOS的缩放技术,栅极长度、氧化层厚度与掺杂浓度的变化越来越显 著。如果我们只对当D输入和Q输出信号都很低时被关闭的品体管采用栅极长度 偏置,如图4显示,这两种状态下的触发器的泄漏量可能很大不同。标称栅极长 度的变化可以改变的漏电流并且最大限度地减少它。图4栅极长度偏置触发器一个更有效的处理亚阈值漏电流的方法,就是采用双VT技术,其中的过程包括 了高阈值电压和低阈值电压设备。拥有两种不同风格的设备,我们可以利用专 门

6、的电路拓扑结构以利用低VT的速度优势,和高VT器件的漏电流减少的优点。 双VT技术提供了固有的快速,非漏设备,可以通过在提供所需性能参数的过程 中来设计。它的结构称作STTG触发器,但较高的阈值电压被分配到晶体管(在 表格5中),以减少其漏电流,用来保持其状态。DT-TG触发器有两条路径,即 非关键路径和关键路径。保持这种状态的电路使用高阈值品体管来减少它的漏 电流。它的性能的维持取决于在关键路径上的低阈值品体管。此外,没有造成任 何额外的动态功率,因为没有更多的晶体管添加到触发器中2。10II1513图5:双阈值传输门触发器3.设计建议虽然图5所示的电路给出了最少的延迟,但功耗非常高。为了克

7、服这个系统的缺 点,我们提出另一个设计。通过使用图6所示的技术,整体功耗和功率延迟都 有效地减少了。该电路内置两个睡眠品体管在5T锁存器电路中。当时钟CLK和 输入IN都为高电平时,品体管M1, M5都关闭,剩余的M2, M3, M4开启。输出 变为高电平。在开启时钟周期内,无论输入的值是多少,它都为输出值。它也可 以作为触发器,当输入IN脉冲宽度很少时5 6。在MTCMOS电路中运用了睡 眠品体管,它有高阈值电压。|_|T4图6:使用MTCMOS技术的D触发器在活跃状态下,高VT晶体管的开启|,由低VT晶体管组成的逻辑门可以运行低开 关功耗,并且传输延迟较小。当驱动电路进入待机模式,另一方面

8、,高VT晶体 管被关闭,任何可能源于内部低电路亚阈值漏电流的传导路径被有效地切断4, 9。4.仿真分析4.1仿真环境所有的电路都利用BSIM3V3的90纳米技术在tanner EDA软件进行了模拟。为 了建立一个公正的测试环境,每个电路都在相同的输入模式下进行测试。4.2模拟对比本节中的各种D触发器将在延迟,功耗和功率延迟各方面进行比较。本文运用 ST-TG作为基准电路,来比较他们的性能。表1和表2显示各种D触发器在不同 VDD下产生的延迟。很显然从表1和表2可以看出,VDD值越高,与其他电路相 比较,ST-TG延迟越小,VDD值越小,DT-TG电路中延迟越小。表1 D触发器的延迟(秒)比较V

9、ddST-TGLF-TGGLB11.96E-02.25E-02.02E-08881.21.99E-01.07E-01.99E-08881.41.99E-09.41E-02.00E-08981.64.27E-11.01E-02.00E-00881.88.68E-11.04E-01.99E-00882.09.71E-01.05E-01.99E-0988表2 D触发器的延迟(秒)比较VddDT-TG8TMTCMOS14.62E-17.20E-01.98E-00981.27.15E-11.06E-01.99E-00881.47.68E-11.00E-02.00E-00881.69.86E-01.00E

10、-02.00E-09881.88.68E-11.04E-01.99E-00882.09.71E-01.05E-01.99E-0988触发器功耗被列在表3和4。最低功耗可以在MTCMOS电路中得到。表3 D触发器的消耗功率(瓦特)比较VddST-TGLF-TGGLB12.83E-02.45E-07.20E-06671.26.67E-03.89E-01.68E-06661.41.19E-05.74E-03.36E-05661.61.42E-08.55E-05.64E-05661.82.62E-01.24E-01.82E-05552.06.79E-01.63E-0 3.18E-0555表4 D触发器

11、的消耗功率(瓦特)比较VddDT-TG8TMTCMOS11.20E-05.20E-01.17E-05771.25.28E-01.04E-01.98E-05671.41.24E-01.78E-01.32E-04661.62.04E-02.56E-05.06E-04671.83.47E-03.50E-07.66E-04672.09.30E-04.58E-01.12E-0266图7和8显示电源Vdd和触发器的功率延迟。从图7我们可以看出,LF-TG具 有稳定的低的PDP与其他电路相比。而从图8可以分析出MTCMOS电路有更好的 表现,电源VDD在1至2V范围内不断变化时PDP是恒定的。3.00E-1

12、3 -2.00E-13 -1.00E-13 -O.OCiE+OO -ST-TGZZB-_FTG- = = f-GLB-FF7.00E-136.005-135.00E-134.OOE-13 d11.21.41.61.B2VDD图7:各种触发器PDP随着电源电压的变化2.00E-13MTCMOS-= =f-_FTG-F二1 .BOE-131.60E-131.405-13.1.20E-13g 1.00E-13-B.00E-146.00E-144.00E-142.00E-14 -O.OOE+OO -11.2 1.4 1.6 l.B 2VDD图8:各种触发器PDP随着电源电压的变化5.结论对于低功耗应用,VDD的缩放是固定的以得到最佳结果。因此DT-TG电路用作 低电源。虽然它具有较高的速度和更低的延迟,但它有更多的功耗。对于高性 能超大规模集成电路系统最小化功耗是必须的。为了有更低的功耗,我们使用 MTCMOS电路。这里所提出的图6描述的电路比其他电路具有更低的功耗,因为 它拥有更少的晶体管数量。所有电路都计算PDP。在这些电路中,MTCMOS触发器 拥有最少的功率时延,因此其性能是最好的。它实现了大量能源的节约,超过了 在其他类似实现的电路。这一设计思想可以提供一个重要意义的参考,将引导 其他电路的设计。

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 卡通可爱绿色小学生家长会模板课件

- 卡通可爱老师教育教学模板课件

- 卡通可爱幼儿园大班家长会模板课件

- 卡通夏日暑假班会家长会模板课件

- 卡通可爱创意爱情告白求婚婚礼婚庆策划方案模板课件

- 卡通可爱军人动态模板通用模板课件

- 卡通可爱五一劳动最光荣主题班会模板课件

- 卡通可爱小学生常用急救知识模板课件

- 卡通动画小乌龟Franklin_02_02【声音字幕同步】课件

- 卡通儿童预防冬季流感科普宣传模板课件

- 卡通动漫动物人物绘制课件

- 卡通可爱儿童节主题活动策划方案模板课件

- 卡通儿童珍爱生命防溺水主题班会模板课件

- 卡通动漫教育教学课程设计教师说课模板课件

- 身体工作动态静心资料来源Osho的静心与健康若欲详解敬请课件