3组合逻辑电路习题解答(精品)

3组合逻辑电路习题解答(精品)

《3组合逻辑电路习题解答(精品)》由会员分享,可在线阅读,更多相关《3组合逻辑电路习题解答(精品)(29页珍藏版)》请在装配图网上搜索。

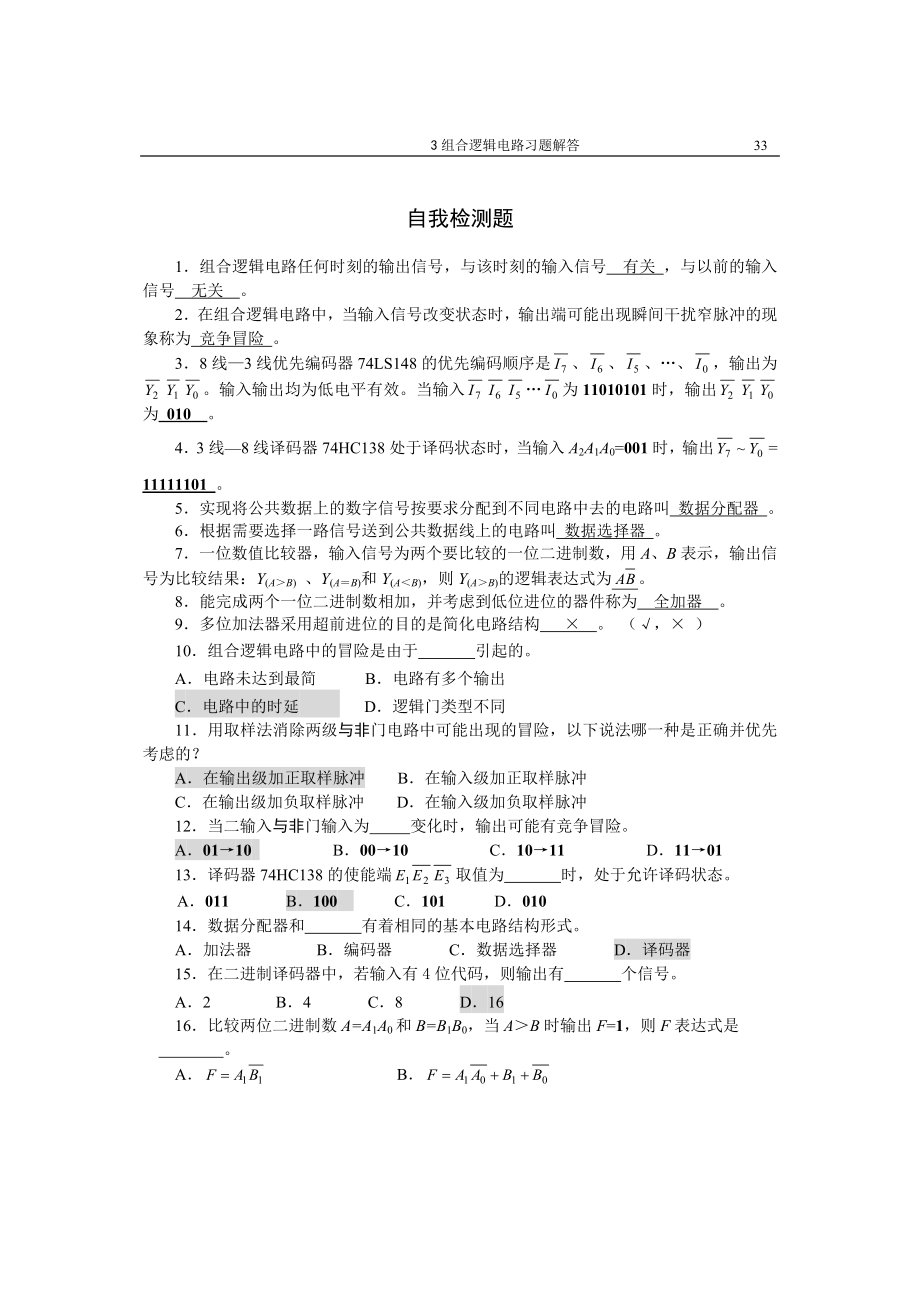

1、 3组合逻辑电路习题解答 61自我检测题1组合逻辑电路任何时刻的输出信号,与该时刻的输入信号 有关 ,与以前的输入信号 无关 。2在组合逻辑电路中,当输入信号改变状态时,输出端可能出现瞬间干扰窄脉冲的现象称为 竞争冒险 。38线3线优先编码器74LS148的优先编码顺序是、,输出为。输入输出均为低电平有效。当输入为11010101时,输出为 010 。43线8线译码器74HC138处于译码状态时,当输入A2A1A0=001时,输出= 11111101 。5实现将公共数据上的数字信号按要求分配到不同电路中去的电路叫 数据分配器 。6根据需要选择一路信号送到公共数据线上的电路叫 数据选择器 。7一

2、位数值比较器,输入信号为两个要比较的一位二进制数,用A、B表示,输出信号为比较结果:Y(AB) 、Y(AB)和Y(AB),则Y(AB)的逻辑表达式为。8能完成两个一位二进制数相加,并考虑到低位进位的器件称为 全加器 。9多位加法器采用超前进位的目的是简化电路结构 。 (, )10组合逻辑电路中的冒险是由于 引起的。A电路未达到最简 B电路有多个输出C电路中的时延 D逻辑门类型不同11用取样法消除两级与非门电路中可能出现的冒险,以下说法哪一种是正确并优先考虑的?A在输出级加正取样脉冲 B在输入级加正取样脉冲C在输出级加负取样脉冲 D在输入级加负取样脉冲12当二输入与非门输入为 变化时,输出可能有

3、竞争冒险。A0110 B0010 C1011 D110113译码器74HC138的使能端取值为 时,处于允许译码状态。A011 B100 C101 D01014数据分配器和 有着相同的基本电路结构形式。A加法器 B编码器 C数据选择器 D译码器15在二进制译码器中,若输入有4位代码,则输出有 个信号。A2 B4 C8 D1616比较两位二进制数A=A1A0和B=B1B0,当AB时输出F=1,则F表达式是 。 A B C D17集成4位数值比较器74LS85级联输入IAB、IA=B、IAB分别接001,当输入二个相等的4位数据时,输出FAB、FA=B、FAB分别为 。A010 B001 C100

4、 D01118实现两个四位二进制数相乘的组合电路,应有 个输出函数。A 8 B9 C10 D11 19设计一个四位二进制码的奇偶位发生器(假定采用偶检验码),需要 个异或门。A2 B3 C4 D520在图T3.20中,能实现函数的电路为 。(a) (b) (c)图T3.20A电路 (a) B电路(b) C电路(c) D都不是习 题1分析图P3.1所示组合逻辑电路的功能,要求写出与-或逻辑表达式,列出其真值表,并说明电路的逻辑功能。图P3.1解: CO=AB+BC+AC真值表ABCSCOABCSCO0000010010001101010101010110010110111111电路功能:一位全加

5、器,A、B为两个加数,C为来自低位的进位,S是相加的和,CO是进位。2已知逻辑电路如图P3.2所示,试分析其逻辑功能。图P3.2解:(1)逻辑表达式,(2)真值表ABCFABCF00001001001110110101110101111110(3)功能从真值表看出,ABC=000或ABC=111时,F=0,而A、B、C取值不完全相同时,F=1。故这种电路称为“不一致”电路。3试用与非门设计一组合逻辑电路,其输入为3位二进制数,当输入中有奇数个1时输出为1,否则输出为0。解:(1)真值表 ABCFABCF00001001001110100101110001101111(2)(无法用卡诺图化简)(

6、3)逻辑图44位无符号二进制数A( A3A2A1A0),请设计一个组合逻辑电路实现:当0A8或12A15时,F输出1,否则,F输出0。解:(1)真值表:A3A2A1A0FA3A2A1A0F00000000000011110011001101010101111111111111111100001111001100110101010100001110(2)表达式 (3)电路图 (4)如果要求用与非门实现,则:逻辑图:5约翰和简妮夫妇有两个孩子乔和苏,全家外出吃饭一般要么去汉堡店,要么去炸鸡店。每次出去吃饭前,全家要表决以决定去哪家餐厅。表决的规则是如果约翰和简妮都同意,或多数同意吃炸鸡,则他们去炸

7、鸡店,否则就去汉堡店。试设计一组合逻辑电路实现上述表决电路。解:(1)逻辑定义:A、B、C、D分别代表约翰、简妮、乔和苏。F=1表示去炸鸡店,F=0表示去汉堡店。(2)真值表ABCDFABCDF00000000000011110011001101010101000000011111111100001111001100110101010100011111(3)用卡诺图化简 (4)逻辑图 F=AB+ACD+BCD6试设计一个全减器组合逻辑电路。全减器是可以计算三个数X、Y、BI的差,即D=X-Y-CI。当XY+BI时,借位输出BO置位。解:设被减数为X,减数为Y,从低位来的借位为BI,则1位全减器

8、的真值表如图 (a)所示,其中D为全减差,BO为向高位发出的借位输出。(1)真值表XYBIDBOXYBIDBO0000010010001111010001011110000110111111由卡诺图得电路图7设计组合逻辑电路,将4位无符号二进制数转换成格雷码。解:(1)列出4位二进制码4位格雷码的转换真值表,如表所示。输 入输 出输 入输 出B3B2B1B0G3G2G1G0B3B2B1B0G3G2G1G0000000001000110000010001100111010010001110101111001100101011111001000110110010100101011111011011

9、01100101111010010111010011111000(2)根据真值表分别画出输出变量G3,G2,G1,G0的卡诺图,如图4.1.2-12所示。化简后,得,(3)由逻辑表达式得电路实现,如图所示。8请用最少器件设计一个健身房照明灯的控制电路,该健身房有东门、南门、西门,在各个门旁装有一个开关,每个开关都能独立控制灯的亮暗,控制电路具有以下功能:(1)某一门开关接通,灯即亮,开关断,灯暗;(2)当某一门开关接通,灯亮,接着接通另一门开关,则灯暗;(3)当三个门开关都接通时,灯亮。解:设东门开关为A,南门开关为B,西门开关为C。开关闭合为1,开关断开为0。灯为Z,等暗为0,灯亮为1。根据

10、题意列真值表如下:ABCZABCZ00001001001110100101110001101111(2)画出卡诺图如图所示。(3)根据卡诺图,可得到该逻辑电路的函数表达式:(3)根据逻辑函数表达式,可画出逻辑电路图如图所示。9设计一个能被2或3整除的逻辑电路,其中被除数A、B、C、D是8421BCD编码。规定能整除时,输出L为高电平,否则,输出L为低电平。要求用最少的与非门实现。(设0能被任何数整除)解:(1)真值表 ABCDLABCDL00001100010001010011001011010001111011010011100010101101011011110011101111(2)用卡

11、诺图化简(3)逻辑图10如图P3.10所示为一工业用水容器示意图,图中虚线表示水位,A、B、C电极被水浸没时会有高电平信号输出,试用与非门构成的电路来实现下述控制作用:水面在A、B间,为正常状态,亮绿灯G;水面在B、C间或在A以上为异常状态,点亮黄灯Y;面在C以下为危险状态,点亮红灯R。要求写出设计过程。图P3.10解:(1)真值表ABCGYRABCGYR000001100001010101010110011100111010(2)卡诺图化简(3)逻辑图11试用卡诺图法判断逻辑函数式Y(A,B,C,D)=m(0,1,4,5,12,13,14,15)是否存在逻辑险象,若有,则采用增加冗余项的方法

12、消除,并用与非门构成相应的电路。解:卡诺图如图(a)所示。最简逻辑函数式为:此函数存在逻辑险象。只要如图所示增加冗余项即可,逻辑式变为:用与非门构成的相应电路如图 (b)所示。(a) (b)12已知,求Y的无竞争冒险的最简与-或式。解:卡诺图如图所示:上式中为冗余项,以消除竞争冒险。13某一组合电路如图P3.13所示,输入变量(A,B,D)的取值不可能发生(0,1,0)的输入组合。分析它的竞争冒险现象,如存在,则用最简单的电路改动来消除之。图P3.13解:解法1:从逻辑图得到以下表达式:根据表达式得到卡诺图:但由于从卡诺图可见,包围圈有两处相切,因此存在竞争冒险现象。可以通过相切点位置增加一个

13、乘积项,得进一步分析,当ACD=000时, ,由于输入变量(A,B,D)的取值不可能发生(0,1,0)的输入组合,因此,当ACD=000时,B必然为0,不会产生竞争冒险。因此,这一项不需要增加,只需要增加。电路图为:解法二:如果逻辑表达式在某种取值下,出现、,就有可能出现竞争冒险。根据逻辑表达式,和不会出现。当A=C=D=0,出现,但由于输入变量(A,B,D)的取值不可能发生(0,1,0)的输入组合,因此,当ACD=000时,B必然为0,因此也不会产生竞争冒险。只有当A=B=1,D=0,出现,存在竞争冒险问题,加冗余项可消除竞争冒险。14电路如图P3.14所示,图中均为2线4线译码器。(1)欲

14、分别使译码器处于工作状态,对应的C、D应输入何种状态(填表P3.12-1);(2)试分析当译码器工作时,请对应A、B的状态写出的状态(填表P3.12-2);(3)说明图P3.14的逻辑功能。表P3.14-1 表P3.14-2处于工作状态的译码器C、D应输入的状态ABCD00011011图P3.14解:处于工作状态的译码器C、D应输入的状态ABCD00000111010110111010110111111110逻辑功能:由74LS139构成的4线16线译码器15图P3.15所示电路是由3线-8线译码器74HC138及门电路构成的地址译码电路。试列出此译码电路每个输出对应的地址,要求输入地址A7A

15、6A5A4A3A2A1A0用十六进制表示。图P3.15解:由图可见,74HC138的功能扩展输入端必须满足E11、才能正常译码,因此E1A31;,即A41,A51; ,即A60,A70。所以,该地址译码器的译码地址范围为A7A6A5A4A3A2A1A000111A2A1A00011100000111111,用十六进制表示即为38H3FH。输入、输出真值表如表1所示。表1 地址译码器的真值表地址输入译码输出A7A6A5A4A3A2A1A038H0111111139H101111113AH110111113BH111011113CH111101113DH111110113EH111111013FH

16、1111111016写出图P3.16所示电路的逻辑函数,并化简为最简与-或表达式。图P3.16解:由图(a)写出逻辑函数并化简,得17试用一片3线-8线译码器74HC138和最少的门电路设计一个奇偶校验器,要求当输入变量ABCD中有偶数个1时输出为1,否则为0。(ABCD为0000时视作偶数个1)。解:连接图18用一个8线-3线优先编码器74HC148和一个3线-8线译码器74HC138实现3位格雷码3位二进制的转换。解:根据下表可得到连线图:G2G1G0B2B1B000000000100101101001001111010011110110111010011119根据图P3.19所示4选1数

17、据选择器,写出输出Z的最简与-或表达式。解: 20由4选1数据选择器和门电路构成的组合逻辑电路如图P3.20所示,试写出输出E的最简逻辑函数表达式。解: 图P3.19 图P3.2021由4选1数据选择器构成的组合逻辑电路如图P3.21所示,请画出在图P3.21所示输入信号作用下,L的输出波形。图P3.21解:4选1数据选择器的逻辑表达式为:将A1=A,A0=B,D0=1,D1=C,D3=C代入得根据表达式可画出波形图:22已知用8选1数据选择器74LS151构成的逻辑电路如图P3.22所示,请写出输出L的逻辑函数表达式,并将它化成最简与-或表达式。图P3.22解:(1)写出逻辑函数表达式:(2

18、)用卡诺图化简23用一个8选1数据选择器74LS151和非门实现:解: 24图P3.24所示是用二个4选1数据选择器组成的逻辑电路,试写出输出Z与输入M、N、P、Q之间的逻辑函数式。图P3.24解;25用二个4选1数据选择器实现函数L,允许使用反相器。解:电路图26一个组合逻辑电路有两个控制信号C1和C2,要求: (1)C2C1=00时,(2)C2C1=01时,(3)C2C1=10时,(4)C2C1=11时,试设计符合上述要求的逻辑电路(器件不限)解:方法一:真值表卡诺图化简逻辑图真值表C2C1ABFC2C1ABF0000010001000111001000101101000011010110

19、0100111000010111101001101111000111011111卡诺图化简逻辑图方法二:利用数据选择器和少量门电路实现27试用4选1数据选择器74LS153(1/2)和最少量的与非门实现逻辑函数 。解:令A1=C,A0=D,D2=1,D3=0连线图:28P(P2P1P0)和Q(Q2Q1Q0)为两个三位无符号二进制数,试用一个74LS138和一个74LS151和尽可能少的门电路设计如下组合电路:当P=Q时输出F=1,否则F=0。解:29试用8选1数据选择器74LS151实现逻辑函数L=AB+AC。解:30用8选1数据选择器74LS151设计一个组合电路。该电路有3个输入A、B、C

20、和一个工作模式控制变量M,当M=0时,电路实现“意见一致”功能(A,B,C状态一致时输出为1,否则输出为0),而M=1时,电路实现“多数表决”功能,即输出与A,B,C中多数的状态一致。解:MABCFMABCF00000000000011110011001101010101100000011111111100001111001100110101010100010111电路图31已知8选1数据选择器74LS151芯片的选择输入端A2的引脚折断,无法输入信号,但芯片内部功能完好。试问如何利用它来实现函数F(A,B,C)m(1,2,4,7)。要求写出实现过程,画出逻辑图。解:对于LSTTL集成芯片,某

21、个输入引脚折断后该脚悬空,相当于输入高电平1。74LS151的高位地址端A2折断后,输出不再响应D0,D1,D2,D3输入,8选1数据选择器只相当于一个4选1,此时地址输入为A1A0,数据输入为D4,D5,D6,D7,输出Y等于与函数F相比较不难看出,只要令AB为地址,则D4C,D5,D6,D7C。逻辑图如图所示。图A4.2.2-5 题4.2.2-11的电路实现32用三片四位数值比较器74LS85实现两个12位二进制数比较。解:33用一片4位数值比较器74HC85和适量的门电路实现两个5位数值的比较。解:高4位加到比较器数值输入端,最低位产生级联输入。W0 V0I(AB)I(AB)I(A=B)

22、0 00010 10 101 01001 1001,I(A=B)=W0V034用两个四位加法器74283和适量门电路设计三个4位二进制数相加电路。解:三个4位二进制数相加,其和应为6位。基本电路如图所示。两个加法器产生的进位通过一定的逻辑生成和的高两位。CO1CO2S5S40000010110011110, 35A、B为4位无符号二进制数(B0),用一个74LS283、非门和一个其它类型门电路实现:当A=(B-1)模16时,输出Y=1,否则为0。解: (B-1)模16即为B-1 A=B-1时Y=1,否则Y=0,即B-1-A=B+1-1=B+为0时,Y=1。36A、B为四位二进制数,试用一片74

23、283实现Y=4A+B。解:Y=4A+B=A3A2A1A000+B3B2B1B037用一片74283和尽量少的门电路设计余3码到2421码的转换。解:余3码到2421码的转换的真值表为:A3A2A1A0B3B2B1B000110000010000010101001001100011011101001000101110011100101011011011111011001111从真值表中可以看到,当A3=0时,B=A-3,当A3=1时,B=A+338设计一个一位8421BCD码乘以5的电路,要求输出也为8421BCD码。要求:(1)用4线/16线译码器及门电路实现 ;(2)只用四位全加器74LS

24、283实现;(3)不用任何器件实现。解:根据题意列出真值表A3A2A1A0B7B6B5B4B3B2B1B0000000000000000100000101001000010000001100010101010000100000010100100101011000110000011100110101100001000000100101000101(1)从真值表可写出逻辑表达式:B7=0,B3=0,B1=0,B6=m(8,9),B5=m(4,5,6,7),B4=m(2,3,6,7),B0=B2=m(1,3,5,7,9)。(2)用全加器实现逻辑图与36题同。(3)不用任何器件实现B7=0,B6=A3,B5=A2,B4=A1,B3=0,B2=A0,B1=0,B0=A039利用两片并行进位加法器和必要的门电路设计一个8421BCD码加法器。8421BCD码的运算规则是:当两数之和小于等于9(1001)时,所得结果即为输出;当所得结果大于9时,则应加上6(0110)。 解:连线图如图所示。加法器1完成两个加数得初始加法,加法器2对加法器1输出进行修正。

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 七年级数学:平面直角坐标系中不规则图形面积的计算课件

- 地理环境的差异性课件——曲靖市麒麟区第一中学-郭金涛1

- 高考数学文科一轮复习(北京卷B)ppt课件102双曲线及其性质

- 剖宫产瘢痕妊娠课件

- 七年级《走进初中-享受学习》主题班会ppt课件

- 2020高端楼盘营销渠道拓客课件

- 七年级道德与法治下册第四单元走进法治天地第九课法律在我们身边第1框生活需要法律ppt课件2新人教版

- 七年级生物血管和心脏课件

- 高考数学一轮复习讲义-第一章-1.2-命题及其关系、充分条件与必要条件ppt课件

- 2021公司元旦跨年预售活动方案课件

- 高考数学一轮复习-第十八章-第2讲-极坐标与参数方程ppt课件-文

- 高考数学一轮复习-第二章第四节-幂函数与二次函数ppt课件-理-(广东专用)

- 北欧家具设计课件

- 高考数学一轮复习5.35特殊数列求和ppt课件理

- 高考数学浙江专用二轮培优ppt课件专题六第1讲排列组合二项式定理