微处理器结构及基本工作原理

微处理器结构及基本工作原理

《微处理器结构及基本工作原理》由会员分享,可在线阅读,更多相关《微处理器结构及基本工作原理(51页珍藏版)》请在装配图网上搜索。

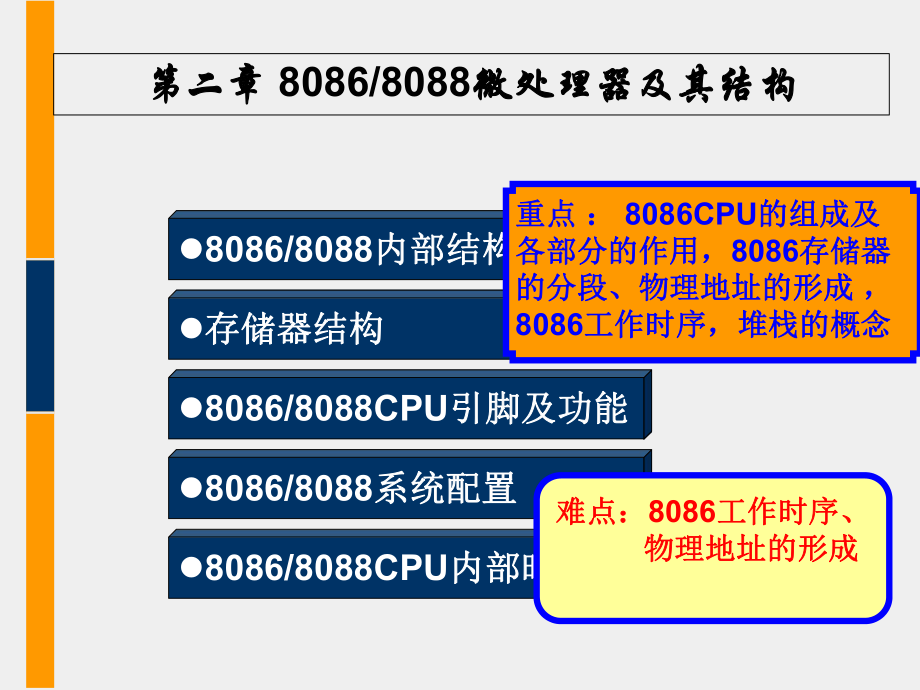

1、第二章第二章 8086/8088微处理器及其结构微处理器及其结构l8086/8088内部结构内部结构 l存储器结构存储器结构 l8086/8088CPU引脚及功能引脚及功能 l8086/8088系统配置系统配置 l8086/8088CPU内部时序内部时序 重点重点:8086CPU的组成及的组成及各部分的作用,各部分的作用,8086存储器存储器的分段、物理地址的形成的分段、物理地址的形成,8086工作时序,堆栈的概念工作时序,堆栈的概念难点:难点:8086工作时序、工作时序、物理地址的形成物理地址的形成1.8086/8088 CPU主要性能l字长字长:16位位/准准16位位l时钟频率:时钟频率:

2、5MHzl数据总线、地址总线复用数据总线、地址总线复用l内存容量内存容量:20位地址总线,位地址总线,1MB存储空间存储空间l端口地址:端口地址:16位位I/O地址总线,地址总线,64KB个端口个端口l中断功能:内部软件中断,外部硬件中断,中断功能:内部软件中断,外部硬件中断,可管理可管理256个中断源个中断源l两种工作模式两种工作模式 :支持单片:支持单片CPU或多片或多片CPU 系统工作系统工作 8086/8088CPU性能指标性能指标 8086:是是INTEL系列系列16位微处理器,采用位微处理器,采用HMOS(高密(高密度金属氧化物半导体)技术,集成度为度金属氧化物半导体)技术,集成度

3、为29000个管片。个管片。数据总线:数据总线:16位位地址总线:地址总线:20位,可直接寻址的地址空间为位,可直接寻址的地址空间为 1M字节。字节。8088:准准16位机,位机,CPU内部数据总路线为内部数据总路线为16位,外部位,外部8位,位,20位地址总线,推出位地址总线,推出8088的目的是为了向下兼容以的目的是为了向下兼容以前的前的8位微型机。位微型机。2.8086/8088内部结构 内内 部部 结结 构构 l8086CPU结构框图及分析结构框图及分析 l8086CPU内部寄存器内部寄存器 l指令执行单元指令执行单元EU l总线接口单元总线接口单元BIU l8088CPU的指令流水线

4、的指令流水线 l通用寄存器通用寄存器 l段寄存器段寄存器 l标志寄存器标志寄存器 l指令指针寄存器指令指针寄存器 2.1 8086CPU工作方式工作方式 微处微处 理器理器 堆栈段堆栈段 存储存储 器接器接 口电口电 路路 存存储储器器附加段附加段 数据段数据段 代码段代码段 代码段代码段1 00000HFFFFFH2.2 8086CPU内部结构框架内部结构框架 ALUTMPTMP标志寄存器标志寄存器FR控制单元EU通用寄存器161616指令队列缓冲器总线控制逻辑通信寄存器CSESSSDSIP地址产生器BIU16816202.2 8086CPU内部结构框架内部结构框架 ALUTMPTMP标志寄

5、存器标志寄存器FR控制单元EU通用寄存器161616指令队列缓冲器总线控制逻辑通信寄存器CSESSSDSIP地址产生器BIU1681620 执行部件执行部件EU的作用:负责的作用:负责执行指令、形成有效地址执行指令、形成有效地址EA。EU 包括四部分:包括四部分:运算器运算器ALU+TEMP 标志寄存器标志寄存器 控制单元控制单元 通用寄存器通用寄存器 2.2 8086CPU内部结构框架内部结构框架 ALUTMPTMP标志寄存器标志寄存器FR控制单元EU通用寄存器161616指令队列缓冲器总线控制逻辑通信寄存器CSESSSDSIP地址产生器BIU1681620 总线接口部件总线接口部件BIU的

6、作用是的作用是预取指令、形成实际地址预取指令、形成实际地址PA、输入输出数据。输入输出数据。BIU主要由五部主要由五部分组成:分组成:指令队列缓冲器指令队列缓冲器 总线控制逻辑总线控制逻辑 段寄存器段寄存器 指令指针寄存器指令指针寄存器 地址产生器地址产生器 l总线利用率高。总线利用率高。串行结构:取指令串行结构:取指令取操作数取操作数执行指令执行指令存放结果存放结果 lCPU利用率高,计算速度快。利用率高,计算速度快。l两部分的动作管理遵循以下原则。两部分的动作管理遵循以下原则。1.每当每当8086的指令队列中有的指令队列中有2个空字节,个空字节,BIU就会自动把指令就会自动把指令取到指令队

7、列中取到指令队列中;2.同时同时EU从指令队列中取出一条指令并分析、执行指令;从指令队列中取出一条指令并分析、执行指令;3.当指令队列已满而当指令队列已满而EU对对BIU又无总线访问请求时,又无总线访问请求时,BIU进入进入空闲状态;空闲状态;4.在执行转移、调用和返回指令时,指令队列中原有内容被自在执行转移、调用和返回指令时,指令队列中原有内容被自动清除。动清除。微处理器结构分析微处理器结构分析 2.3 8088CPU内部结构框架内部结构框架 l指令队列长度仅有指令队列长度仅有4个字节,队列中出现个字节,队列中出现1个个 空闲字节,空闲字节,BIU就会自动访问存储器,取新的就会自动访问存储器

8、,取新的 指令。指令。lBIU通过总线控制电路与外部交换数据的数据通过总线控制电路与外部交换数据的数据 总线宽度是总线宽度是8位,总线控制电路与专用寄存器位,总线控制电路与专用寄存器 之间的数据总线宽度也是之间的数据总线宽度也是8位。位。2.3 8088CPU内部结构框架内部结构框架 2.4 寄存器通用寄存器寄存器通用寄存器 四个四个16位通用寄存器、两个变址寄位通用寄存器、两个变址寄存器、两个指针寄存器。存器、两个指针寄存器。AX:累加器(:累加器(Accumulator)BX:基址寄存器(:基址寄存器(Base Index)CX:计数寄存器(:计数寄存器(Count Index)DX:数据

9、寄存器(:数据寄存器(Data Index)SI:源变址寄存器(:源变址寄存器(Source Index)DI:目标寄存器(:目标寄存器(Destination Index)SP:堆栈指针(:堆栈指针(Stack Pointer)BP:基址指针(:基址指针(Base Pointer)AXBXCXDX0158 7ALAHBLBHCLCHDLDHSIDISPBP在某些指令中规定了某些通用寄存器的专门用法,这样可以缩短指令代码长度;或使这些寄存器的使用具有隐含的性质,以简化指令的书写形式(即在指令中不必写出使用的寄存器名称)。通用寄存器的隐含用法如左表所示。2.4 寄存器控制寄存器寄存器控制寄存器

10、指令指针寄存器IP:16位的寄存器,存放BIU要取的下一条指令的偏移地址。标致寄存器FR:FR中的含6个状态标志位,3个控制标志位。状态标志位用来反映EU执行算术运算和逻辑运算以后的结果特征;控制标志位用来控制微处理器的工作方式或工作状态。2.4 寄存器标志寄存器寄存器标志寄存器FR OF DF IF TF SF ZF AF PF CF 15870状态状态标志位标志位 CF进位标志进位标志,CF=1,有进有进(借借)位位(算术)。算术)。PF奇偶标志,含奇偶标志,含1个数为偶数,个数为偶数,PF=1。AF辅助进位位,辅助进位位,D3向向D4有进借位,有进借位,AF=1。OF溢出标志,溢出标志,

11、OF=CF+CD。OF=1,有溢出。,有溢出。SF符号标志,符号标志,SF=1,D7(D15)=1。零标志,零标志,ZF=1,结果为零。,结果为零。控制位控制位 IF中断允许标志,中断允许标志,IF=1,允许,允许CPU响应响应外设通过可屏蔽中断请求线提出的中断外设通过可屏蔽中断请求线提出的中断DF 方向标志,串,方向标志,串,DF=1,减址,减址 TF跟踪标志,跟踪标志,TF=1,CPU进入单步运行状态。进入单步运行状态。标志OFDFIFSFZFAFPFCFOVDNEINGZRACPECYNVUPDIPLNZNAPONC为1的符号为0的符号标志寄存器中的状态标志的状态表示符号CF=1 PF=

12、1 AF=0 OF=0 SF=0 ZF=0 无符号数相加无符号数相加 211 105 316 +-45 +105+60 +11010011+0110100100111100 11 11 11010011+0110100100111100 11 11 有符号数相加有符号数相加 2.4 寄存器段寄存器寄存器段寄存器 0 0A A000 0000 1001 0001 1100 0100 1101 0101 1010 0010 1011 0011 1110 0110 1111 0111 1十六进制数十六进制数0H1H2H3H4H5H6H7H8H9HAHBHCHDHEHFH0HFH 地址地址 译码译码

13、电路电路 0 0A A1 1A A2 2A A3 3A ADB8086微处理器的地微处理器的地址总线为址总线为20根,则根,则其寻址空间为:其寻址空间为:2 20 02 2=1 1M MB B00000HFFFFFH2.4 寄存器段寄存器寄存器段寄存器 矛盾:矛盾:外部地址总线为外部地址总线为20根,内部能够提供的数据为根,内部能够提供的数据为16位。位。逻辑段逻辑段1 逻辑段逻辑段2 逻辑段逻辑段3 l因为因为16位地址最多可以访问位地址最多可以访问64K的存储空的存储空间,所以每个分段的最大空间为间,所以每个分段的最大空间为64K。段起段起始地始地址址l物理地址:存储器中实实在在存在的一个

14、物理地址:存储器中实实在在存在的一个存储单元的编号,也叫实际地址。存储单元的编号,也叫实际地址。l段起始地址:分段的第一个物理地址。段起始地址:分段的第一个物理地址。00000HFFFFFHl1M的存储空间能够被分为的段数为:的存储空间能够被分为的段数为:16 l段起始地址的特点:低四位为段起始地址的特点:低四位为0。12340H 12000H 00000H 23560H FFFF0H 2.4 寄存器段寄存器寄存器段寄存器 l段基址:段起始地址高十六位(段基址:段起始地址高十六位(二二进制进制)组成的地址编码。)组成的地址编码。偏移地址偏移地址12340H2233FH 逻辑段逻辑段11238F

15、H右图所示段的段基址为:右图所示段的段基址为:1234Hl偏移地址:物理地址与所在段起始偏移地址:物理地址与所在段起始地址的差,也叫有效地址。地址的差,也叫有效地址。右图中右图中1238FH的偏移地址为:的偏移地址为:0004FHl物理地址的形成:段基址左移物理地址的形成:段基址左移4位位(二进制二进制)+偏移地址。偏移地址。l偏移地址的特点:高四位(偏移地址的特点:高四位(二进制二进制)永远为永远为0,因此仅取其低十六位。,因此仅取其低十六位。最大的偏移地址最大的偏移地址2233FH-12340H=0FFFFH2.4 寄存器段寄存器寄存器段寄存器 逻辑段逻辑段2 逻辑段逻辑段1 同一个存储单

16、元同一个存储单元25637H25630H25600H00037H00007Hl逻辑地址的特点:不唯一逻辑地址的特点:不唯一 l逻辑地址逻辑地址 段基址:偏移地址段基址:偏移地址 左图中左图中1238FH的逻辑地址为:的逻辑地址为:1234H:004FH偏移地址偏移地址12340H2233FH 逻辑段逻辑段11238FH 逻辑地址的来源逻辑地址的来源 2.4 寄存器段寄存器寄存器段寄存器 l代码段:存放等待执行的指令代码。代码段:存放等待执行的指令代码。l数据段:存放指令中所需要的操作数。数据段:存放指令中所需要的操作数。l堆栈段:一段特殊的数据存取区域。堆栈段:一段特殊的数据存取区域。l附加段

17、:通常也用来存放操作数。附加段:通常也用来存放操作数。l在程序量很大的情况下可以开辟在程序量很大的情况下可以开辟多个代码段。同理,其它逻辑段也多个代码段。同理,其它逻辑段也可以进行扩展。可以进行扩展。堆栈段堆栈段 附加段附加段 数据段数据段 代码段代码段 l各个逻辑段可以重叠。各个逻辑段可以重叠。代码段代码段1 数数据据段段1附附加加段段1l功能段:按存放数据所起到的功能不功能段:按存放数据所起到的功能不同又可以分为代码段、数据段、堆栈段同又可以分为代码段、数据段、堆栈段和附加段。和附加段。2.4 寄存器段寄存器寄存器段寄存器 l代码段寄存器代码段寄存器CS:指向当前的:指向当前的代码段,指令

18、由此段取出。代码段,指令由此段取出。l数据段寄存器数据段寄存器DS:指向当前的:指向当前的数据段,通常用来存放程序变量。数据段,通常用来存放程序变量。l堆栈段寄存器堆栈段寄存器SS:指向当前的堆:指向当前的堆栈段,堆栈操作所需的就是该段存栈段,堆栈操作所需的就是该段存储单元的内容。储单元的内容。l附加段寄存器附加段寄存器ES:指向当前的附:指向当前的附加段,通常也用来存储数据。加段,通常也用来存储数据。2.4 寄存器指令指针寄存器指令指针IP 12300H12307H 0007H IP:当前代码段当前代码段l指令指针寄存器指令指针寄存器IP存储的是当前存储的是当前预取指令的存储地址。预取指令的

19、存储地址。l对于对于8086,BIU从存储器中取过从存储器中取过一次指令后,一次指令后,IP自动加自动加2,指向下,指向下一个预取指令。一个预取指令。l对于对于8088,BIU从存储器中取过从存储器中取过一次指令后,一次指令后,IP自动加自动加1,指向下,指向下一个预取指令。一个预取指令。l程序员不能对程序员不能对IP进行存取操作,进行存取操作,程序中的转移指令、返回指令及程序中的转移指令、返回指令及中断指令能对中断指令能对IP进行操作进行操作。3 8086/8088CPU的外部特性的外部特性 有效电平 指引脚起作用时的逻辑电平。有些信号是低电平有效,也称作负逻辑,有些信号是高电平有效,也称作

20、正逻辑。三态 是指引脚除了能正常的输入或输出高、低电平之外,还能输出高阻状态。l最大模式:有多个微处理器最大模式:有多个微处理器 l最小模式:仅有最小模式:仅有8086一个微处理器一个微处理器 GNDAD14AD13AD12AD11AD10AD9AD8AD7AD6AD5AD4AD3AD2AD1AD0NMIINTRCLKGNDVcc(+5V)AD15A16/S3A17/S4A18/S5A19/S6BHE/S7MN/MXRDREADYRESETHOLD(RQ/GT0)HLDA(RQ/GT1)WR(LCCK)M/IO(S2)DT/R(S1)DEN(S0)ALE(QS0)INTA(QS1)TEST1

21、12 23 34 45 56 67 78 89 910 10 11 11 20 20 12 12 13 13 14 14 15 15 16 16 17 17 18 18 19 19 40 40 39 39 38 38 37 37 36 36 35 35 34 34 33 33 32 32 31 31 30 30 29 29 28 28 27 27 26 26 25 25 24 24 23 23 22 22 21 21 8086/8088微处理器引脚及功能微处理器引脚及功能(1)AD15AD0 分时复用的地址分时复用的地址/数据总线。数据总线。T1周期传送地址,三态输出;周期传送地址,三态输出;

22、T2T4周期传送数据,双向三态周期传送数据,双向三态输入输入/输出。输出。(2)A19/S6A16/S3 分时复用的地址分时复用的地址/状态线。状态线。S5=1,则,则IF=1;S6恒为恒为0 80868086微处理器微处理器 GNDAD14AD13AD12AD11AD10AD9AD8AD7AD6AD5AD4AD3AD2AD1AD0NMIINTRCLKGNDVcc(+5V)AD15A16/S3A17/S4A18/S5A19/S6BHE/S7MN/MXRDREADYRESETHOLD(RQ/GT0)HLDA(RQ/GT1)WR(LCCK)M/IO(S2)DT/R(S1)DEN(S0)ALE(QS

23、0)INTA(QS1)TEST1 12 23 34 45 56 67 78 89 910 10 11 11 20 20 12 12 13 13 14 14 15 15 16 16 17 17 18 18 19 19 40 40 39 39 38 38 37 37 36 36 35 35 34 34 33 33 32 32 31 31 30 30 29 29 28 28 27 27 26 26 25 25 24 24 23 23 22 22 21 21 (3)Vcc(电源电源)、GND(地地)8086微处理器只需要单一的微处理器只需要单一的+5V电源,由电源,由Vcc输入,输入,GND为接为接地

24、端。地端。80868086微处理器微处理器 (4)17根控制信号线根控制信号线。地址锁存器存储器I/O芯片VCC数据收发器 MN/MX RD CLK WRREADY M/IORESET ALE TEST BHE A16A19AD0AD15HLDA .HOLD .8086INTA .INTR DEN NMI DT/RBHE时钟发生器8282锁存器与锁存器与8086的连接的连接 8282的选通信号输入端STB和CPU的ALE端相连 8282的DI7DI0接CPU的AD7AD0 8282的输出DO7DO0就是系统地址总线的低8位 OE为输出允许信号,当OE为低电平时,8282 的输出信号DO7DO0

25、 有效;而当OE为高电平时,DO7DO0变为高阻抗。在带DMA控制器的8086单处理器系统中,将OE接地即可。最小模式8286与8086的连接当一个系统中所含的外设较当一个系统中所含的外设较多时,数据总线上需要有发多时,数据总线上需要有发送器和接收器来增加驱动能送器和接收器来增加驱动能力。发送器和接收器简称为力。发送器和接收器简称为收发器,也称为总线驱动器收发器,也称为总线驱动器80888088系统,只用一片系统,只用一片8286 8286 就就可构成数据总线收发器,而可构成数据总线收发器,而8086 8086 系统中,则要用两片系统中,则要用两片82868286。82868286具有两组对称

26、的数据引具有两组对称的数据引线,线,A7A7A0A0为输入数据线,为输入数据线,B7B7B0B0为输出数据线为输出数据线收发器中数据可双向传输收发器中数据可双向传输引脚信号引脚信号T T控制数据传输方向。控制数据传输方向。当当T=1 T=1 时,就使时,就使A7A7A0A0为输为输入线,入线,B7B7B0B0为输出线;当为输出线;当T T=0=0时,则使时,则使B7B7B0B0为输入线。为输入线。T T和和CPUCPU的的DT/R DT/R 相连,相连,DT/R DT/R 为数据收发控制信号。为数据收发控制信号。lOE是输出允许信号,此信号决定了是否允许数据通过8286。在8086/8088系

27、统中,OE端和CPU的DEN端相连。l当系统中CPU 以外的总线主控部件对总线有请求,并且得到CPU允许时,CPU的DEN和DT/R 端呈现高阻状态,从而使8286 各输出端也成为高阻状态。GNDA14A13A12A11A10A9A8AD7AD6AD5AD4AD3AD2AD1AD0NMIINTRCLKGNDVcc(+5V)A15A16/S3A17/S4A18/S5A19/S6SS0MN/MXRDREADYRESETHOLD(RQ/GT0)HLDA(RQ/GT1)WR(LCCK)IO/M(S2)DT/R(S1)DEN(S0)ALE(QS0)INTA(QS1)TEST1 12 23 34 45 5

28、6 67 78 89 910 10 11 11 20 20 12 12 13 13 14 14 15 15 16 16 17 17 18 18 19 19 40 40 39 39 38 38 37 37 36 36 35 35 34 34 33 33 32 32 31 31 30 30 29 29 27 27 26 26 25 25 21 21 80888088微处理器微处理器 28 28 24 24 23 23 22 22 (1)AD7AD0 数据总线为数据总线为8条。条。(2)M/IO管脚定义相反。管脚定义相反。(3)BHE改为改为SS0。4.存储器组织l8086系统中存储器的结构系统中存

29、储器的结构 l8088系统中存储器的结构系统中存储器的结构 4.1 8086系统中存储器的结构系统中存储器的结构 l存储地址相当于房间号码,而其中存储存储地址相当于房间号码,而其中存储的数据才是我们要存取的具体内容。的数据才是我们要存取的具体内容。右图所示的存储单元地址为:右图所示的存储单元地址为:12356H该单元中存储的数据为:该单元中存储的数据为:25H25H36H00000HFFFFFH12356H程序中的表示形式为:程序中的表示形式为:12356H=25H如果存放的是字,则其表示形式为:如果存放的是字,则其表示形式为:12356H=3625H注意:字的高位存放在大地址单元,低注意:字

30、的高位存放在大地址单元,低位存放在小地址单元。程序中说明是字位存放在小地址单元。程序中说明是字数据还是字节数据。数据还是字节数据。4.1 8086系统中存储器的结构系统中存储器的结构 25H 36H 00000HFFFFFH12356H512K8 8位位奇地址奇地址存储体存储体(A A0 0=1=1)512K8位位偶地址偶地址存储体存储体(A0=0)158 7000000H00000H00000H00000HFFFFEH00001H00003H00005H00007HFFFFFHl字节交叉编址字节交叉编址 4.1 8086系统中存储器的结构系统中存储器的结构 CS A1A19高位(奇数)库高位

31、(奇数)库512K8D0D7CS A1A19低位(偶数)库低位(偶数)库512K8D0D7A1A19A0BHED8D15D0D74.1 8086系统中存储器的结构系统中存储器的结构 BHE A0 访问库名访问库名 0 0 双库,实现双库,实现16位数据的传送位数据的传送 0 1 奇地址高位库,实现奇地址高位库,实现8位数据的传送位数据的传送 1 0 偶地址低位库,实现偶地址低位库,实现8位数据的传送位数据的传送 1 1 不传送不传送BHE和和A0的控制作用的控制作用34H 12H 25H 36H 00000HFFFFFH12356H12351Hl假设存放的为字数据,则假设存放的为字数据,则 1

32、2351H=1234H12356H=3625H 规则字与非规则字规则字与非规则字 l规则字:起始地址为偶地址。微规则字:起始地址为偶地址。微处理器一次可以将数据读走。处理器一次可以将数据读走。l非规则字:起始地址为奇地址。非规则字:起始地址为奇地址。微处理器两次才能将数据读走。微处理器两次才能将数据读走。4.2 8088系统中存储器的结构系统中存储器的结构 l单一存储体单一存储体 l一次只能读取一个字节的信息一次只能读取一个字节的信息 4.3 专用和保留的存储器单元专用和保留的存储器单元00000H003FFH(共1KB)。存放中断向量表。可存放256个中断服务程序的入口地址。属于系统的RAM

33、范围。FFFF0HFFFFFH。系统上电或复位时,(CS)=FFFFH,(IP)=0000H,故FFFF0H为系统的复位地址,从这一地址开始存放一条无条件转移指令,使系统自动跳转到初始化程序。属于系统的ROM范围内。5 8086总线时序的一些概念总线时序的一些概念时序的概念:CPU各引脚信号在时间上的关系。指令周期:CPU完成一条指令所需的时间。时序图:描述某一操作过程中,芯片/总线上有关引脚信号随时间发生变化的关系图。一个指令周期由多个总线周期组成。总线周期:CPU完成一次访问内存(或接口)操作所需要的时间。一个总线周期至少包括4个时钟周期。时钟周期:由时钟发生器产生。是计算机内部最小的时间

34、单位,用Ti表示。晶振周期:晶体振荡器输出的周期。它一般分频后变为时钟周期,再作为内部工作单位。5 8086CPU内部时序 等待周期:因存储器或I/O设备速度慢引起的。空闲周期:因CPU执行指令所需时间长或在多微处理器系统中微处理器交换总线权时出现的。地址输出T1T2T3T4缓冲数据输入 T1T2T3TWT4TITIT1T2T3TWT4T1T2T3T48086CPU读时序周期T1T2T3T4地址输出CLKDSAM/IORDDENDT/RA19/S6A16/S3BHE/S7ALEAD15AD0第一周期第一周期CPUCPU输出输出2020位地址、位地址、ALEALE信号,及地址信号,及地址A A0

35、 0-A-A1919 第二周期第二周期A A1919/S/S6 6-A-A1616/S/S3 3,BHE/SBHE/S7 7输出状态输出状态S S7 7-S-S3 3;同时;同时RDRD和和DENDEN变有效变有效(低低电平电平)。第三周期第三周期 数据输入。数据输入。第四周期第四周期 从从ADAD1515-AD-AD0 0读入数据,并使读入数据,并使RDRD 信号和信号和DENDEN信号处于无效状态。信号处于无效状态。8086CPU写时序周期地址输出T1T2T3T4CLKA19/S6A16/S3BHE/S7DSAALEAD15AD0M/IOWRDENDT/R最小模式下的时序操作小结最小模式下

36、的时序操作小结一个基本总线周期由T1T4组成;T1状态:ALE、M/IO、DT/R有效,分时复用线上传送地址信息;T2状态:RD、WR、DEN信号有效。对读操作,数据线呈高阻;对写操作,直接出现输出数据;T3状态:在T3的前沿检测READY,若有效,则读操作出现输入数据;若READY无效,持续其他各控制信号,加入若干个等待态Tw,并在每个Tw前沿继续检测READY,直至READY有效为止;T4状态:接收数据,将各控制信号驱动为无效,进入无源状态,为下一个总线周期做好准备。8088与与8086的区别的区别指令预取队列:8088为4字节,8086为6字节数据总线引脚:8088有8根,8086有16根控制线引脚:8088为IO/M,而8086为M/IO 8088 为SS0,而8086 的/BHE。8088为准16位CPU,内部DB为16位,但外部仅为8位,16位数据要分两次传送

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 四年级科学下册《食物包装上的信息》教科版课件

- 加强官德修养-做有德领导教学课件

- 医院药物临床试验机构资料管理员专项培训教材课件

- 北京中小学学生电子学籍管理系统一年级信息录入培训课件

- 医疗服务全面质量管理-课件

- 加强处方点评促进合理用药课件

- 加强学科建设打造品牌医院提升三级医院综合服务能力培训课件

- 化工设备检修安全技术概述课件

- 四年级下册英语Unit2WhattimeisitPartA课时课件

- 化工设备常用零部件图样及结构选用概述课件

- 加强学习履行职责做一名称职的党务干部支部书记培训课件2

- 医务人员艾滋病病毒职业暴露的预防及处理课件

- 四年级上第四单元三位数乘两位数解决问题课件

- 四年级数学上册计算工具的认识及计算课件免

- 四年级期末家长会(语文)课件