计算机体系结构培训讲学

计算机体系结构培训讲学

《计算机体系结构培训讲学》由会员分享,可在线阅读,更多相关《计算机体系结构培训讲学(11页珍藏版)》请在装配图网上搜索。

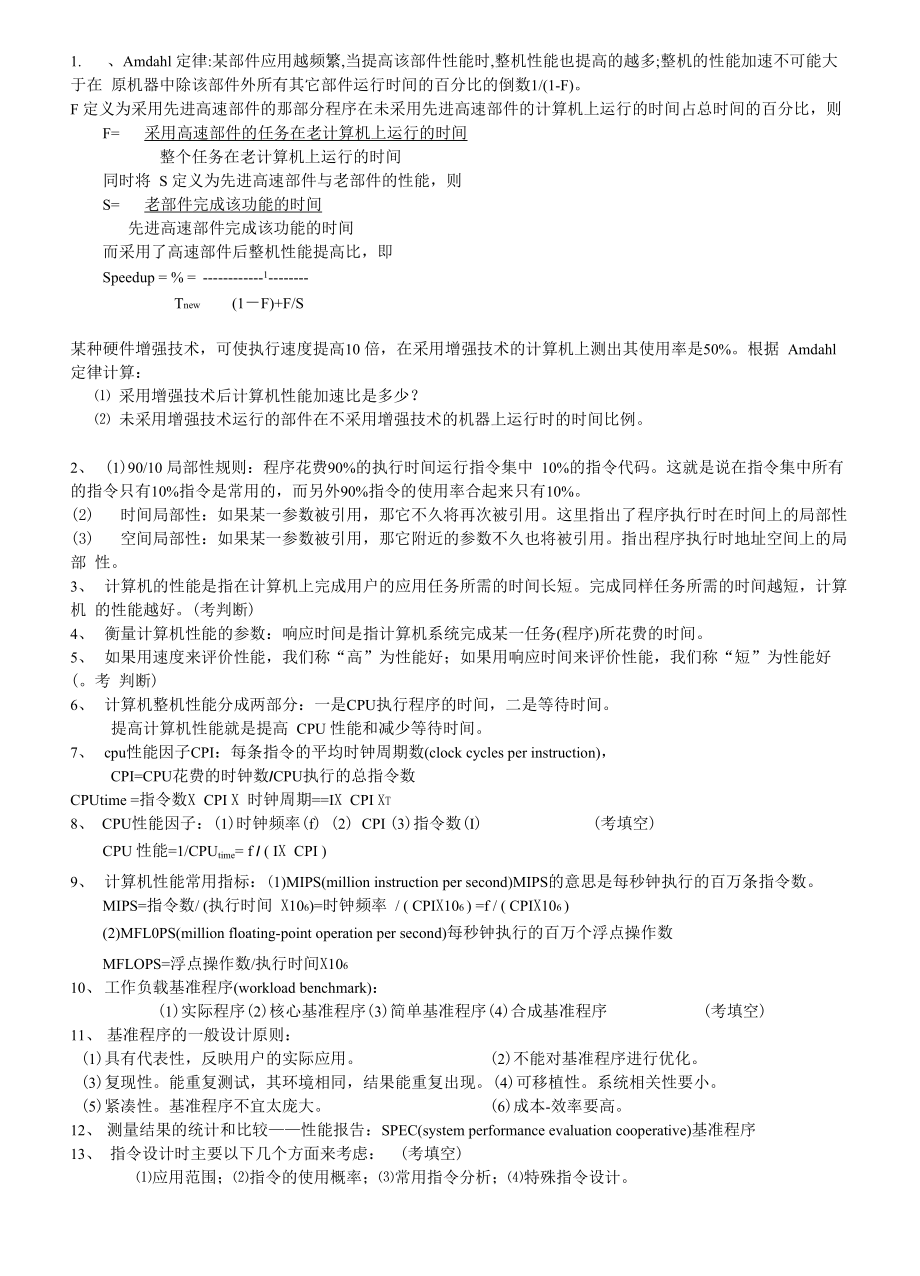

1、1. 、Amdahl 定律:某部件应用越频繁,当提高该部件性能时,整机性能也提高的越多;整机的性能加速不可能大于在 原机器中除该部件外所有其它部件运行时间的百分比的倒数1/(1-F)。F 定义为采用先进高速部件的那部分程序在未采用先进高速部件的计算机上运行的时间占总时间的百分比,则F=采用高速部件的任务在老计算机上运行的时间整个任务在老计算机上运行的时间同时将 S 定义为先进高速部件与老部件的性能,则S=老部件完成该功能的时间先进高速部件完成该功能的时间而采用了高速部件后整机性能提高比,即Speedup = % = 1Tnew(1F)+F/S某种硬件增强技术,可使执行速度提高10 倍,在采用增

2、强技术的计算机上测出其使用率是50%。根据 Amdahl 定律计算: 采用增强技术后计算机性能加速比是多少? 未采用增强技术运行的部件在不采用增强技术的机器上运行时的时间比例。2、(1)90/10 局部性规则:程序花费90%的执行时间运行指令集中 10%的指令代码。这就是说在指令集中所有 的指令只有10%指令是常用的,而另外90%指令的使用率合起来只有10%。(2) 时间局部性:如果某一参数被引用,那它不久将再次被引用。这里指出了程序执行时在时间上的局部性(3) 空间局部性:如果某一参数被引用,那它附近的参数不久也将被引用。指出程序执行时地址空间上的局部 性。3、计算机的性能是指在计算机上完成

3、用户的应用任务所需的时间长短。完成同样任务所需的时间越短,计算机 的性能越好。(考判断)4、衡量计算机性能的参数:响应时间是指计算机系统完成某一任务(程序)所花费的时间。5、如果用速度来评价性能,我们称“高”为性能好;如果用响应时间来评价性能,我们称“短”为性能好(。考 判断)6、计算机整机性能分成两部分:一是CPU执行程序的时间,二是等待时间。提高计算机性能就是提高 CPU 性能和减少等待时间。7、cpu性能因子CPI:每条指令的平均时钟周期数(clock cycles per instruction),CPI=CPU花费的时钟数/CPU执行的总指令数CPUtime =指令数X CPI X

4、时钟周期=IX CPI Xt8、 CPU性能因子:(1)时钟频率(f) (2) CPI (3)指令数(I)(考填空)CPU 性能=1/CPUtime= f / ( IX CPI )9、计算机性能常用指标:(1)MIPS(million instruction per second)MIPS的意思是每秒钟执行的百万条指令数。MIPS=指令数/ (执行时间 X106)=时钟频率 / ( CPIX106 ) =f / ( CPIX106 )(2)MFL0PS(million floating-point operation per second)每秒钟执行的百万个浮点操作数MFLOPS=浮点操作数/

5、执行时间X10610、工作负载基准程序(workload benchmark):(1)实际程序(2)核心基准程序(3)简单基准程序(4)合成基准程序(考填空)11、基准程序的一般设计原则:(1)具有代表性,反映用户的实际应用。(2)不能对基准程序进行优化。(3)复现性。能重复测试,其环境相同,结果能重复出现。(4)可移植性。系统相关性要小。(5)紧凑性。基准程序不宜太庞大。(6)成本-效率要高。12、测量结果的统计和比较性能报告:SPEC(system performance evaluation cooperative)基准程序13、 指令设计时主要以下几个方面来考虑:(考填空)应用范围;指

6、令的使用概率;常用指令分析;特殊指令设计。14、 正向条件转移大部分是不成功的,它满足条件的概率较低。(考判断)15、一般基本传送指令包含 Load, Store 和 Move 三类。(考填空)16、从操作数存放的位置来说,至少有三类地址:(1)存储器地址(2) I/O 地址(3)寄存器地址如果不加特殊说明,我们称地址就是指存储器地址或I/O地址。17、主存储器编址:计算机有两种习惯使用方法,即在字单元地址内有两种字节排列次序:第一种为低位收尾(little endian),其字节次序是低字节在最低位的排列;DEC Intel公司 第二种为高位收尾(big endian),其字节次序是高字节在

7、最低位的排列。IBM Motorola公司18、操作码的信息源熵(系统包含的平均信息量)公式(H=Pilog2Pi )式中pi为事件出现的频率,由此我们可 以比较压缩前后的信息冗余量或时间冗余量。19、“Simple is fast”和“Small is fast”,即:简单事件可以更快速处理;小规模器件的速度可以做的更快,体现 了 RISC思想的精髓。20、 构成计算机的成本组合:(1)器件成本(2)直接成本(3)间接成本(4)报价单价格(考填空)21、计算机的三种机器结构:堆栈、累加器、通用寄存器22、处理器(CPU )可分为两部分:(1.)数据通路(ALU(arithmetic logi

8、c unit)+寄存器)为处理器工作时数据实际流过的路径。(2)控制器(解释计算机机器指令代码,并按这些代码发出控制信号控制数据通道的工作以完成指令)是处理器 中的主控部分,是将指令转换为实际硬件动作的桥梁,设计最复杂。23、数据通路组成图控制部件24、寄存器:专用寄存器+通用寄存器专用寄存器:(1) PC (Program Counter)程序计数器(2) MAR(memory address register)存储器地址寄存器(3) MDR(memory data register) 存储器数据寄存器 (4) IAR(interrupt address register) 中断地址寄存器(

9、5) Temp 暂存寄存器:数据访问中起暂存作用的寄存器。不知道存在: MAR、MDR、Temp 用户透明: PC、IAR 通用寄存器:能被用户自由地用于数据计算的寄存器 寄存器堆(register file)由多个通用寄存器合起来的。存储器层次结构中的最高层,属于最小也是最快的暂存部件。25、指令的执行分为以下五个步骤:(1)取指令IF (2.)指令译码/寄存器读出ID (3)执行/有效地址计算EX(4)存储器访问/完成转移:a.访存指令b.转移指令MEM (5)写回WB26、微指令编制方式:(1)垂直微代码:加一些硬件电路来解释这些信号,而不是直接使用它们(2)水平微代码:完全不编码的微指

10、令27、中断在不同的计算机系统中有不同的叫法,Intel和IBM仍将所有的都称为中断,而Motorola将它们称为例 外,DEC则根据不同的情况,将它们称作异常、出错、自陷、放弃或中断。28、流水线的作用:提高硬件功能部件的使用率, 减少指令的平均执行时间。流水线(pipeline)是指在程序执行时多条指令重叠进行操作的一种准并行处理实现技术(流水线的并行处理是指完成一条指令的各个部件在时间上可以重叠工作)。30、 流水线竞争有三种:结构竞争(资源竞争):由资源缺乏引起。数据竞争(data hazard):由指令间 数据相关而引起。控制竞争(control hazard):由程序指针PC值的改

11、变而引起。(考填空)31、为什么计算机设计者允许结构竞争存在(1)减少成本。(2)降低单元电路的延时时间。(3)减少电路的复杂程度。32、三种数据竞争:(1)先写后读相关 RAW (read after write) (2)写写相关 WAW (write after write)(3)先读后写相关 WAR (write after read)33、指令从ID级流入EX级,一般称指令发射(instruction issue)。一条指令已建立了这一过程,称为已发射(issued)。34、浮点/整数乘法部件M 丄 M2浮点加法IFA醱(ALUEXMEM浮点/整数除法部件图429 EK级浮点操作的流水

12、结构()35、浮点乘法:15 个周期,执行周期7 个。浮点加法:执行周期4 个。浮点除法:15个周期37、集中式动态调度。记分牌有以下四级流水步骤: 发射级(issue)处理结构竞争和WAW竞争 读操作数(readoperands)动态解决RAW竞争执行(execution)写结果(writeresult) 处理WAR竞争记分牌重点掌握:38、下面我们来分析如图4-30 所示的 5 个功能部件的记分牌数据结构和工作过程。表4-24给出了执行下列简单 的指令序列时记分牌的组成信息:LDF6,34(R2)LDF2,45(R3)MULTDF0,F2,F4SUBDF8,F6,F2DIVDF10,F0,

13、F6ADDDF6,F0,F2表 4-24 记分牌的组成结构指令状态指令:状态发射 issue读操作数 read operandsexecution写结果 write resultLD F8, 34(RJjJ14LD F” 45( R3)jJ:JMULTO FOf F2, F斗zSUBD F3, Fs, F2dDIVD Fq” Fo,FgVADDDFq F;可用功能部件寄存未维备就勺动态调度MultSubiteg30域FU表424部件处称IntegerLeadRkYesFk准备就绪,可用Sub DivideMullj IntegerDivideAdd记分牌构成分三个部分:1. 指令状态。指出指令

14、工作处在上述四级中的哪一级。2. 功能部件工作状态。指出功能部件的工作情况,每个功能部件需要指出九项相关参数Busy指出功能部件地忙或空闲状态。Op功能部件所执行的操作类型。F目的寄存器。耳,Fk源操作数所用的寄存器。Qj,Qk产生源寄存器数据的功能单元。气,Rk指示源寄存器Fj, Fk准备就绪。3. 寄存器结果状态。如果有一条已激活指令有一个目的操作数是寄存器,则指出那个功能单元将写(操作) 这个寄存器。相应流水线记分牌的工作过程也分三步。从表4-24 可以看到,每条指令不论有没有发射,只要已取入流水 线,在指令状态表中就有记录。而每个功能部件在其状态表中只保持一条记录。对于上述指令序列:指

15、令状态寄存器表明第一条LD指令已经完成并且将结果写入了寄存器,而第二条LD指令已经执行完 成,但还没有写结果。第三、四、五条指令MULTD, SUBD和DIVD已经发射,但被暂停在读操作数这一级, 等候其操作数的到来。功能部件工作状态则表明第一个乘法单元在等整数单元取操作数F2,同样加法单元在等整数减法部件 的操作数F2,除法部件在等第一个乘法部件的操作数F0o加法指令 ADDD 被暂停发射,因为存在一个结构竞争,这个结构竞争是减法指令引起的,等加法功能 部件的减法指令执行完,功能部件竞争就会消除。例4-8 我们假定浮点功能部件在EX级流水级其等待延迟时间,加法部件是2时钟周期,乘法部件是10

16、时 钟周期,则对表4-24记分牌记录的代码序列和初值数据结构,分析当前指令MULTD和指令DIVD继续执行各 自进入写结果状态时记分牌的数据结构。解:第二条指令LD给MULTD和SUBD指令带来了 RAW型数据竞争,而指令MULTD给指令DIVD、指 令SUBD给指令ADDD也带来了 RAW型数据竞争。在指令DIVD和ADDD之间存在着WAR数据竞争。对加 法指令ADDD要用到的加法功能单元还存在结构竞争。因此,乘法指令进入写结果状态和除法指令DIVD进入 写结果状态是不同的,分别如表4-25和表4-26所示。表4-25指令MULTD进入写结果级前的记分牌数据结构指令指令优态发射读操作数执行完

17、成写结果LD Fs, 34(Rz)ilJJJJLD F2 45(R3)IjJ;44VMULTD Fo? F2, F4l|44VSUBD Fbj Fgj F2yJJDIVD Fio F”VADDD Fg? F” FaiV4lNoFoMultYes10部件名称IntegerMultRk=YesFk准备就绪”可用Rj=No 号未准备就 绪,不可严 表4-25指令MULTD进入写结果级* JAddDivide域结果状态pMpnirm(pHMulAddDivide表4-26是指令DIVD进入写结果级前记分牌的数据结构。此时加法指令已完成,同时除法指令DIVD通过读操 作数级获得操作数F6。最后完成除法指

18、令。表4-26 指令DIVD进入写结果级前记分牌的数据结构表4-26 指令DIVD进入写结果级前记分牌的数据结构高速度、大容量、低价格始终是存储体系的设计目标。40、41、存储器层次结构设计中的四大基本问题:(1)映象方式(2)映象机构(3)替换策略(4)写策略 最基本的Cache/主存映象方式有三种:(1)直接映象(主存中的一信息块只能对应Cache的一个特定行)(2)全关联映象(主存中的一信息块可对应Cache中的任意一行)(3)组关联映象(主存中的第i块可以对应Cache中的某一特定组中的任意一行)42、主存T匚2储器层次结构实例数据Cache有效隹标志块桢地址块内偏移结构如图5-12,

19、当Cache读命中时,Cache的工作流程可分为五大步骤,这五个步骤是在一个CPU时钟周期内完成 的。(1) 来自CPU的地址被分为29位块帧地址和3位块内偏移地址,块帧地址又分成20位标志和9位索引。(2) 根据索引选择Cache中的一个组,读取组内各行标志以判定要访问的数据块是否在Cache中。(3) 块帧地址的标志域与步骤2中读取的两个行标志作相等比较。(4) 假设有一行标志与块帧地址的标志相匹配,则由2选1多路转换器选取相应的数据行。(5) 读出的字送往 CPU。43、按导致Cache失配的原因划分,Cache失配可分成以下三类。这种分析失配的方法也称之为3C模型。(1) 被迫(com

20、pulsory)失配:第一次访问存储块时,由于该块不在Cache中,所以必须首先将此存储块从主存取 入 Cache 中。(2) 容量(capacity)失配:如果Cache不能容纳程序执行过程中所需的所有存储块,那么当程序再次访问到曾装 入 Cache 又已被替换出去的某存储块时,就会出现容量失配。(3) 冲突(conflict)失配:在采用组关联和直接映象方式的Cache中,主存的很多块都将映象到Cache的某一行。 如果因为这个原因,当程序再次访问到曾装入Cache又被替换出去的某存储块时,就会出现冲突失配,也称为碰 撞失配(collision miss)。44、越靠近CPU的存储器容量越

21、小、速度越快、价格越高,离CPU越远的容量越大、速度越慢、价格越低;45、平均存储访问时间(average memory_access time,AMT)平均存储访问时间=命中率+失配率X失配时间表示为:AMT=HT+M X MP46、两级 Cache:(1) 一级Cache,一般做在CPU芯片上(也称片内Cache)。它容量较小,速度与CPU的时钟周期相匹配。(2) 二级Cache,一般做在CPU芯片上(也称为片外Cache),它容量大,速度在CPU和主存之间,以便尽可能 多的访问二级Cache中完成而不必再去访问主存。47、主存组织方式:(1)单体单字主存结构(2)单体多字主存结构(3)多

22、体交叉主存结构48、 输入/输出(简称I/O)设备可分为三大类:数据表示设备、网络通讯设备、存储设备。49、网络通讯设备的种类,按连接处理器的距离分,MPP网、局域网、广域网等;50、根据网上节点数目和它们连接的紧密程度,可以把互连网络分为三种不同的类型:(1) 大规模并行处理器(massively parallel processors,MPP)网络。MPP 网=SAN (store area network)存储区域网(2) 局域网(local area network, LAN)(3) 广域网(wide area network, WAN)51、根据机器最关键部位的指令和由指令引起数据流的并行性,把所有的计算机分为四类:(1) 单指令流,单数据流(SISD)这就是一个单处理器。(2) 单指令流,多数据流(SIMD)同一指令由多个处理器执行,这些处理器使用不同数据流,有各自的数据 内存,但共享一个指令内存和控制处理器(负责存取和发送指令)。处理器通常是专用的,不要求通用性。(3) 多指令流,单数据流(MISD)这种类型的商用机器目前尚未出现,今后也许有可能。(4) 多指令流,多数据流(MIMD)每个处理器存取自己的指令,操作自己的数据。通常采用普通的微处理器。52、现有的MIMD机器基于使用的处理器数目,可以分为两类:(1)集中共享存储器式体系结构(2)分布式存储器的机器

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。