串行通信差分对

串行通信差分对

《串行通信差分对》由会员分享,可在线阅读,更多相关《串行通信差分对(20页珍藏版)》请在装配图网上搜索。

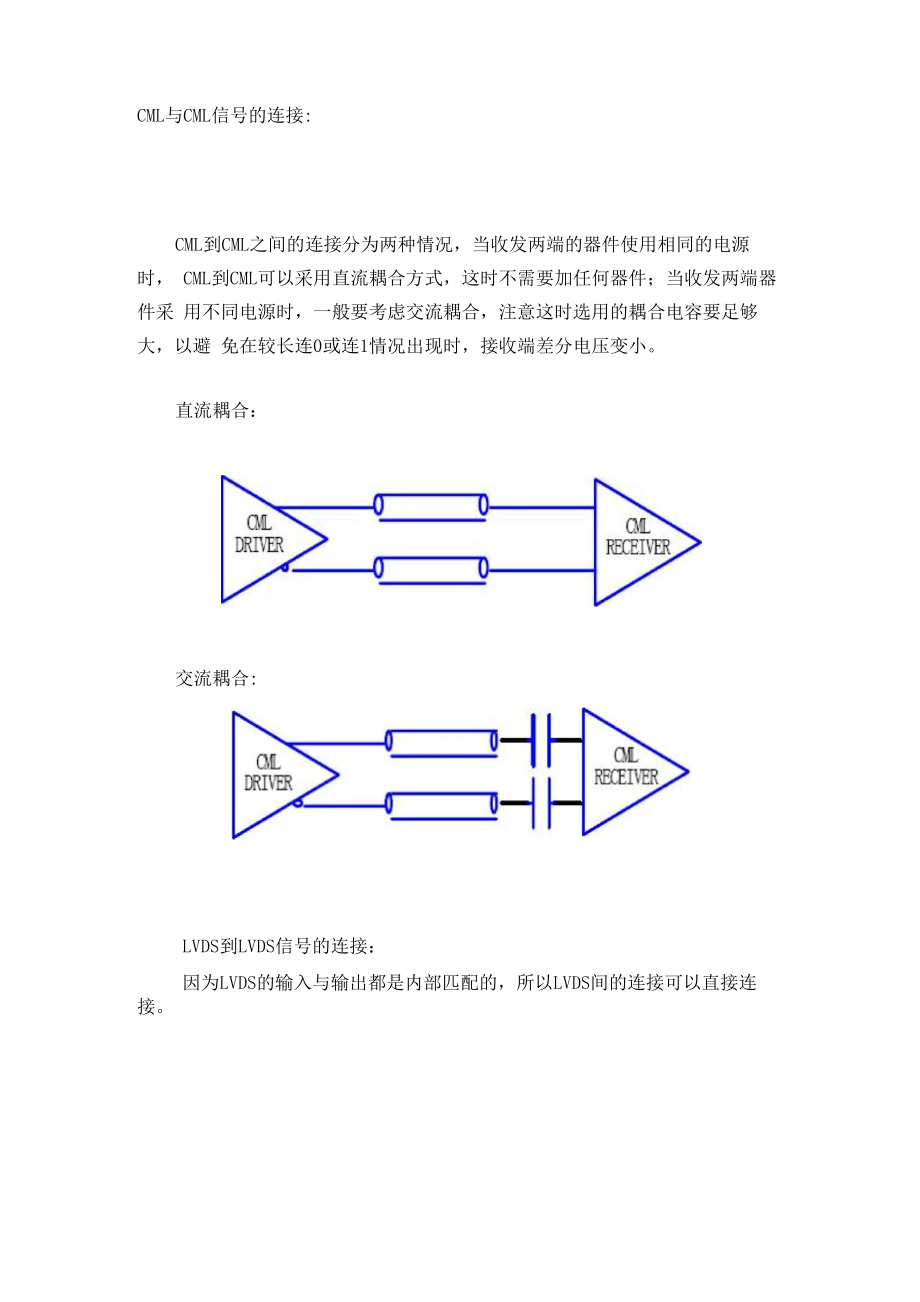

1、CML与CML信号的连接:CML到CML之间的连接分为两种情况,当收发两端的器件使用相同的电源时, CML到CML可以采用直流耦合方式,这时不需要加任何器件;当收发两端器件采 用不同电源时,一般要考虑交流耦合,注意这时选用的耦合电容要足够大,以避 免在较长连0或连1情况出现时,接收端差分电压变小。直流耦合:交流耦合:LVDS到LVDS信号的连接:因为LVDS的输入与输出都是内部匹配的,所以LVDS间的连接可以直接连 接。CML与LVDS的连接:一般情况下,实际应用中没有CML和LVDS进行互联的情况,因为LVDS通 常用作并联数据的传输,数据速率为155MHz, 622MHz,或1.25GHz

2、,而CML常用 来做串行数据的传输,传输速率为2.5GHz或10GHz。作为特殊情况,下面给出 他们互联的解决方案。LVDS到CML的连接:5KQDRIVCML到LVDS的连接:LVDSLVPECL与CML的连接有直流和交流两种耦合方式。交流耦合方式:在LVPECL的两个输出端各加一个到地的偏置电阻,电阻值选取范围可以从 142ohm到200ohm。如果LVPECL的输出信号摆幅大于CML的接收范围,可以在信 号通道上串接一个25ohm的电阻,这时CML输入端的电压摆幅变为原来的0.67 倍。交流耦合方式如下图所示:直流耦合情况:在LVPECL到CML的直流耦合连接方式中需要一个电平转换网络,

3、该电平转 换网络的作用是匹配LVPECL的输出与CML的输入共模电压。一般要求该电平转 换网络引入的损耗要小,以保证LVPECL的输出经过衰减后仍能满足CML输入灵 敏度的要求;另外还要求来自LVPECL端看到的负载阻抗近似为50ohm。下图为 电平转换网络。 Ft3 -+ 5 (J iR3 + 50 Q该电阻转换网络必须满足如下方程式:求解上面的万程组,得到Rl=182ohm,Gain=0.147, Zin=49ohm。直流耦合方式如下图所示:CML即Current Mode Logic,也就是电流模式逻辑,CML电路主要靠电流驱 动,可以说CML是所有高速数据接口形式中最简单的一种,它的输

4、入与输出是 匹配好的,从而减少了外围器件,使用时直接连接就可以,基本上不需要在IC 外面做匹配,此特点使单板硬件设计更简单,单板看起来更简洁,CML的摆幅 较小,功耗比较低。CML输出结构:如上图所示,CML的输出电路形式是一个差分对,该差分对的集电极电阻 为50ohm,输出信号的高低电平切换是靠共发射极差分对的开关控制的,差分对 的发射极到地的恒流源典型值为16mA,假定CML的输出负载为一 50ohm上拉 电阻,则单端CML输出信号的摆幅为VCCVCC-0.4V。在这种情况下,差分输 出信号摆幅为800mV,共模电压为VCC-0.2V。若CML输出采用交流耦合至50ohm 负载,这时的直流

5、阻抗由集电极电阻决定,为50ohm,CML输出工模电压变为 VCC-0.4V,差分信号摆幅仍为800mV。CML波形:OUT+OUT+CML的输入一般都是片内匹配好的,50ohm上拉到VCC,而且大部分是交流 耦合。CML的输入结构:voc50QIN-CML的摆幅一般在600mV-100mV之间,典型值为800mV。CML逻辑参数:CML的优点是功耗低,速度高,但是驱动能力不如LVPECL,传输距离也没 有ECL远。LVPECL/LVDS/CML三种逻辑比较:LVPECL 即 Low Voltage Positive Emitter-Couple Logic,也就是低压正发射极 耦合逻辑,使用

6、3.3V或2.5V电源,LVPECL是由PECL演变而来的,PECL即 Positive Emitter-Couple Logic,也就是正发射极耦合逻辑的意思,使用5.0V电源, 而PECL是由ECL演变而来的,ECL即Emitter-Couple Logic,也就是发射极耦 合逻辑,ECL有两个供电电压VCC和VEE。当VEE接地时,VCC接正电压时,这 时的逻辑称为PECL;当当VCC接地时,VEE接负电压时,这时的逻辑成为NECL, VEE 一般接-5.2V电源;一般狭义的ECL就是指NECL。ECL分类:PECL700 = 5.07, VEE = 0.0VLVPECLVCC = 3.

7、3VJ VEE = O.OV2.5VPECLVCC = 2.5VJ VEE = O.OV2.5VNECLVCC = O.QV. VEE 二 25VLVNECLVCC = O.OV, VEE =-3.3VNECLVCC = O.QV, VEE =-5.0VECL/PECL/LVPECL 逻辑的优点:1. 输出阻抗低(68ohm),输出阻抗高(可以看作无穷大),所以驱动能力特别强, 它可以驱动50130ohm特征阻抗的传输线而交流特性并没有明显的改变。由 于驱动能力强,所以支持更远距离的传输,所以背板走线或长线缆传输基本 上都使用ECL逻辑。2. ECL器件对电压和温度的变化不如TTL和CMOS器

8、件敏感,ECL时钟驱动 器产生的各路时钟的并发性更好,skew更小。3. 相对于同为差分信号的LVDS,ECL支持的速率更高,受工艺的限制,LVDS 的逻辑很少有高于1.5GHz的应用,而ECL可以应用高于10GHz的场合,可 以说,高于5GHz的场合,基本上是ECL和CML的天下。在所有的数字电 路中,ECL的工作速度最高,其延时小于1ns,在中小规模集成电路,高速, 超高速数字系统和设备中应用4. 对传输线阻抗的适应范围更宽。LVDS属于电流型驱动,其终端的100ohm 匹配电阻兼有产生电压的功能。因此,为了不改变信号的摆幅,终端电阻的 阻值必须取100ohm,为了保证较好的信号完整性,L

9、VDS的传输线阻抗也必 须精确控制在50ohm,否则容易产生反射等SI问题。ECL/PECL/LVPECL 逻辑的缺点:跟它的优点一样,ECL的缺点也很明显,那就是功耗大,噪声容限小, 抗干扰能力弱。ECL电路的逻辑摆幅只有0.8V,直流噪声容限只有200mV。可 以说,ECL的高速性能是用高功耗、低噪声容限为代价换来的。PECL的标准输出负载是50ohm至VCC-2V的电平上,在这种负载条件下,OUT+与OUT-的静态电平典型值为VCC-1.3V, OUT+与OUT-的输出电流为 14mA。PECL的输出电路结构:25tss 1怙一EKZIrZRLVPECL芯片内没有直流偏置情况:4.3kii

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

相关资源

更多 数学中的脑筋急转弯趣味数学课堂PPT

数学中的脑筋急转弯趣味数学课堂PPT

广东中山市小榄镇发展改革和统计局招考聘用聘用人员2人模拟试卷【附答案解析】{6}

广东中山市小榄镇发展改革和统计局招考聘用聘用人员2人模拟试卷【附答案解析】{6}

广东中山市政务服务数据管理局所属事业单位公开招聘事业单位人员3人模拟试卷【附答案解析】{8}

广东中山市政务服务数据管理局所属事业单位公开招聘事业单位人员3人模拟试卷【附答案解析】{8}

福州市仓山区市场监督管理局招考1名编外人员模拟试卷【附答案解析】(6)

福州市仓山区市场监督管理局招考1名编外人员模拟试卷【附答案解析】(6)

江苏省射阳县面向全国部分高校和境外世界名校引进202名优秀毕业生工作模拟试卷【附答案解析】【2】

江苏省射阳县面向全国部分高校和境外世界名校引进202名优秀毕业生工作模拟试卷【附答案解析】【2】

福州市仓山区市场监督管理局招考1名编外人员模拟试卷【附答案解析】(8)

福州市仓山区市场监督管理局招考1名编外人员模拟试卷【附答案解析】(8)

福州市仓山区城市管理局招考12名编外人员模拟试卷【附答案解析】(3)

福州市仓山区城市管理局招考12名编外人员模拟试卷【附答案解析】(3)

福州市公共法律服务指挥中心招考1名工作人员模拟试卷【附答案解析】(0)

福州市公共法律服务指挥中心招考1名工作人员模拟试卷【附答案解析】(0)

纪念五四运动00周年大会精神学习心得

纪念五四运动00周年大会精神学习心得

![福建厦门市湖滨小学教师招考聘用模拟试卷【附答案解析】[7]](/Images/s.gif) 福建厦门市湖滨小学教师招考聘用模拟试卷【附答案解析】[7]

福建厦门市湖滨小学教师招考聘用模拟试卷【附答案解析】[7]