电子科大毕设

电子科大毕设

《电子科大毕设》由会员分享,可在线阅读,更多相关《电子科大毕设(13页珍藏版)》请在装配图网上搜索。

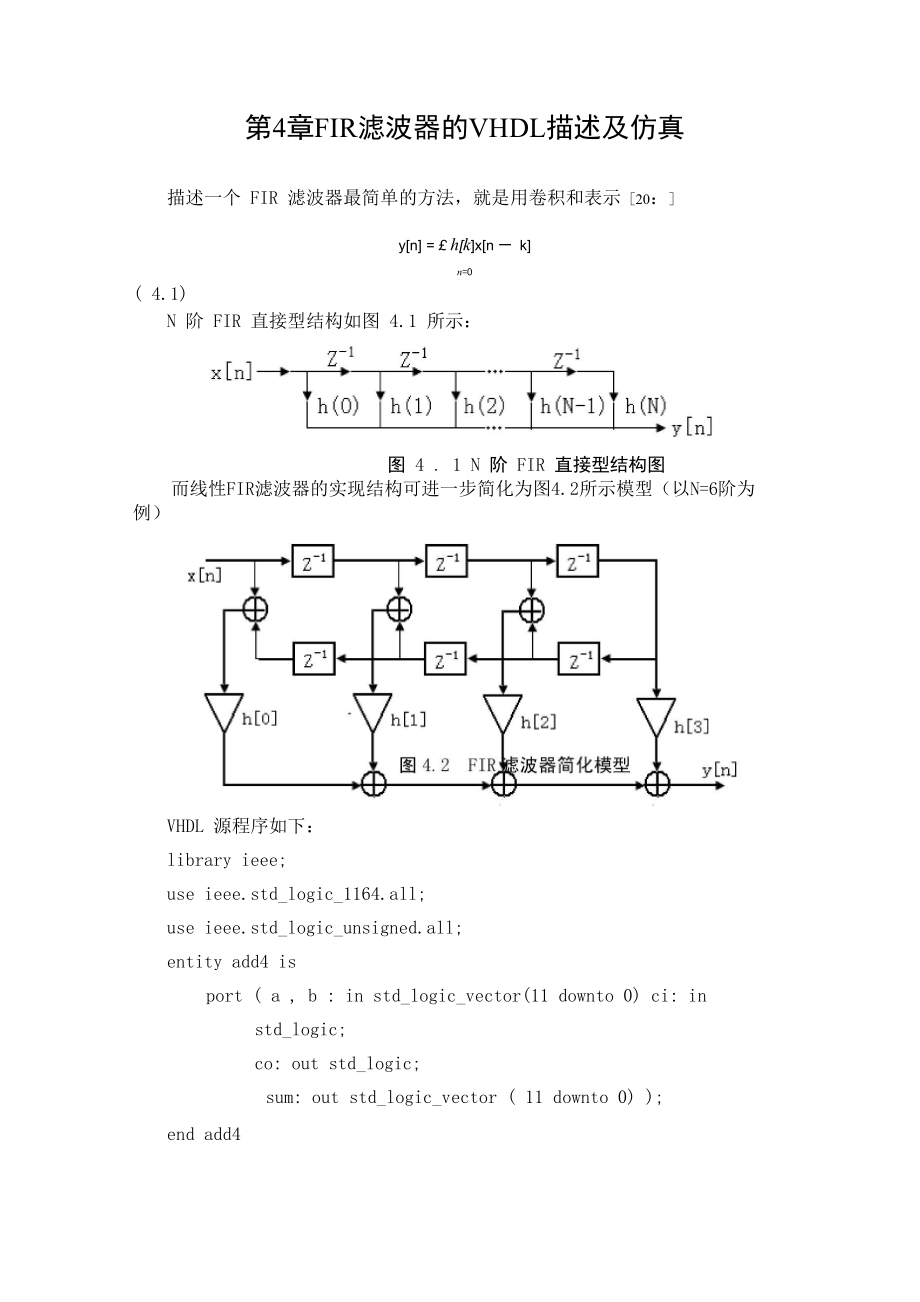

1、第4章FIR滤波器的VHDL描述及仿真描述一个 FIR 滤波器最简单的方法,就是用卷积和表示20:yn = hkxn 一 kn=0( 4.1)N 阶 FIR 直接型结构如图 4.1 所示:图 4 . 1 N 阶 FIR 直接型结构图而线性FIR滤波器的实现结构可进一步简化为图4.2所示模型(以N=6阶为 例)VHDL 源程序如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity add4 isport ( a , b : in std_logic_vector(11 downto 0)

2、 ci: in std_logic;co: out std_logic;sum: out std_logic_vector ( 11 downto 0) );end add4architecture behav of add4 issignal sint : std_logic_vector ( 12 downto 0);signal aa, bb: std_logic_vector ( 12 downto 0);beginaa=0&a;- 将 4 位加数矢量扩为 5 位,为进位提供空间bb=0&b;- 将 4 位被加数矢量扩为 5 位,为进位提供空间sint=aa+bb+ci;-std_lo

3、gic_unsigned 包定义了“+”运算sum=sint (11 downto 0);co0);pa(11 downto 0):=signed(ain); a_1:=0;for i in 1 to 12 loopcase std_logic_vector(pa(0),a_1) iswhen 01 = p:=p+signed(bin);when 10 = p:=p-signed(bin); when others = null;end case;a_1:=pa(0); pa:=shift_right(pa,1);end loop; qout=std_logic_vector(pa(23 do

4、wnto 0);end process;end rtl;该乘法器的原理图如图 4.7:r mul12ain11.Oqout23.0bin11.Oi inst:图 4 . 7 12 位乘法器原理图通过仿真得到 12位乘法器波形如下图 4.8所示:图4.8 乘法器仿真图此时,ain=-l,bin=-l,输出qout= 1,显然是正确的。4.1.4 延时器的实现延时器可以用寄存器实现, VHDL 源程序如下: library ieee;use ieee.std_logic_1164.all; entity delayer isport(a: in std_logic_vector(11 downto

5、 0);clk:in std_logic;reset:in std_logic;b: out std_logic_vector(11 downto 0);end entity delayer;architecture rtl of delayer isbeginprocess(clk,reset)beginif reset=1 then b=000000000000;-异步复位elsif clkevent and clk=1 then-时钟上升沿b=a;end if;end process;end architecture rtl;延时器的基本逻辑单元是上升沿触发的 D 触发器,其原理图如下图

6、 4.9 所示:delaytjr图4.9 延时器原理图仿真波形如4.10所示:iu.u f ruirnui.imuivdi.OdlLILdiTieVai-200elkrese tH aB 000CJ 15H bB 000CNd右IDI I IIIIU Ddl.L1111I1111I(000000000000 ;:000000000001 X 000000000011 X 000000000111、.I0000000J0000000000000001 X 000000000011 )foJ ps20. 0 ns40.0 ns60. 0 ns80.020.0 nsJ图4.10 延时器仿真图4.2

7、FIR 带通滤波器的顶层实现利用上面所编写的 12位加法器,24位加法器,12位乘法器及延时器,我们 可以组合出所需的 FIR 带通滤波器。程序中主要是运用元件例化语句来实现一个 结构化的描述,系统函数通过调用 12 位加法器,24 位加法器,12 位乘法器及延 时器等模块来 FIR 带通滤波器。具体的调用层次见图 4.11 所示。图4. 11 FIR滤波器的结构图滤波器顶层源程序如下。顶层源程序;library ieee;- 库包说明use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.numeric_std

8、.all;entity filter isport( x: in std_logic_vector (11 downto 0); - 端口说明clk: in std_logic; reset: in std_logic; y: out std_logic_vector (23 downto 0);end entity filter;architecture stru of filter is component add12 is-12 位加法器port ( a , b : in std_logic_vector(11 downto 0) ;ci: in std_logic;co: out st

9、d_logic;sum: out std_logic_vector ( 11 downto 0) );end component add12;component add24 is-24 位加法器port ( a , b : in std_logic_vector(23 downto 0) ;ci: in std_logic;co: out std_logic;sum: out std_logic_vector ( 23 downto 0) );end component add24;component mul12 is-12 位乘法器port(ain: in std_logic_vector(

10、11 downto 0);bin: in std_logic_vector(11 downto 0); qout: out std_logic_vector(23 downto 0);end component mul12;component delayer is- 延时器port(a: in std_logic_vector(11 downto 0);clk:in std_logic;reset:in std_logic;b: out std_logic_vector(11 downto 0);end component delayer;type delaytype is array (0

11、to 21) of std_logic_vector(11 downto 0); -自定义数据类型type sumtype is array (0 to 10) of std_logic_vector(11 downto 0); type multype is array (0 to 10) of std_logic_vector(23 downto 0); signal delay:delaytype;- 定义信号signal sum:sumtype;signal mul,sum2:multype;constant h:sumtype:=(000000100011,- 系统函数1111110

12、10010, 111111110011, 111111011000, 000000110110,001100010110, 111110101010,000110101110, 111111101000,110000011100, 110011100100);begin delay(0)=x; g1:for i in 0 to 20 generate de:delayer port map(delay(i),clk,reset,delay(i+1); end generate g1;g2:for i in 0 to 10 generatead12:add12 port map(delay(i)

13、,delay(21-i),0,open,sum(i); end generate g2;g3:for i in 0 to 10 generate mu:mul12 port map(sum(i),h(i),mul(i);end generate g3; sum2(0)=mul(0); g4:for i in 0 to 9 generate ad24:add24 port map(sum2(i),mul(i+1),0,open,sum2(i+1);end generate g4; y=sum2(10);end architecture stru;点击 Files 下的 Create/Update

14、Create Symbol Files for Current File,可以生成滤波器模块及各独立元件(加法器,乘法器,延时器等)的模块。可建图4. 12 FIR滤波器模型图为了验证生成的模型是否满足设计的性能指标,必须进行时序仿真,而其中 最有效最全面的方法就是加入一个冲激信号,看滤波器的单位冲激响应。让输入 x在第一个时钟有效沿为12位的二进制脉冲,即冲激信号。编辑波形文件,进 行仿真,得到仿真报告如图 4.13 下:S i mill ation Rep nr t冒? =| Le g:il No t i 亡 mFlow SuiTim:ry Flow Emtt-SimulatorSH Si

15、mula tor Suirim srySH S i mill aEmtti ngsSimiilati un W ave urm e Si mill atd INI Usage Si mill at or Mess age eTypeValue1S i mill a tiun St:r t Timed.蔗2S i mill a tiun End Time50. 0 he3S i mill a tiun Hmt li e t Si ze2873 nodes4S i mill a t i un C overage31.87 %5T a t al NiJiTib er u f Tr otle i t

16、i unE12201SiBulator SiuiBary图 4 . 13 仿真报告当输入为任意值时仿真波形图如4.14所示:N:=LiTie127.29 ns128. 44 ns129.6 ns130.75 ns131iiioelkrese t田X田y1 1 1 1 11 1 1聆1薛2000000001100 )( 000000001101Cy 15l30X0l31 Xol_W0iYX图4. 14总仿真波形图 | H Pointer:Interval:Master Time Bar:9.825 ns128.57 ns118.75 nsStart:N:=ifTie0elkplr ese tH

17、xJ/15田yn jrL_nL_nL_RL_n_JrL_nL_nL_L_TUL nL nL_nL_r15 255)c00255 255255)c00010.0 ns12.875 rLS当输入为高电平或低电平时仿真波形图如4.15所示:图 4 . 15 总仿真波形图从波形可以看出:当输入为任意值时,有选择性的输出。当为输入为高电平 时输出为高电平:当输入为低电平时输出为低电平。可以看出符合设计要求。在 进行系统仿真时,有以下几点体会:(1) 系统模块化分的重要性对于一个系统的开发,最初的模块划分是非常重要的。随着系统的复杂度的 增大,模块划分对于系统的后续开发显示出越来越大的重要性。随着自顶向下

18、设 计方法的广泛采用,把一个系统划分为几个子模块,然后各个子模块分别设计的 方法也越来越多的被广大设计者所使用。一个系统模块划分的好坏,模块间接口 设计得是否合理,将直接影响到整个系统的开发,甚至会决定系统开发的成功与 否。一个良好的系统模块划分,合理的模块间接口设计会使后续的系统开发事半 功倍。反之则使得后续的系统开发步履艰难。因而,系统开发人员把越来越多的 时间和精力投入到系统的模块划分和接口设计当中。具体到本设计的开发,由于 开发的经验不足,模块间的接口设计不是很合理,等到开发到具体的子模块时, 才发现了问题,使得系统综合与仿真无法进行下去,从而不得不重新设计模块间 的接口,耽误了整个系

19、统开发的速度。(2) 器件延时对系统实现的影响器件延时对一个实际系统来说是客观存在的,它对系统实现的影响是不可避 免的,同时也是很难预测的。因而在实现系统时,要想把器件对系统实现的影响 完全消除)L乎是不可能的。如果完全忽视它,很可能会导致系统无法正确实现。 比较好的做法是把器件延时的影响控制在一个系统可以允许的范围内,使得它不 至于对系统实现产生决定性的影响。在本系统的开发过程当中,刚开始由于对器 件延时的影响考虑不足,所以导致了程序仿真结果与预先设想的不一致,使得系 统仿真无法实现预定的功能。后经过修改程序,考虑了器件延时对同步的影响, 才最终实现了系统预定的功能。可见,考虑器件延时的影响

20、对一个系统设计者来 说是非常重要的。4.3 硬件下载将编译产生的SOF格式配置文件配置进FPGA中。硬件测试步骤如下:(1)打开编译好的文件,将实验系统和并口通信线接好,打开电源。先对引 脚进行锁定。再选择ToolProgrammer命令,在Mode列表中选JTAG,单击左 侧的Add File按钮,手动选择配置文件。(2) 设置编程器。单击Hardware Setup按钮在弹出的Hardware Setup对话 框中双击ByteBlasterMV,单击Close即可。(3) 选择编程器。根据试验箱选择编程口。本次设计选择ByBtil,最后单 击 Start 即可,当 Programme 显示出 100%时,编译成功。( 4)硬件测试。根据仿真结果输入脉冲。观察结果正确。下载成功。联想商务网 htt p:/www .timeto pro tect .com cjbl3x

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 沪教牛津英语六年级上册Module3单元全套ppt课件

- 沪科版《声音的产生与传播》ppt课件

- 店铺数据分析课件

- 美国研究文献资源指南.课件

- 绿色夏天清新汇报课件

- 美食咖啡下午茶餐饮课件

- 微生物学实验-1-口腔微生物的染色观察与显微镜油镜的使用;细菌的革兰氏染色教学课件

- 沪教版(上海)七年级数学第二学期ppt课件152(2)直角坐标平面内点的运动

- 店铺报告模本教学课件

- 民兵组织建设课件

- 沪教版(上海)七年级数学第二学期ppt课件152(1)直角坐标平面内点的运动

- 沪教版牛津英语小学二年级上学期期末复习句型课件

- 沪教版地理七年级上册42黄河课件

- 沪教版五年级数学下册《正方体、长方体的表面积2》ppt课件

- 微生物学基础知识培训课件