组成原理考研真题及解答

组成原理考研真题及解答

《组成原理考研真题及解答》由会员分享,可在线阅读,更多相关《组成原理考研真题及解答(9页珍藏版)》请在装配图网上搜索。

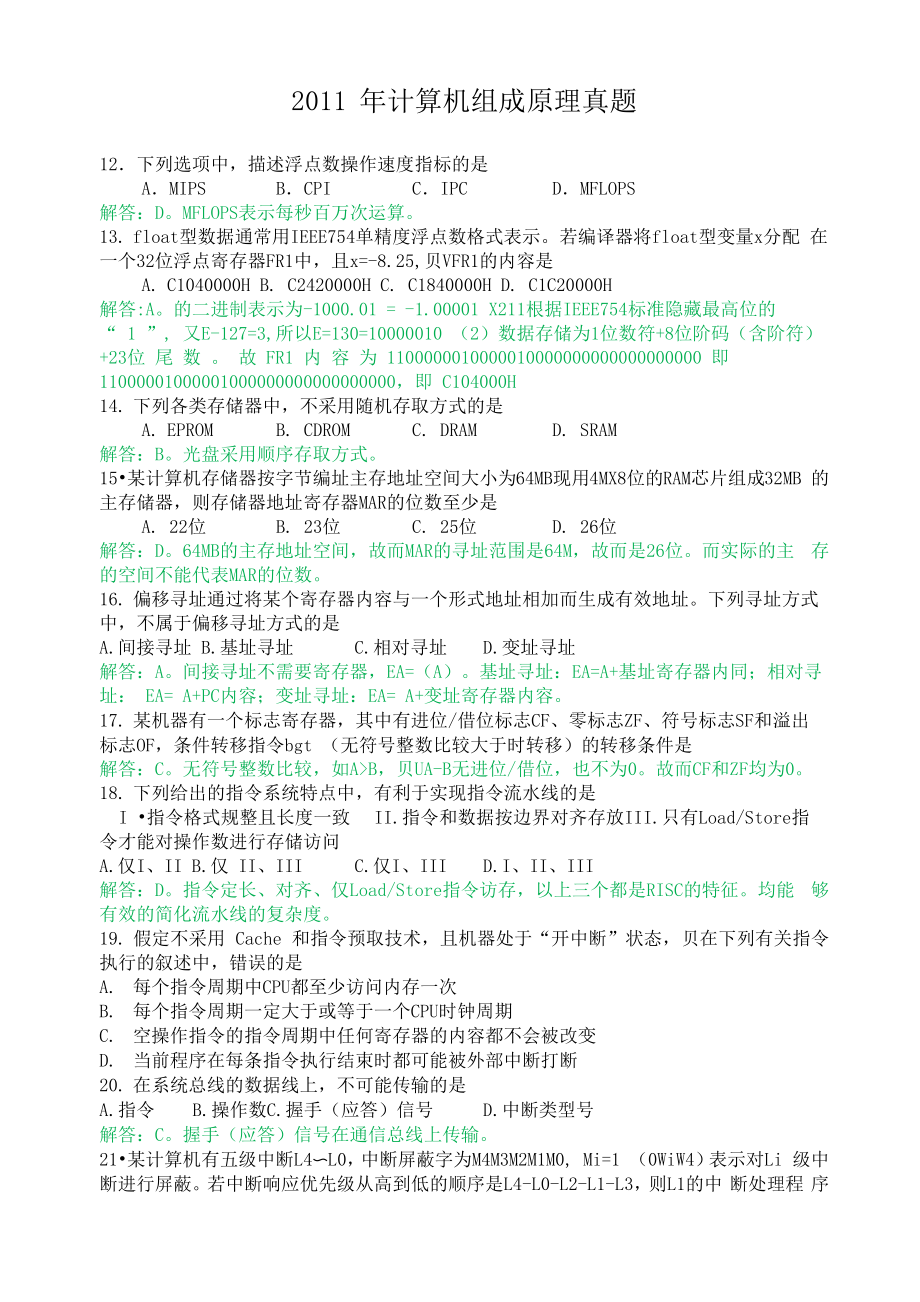

1、2011 年计算机组成原理真题12下列选项中,描述浮点数操作速度指标的是AMIPSBCPICIPCDMFLOPS解答:D。MFLOPS表示每秒百万次运算。13. float型数据通常用IEEE754单精度浮点数格式表示。若编译器将float型变量x分配 在一个32位浮点寄存器FR1中,且x=-8.25,贝VFR1的内容是A. C1040000H B. C2420000H C. C1840000H D. C1C20000H解答:A。的二进制表示为-1000.01 = -1.00001 X211根据IEEE754标准隐藏最高位的“ 1 ”, 又E-127=3,所以E=130=10000010 (2

2、)数据存储为1位数符+8位阶码(含阶符)+23位 尾 数 。 故 FR1 内 容 为 1100000010000010000000000000000000 即 11000001000001000000000000000000,即 C104000H14. 下列各类存储器中,不采用随机存取方式的是A. EPROMB. CDROMC. DRAMD. SRAM解答:B。光盘采用顺序存取方式。15某计算机存储器按字节编址主存地址空间大小为64MB现用4MX8位的RAM芯片组成32MB 的主存储器,则存储器地址寄存器MAR的位数至少是A. 22位B. 23位C. 25位D. 26位解答:D。64MB的主存

3、地址空间,故而MAR的寻址范围是64M,故而是26位。而实际的主 存的空间不能代表MAR的位数。16. 偏移寻址通过将某个寄存器内容与一个形式地址相加而生成有效地址。下列寻址方式 中,不属于偏移寻址方式的是A.间接寻址 B.基址寻址C.相对寻址D.变址寻址解答:A。间接寻址不需要寄存器,EA=(A)。基址寻址:EA=A+基址寄存器内同;相对寻址: EA= A+PC内容;变址寻址:EA= A+变址寄存器内容。17. 某机器有一个标志寄存器,其中有进位/借位标志CF、零标志ZF、符号标志SF和溢出 标志OF,条件转移指令bgt (无符号整数比较大于时转移)的转移条件是解答:C。无符号整数比较,如A

4、B,贝UA-B无进位/借位,也不为0。故而CF和ZF均为0。18. 下列给出的指令系统特点中,有利于实现指令流水线的是I 指令格式规整且长度一致II.指令和数据按边界对齐存放III.只有Load/Store指令才能对操作数进行存储访问A.仅I、II B.仅 II、IIIC.仅I、IIID.I、II、III解答:D。指令定长、对齐、仅Load/Store指令访存,以上三个都是RISC的特征。均能 够有效的简化流水线的复杂度。19. 假定不采用 Cache 和指令预取技术,且机器处于“开中断”状态,贝在下列有关指令 执行的叙述中,错误的是A. 每个指令周期中CPU都至少访问内存一次B. 每个指令周

5、期一定大于或等于一个CPU时钟周期C. 空操作指令的指令周期中任何寄存器的内容都不会被改变D. 当前程序在每条指令执行结束时都可能被外部中断打断20. 在系统总线的数据线上,不可能传输的是A.指令B.操作数C.握手(应答)信号D.中断类型号解答:C。握手(应答)信号在通信总线上传输。21某计算机有五级中断L4L0,中断屏蔽字为M4M3M2M1M0, Mi=1 (0WiW4)表示对Li 级中断进行屏蔽。若中断响应优先级从高到低的顺序是L4-L0-L2-L1-L3,则L1的中 断处理程 序中设置的中断屏蔽字是A11110 B01101 C00011 D01010解答:D。高等级置0表示可被中断,比

6、该等级低的置1表示不可被中断。22.某计算机处理器主频为50MHz,采用定时查询方式控制设备A的I/O,查询程序运行 一次所用的时钟周期数至少为500。在设备A工作期间,为保证数据不丢失,每秒需对其 查询至少200次,则CPU用于设备A的I/O的时间占整个CPU时间的百分比至少是 A0.02% B0.05% C0.20% D0.50%解答:C。每秒200次查询,每次500个周期,则每秒最少200X500= 100000个周期,100000 F50M=0.20%。43. (11分)假定在一个8位字长的计算机中运行如下类C程序段:unsignedintx=134;unsignedinty=246;

7、intm=x;intn=y;unsignedintz1=x-y;unsignedintz2=x+y;intk1=m-n;intk2=m+n;若编译器编译时将8个8位寄存器R1R8分别分配给变量x、y、m、n、z1、z2、k1和k2。请回答下列问题。(提示:带符号整数用补码表示)(1)执行上述程序段后,寄存器R1、R5和R6的内容分别是什么?(用十六进制表示)(2)执行上述程序段后,变量m和k1的值分别是多少?(用十进制表示)(3)上述程序段涉及带符号整数加 /减、无符号整数加/减运算,这四种运算能否利用同一个加法器辅助 电路实现?简述理由。(4)计算机内部如何判断带符号整数加/减运算的结果是否

8、发生溢出?上述程序段中,哪些带符号整数运 算语句的执行结果会发生溢出?解答:( 1 ) R1=134=86H,R5=90H,R6=7CH;134=10000110B=86H ; x-y=10000110B-11110110B=10010000B=90H ; x+y=10000110B+11110110B=01111100B (溢出)( 2 ) m=-122,k1=-112m=1OOOO11OB,做高位为符号位,则m的原码为11111010B=-122; n=1111O11OBn的原码为 1OOO1OO1=-1O; k1=m-n=-112。(3)无符号数和有符号数都是以补码的形式存储,加减运算没

9、有区别不考虑溢出情况时), 只是输出的时候若是有符号数的最高位是符号位。减法运算求-x补的时候,是连同符号位一起按位取反末位加1,但是如果有溢出情况,这两者是有区别的,所以可以利用同一个加法器实现,但是溢出判断电路不同。(4)判断方法是如果最高位进位和符号位的进位不同,则为溢出;“intk2=m+n; ”会溢出; 三种方法可以判断溢出,双符号位、最高位进位、符号相同操作数的运算后与原操作 数的符号不同则溢出。44. (12分)某计算机存储器按字节编址,虚拟(逻辑)地址空间大小为16MB,主存(物理)地址空间大 小为1 MB,页面大小为4KB; Cache采用直接映射方式,共8行;主存与Cach

10、e之间交换的块大小为32B。系统运行到某一时刻时页表的部分内容和Cache的部分内容分别如题44-a图、题4 4-b图所示,图中页 框号及标记字段的内容为十六进制形式。请回答下列问题。1)虚拟地址共有几位,哪几位表示虚页号?物理地址共有几位,哪几位表示页框.物理页号)?(2)使用物理地址访问Cache时,物理地址应划分成哪几个字段?要求说明每个字 段的位数及在物理地址中的位置。(3)虚拟地址001C60H所在的页面是否在主存中?若在主存中,则该虚拟地址对应 的物理地址是什么?访问该地址时是否Cache命中?要求说明理由。(4)假定为该机配置一个4路组相联的TLB共可存放8个页表项,若其当前内容

11、(十 六进制)如题44-c图所示,则此时虚拟地址024BACH所在的页面是否存在主存题44-c图TLB的部分内容解答: .1) 24位、前12位;20位、前8位。16M=224故虚拟地址24位,4K=212,故页内地址12位,所以虚页号为前12位;1M=22O 故物理地址20位, 20-12=8,故前8位为页框号。(2)主存字块标记(12bit)cache字块标记(3bit)字块内地址(5bit)物理地址20位,其中,块大小为32B=25B故块内地址5位;cache共8行,8=23,故 字块标记为3位; 20-5-2=12,故主存字块标记为12位。(3)在主存中,04C60H,不命中,没有04

12、C的标记字段001C60H中虚页号为001H=1,查页表知其有效位为1,在内存中;该物理地址对应的 也表项中,页框号为04H故物理地址为04C60H;物理地址04C60H在直接映射方式下,对应 的行号为4,有效位为1但是标记位为064HH04CH故不命中。(4)在012的那个标记是对的。 思路:标记11位组地址1位页内地址12位,前12位为000000100100,组地址位为0,第0组中存在标记为012的页,其页框号为1F,故024BACH所在的页面存在主存中。2012 年计算机组成原理真题12. 假定基准程序A在某计算机上的运行时间为100秒,其中90秒为CP U时间,其余为I/O时 间。若

13、CPU速度提高50%, I/O速度不变,则运行基准程序A所耗费的时间是A. 55 秒 B.6 0 秒 C.65 秒 D.70 秒13. 假定编译器规定in t和shor t类型长度占32位和16位,执行下列C语言语句 unsignedshortx=65530;unsignedinty=x;得到y的机器数为A.00007FFAB.0000FFFAC.FFFF7FFAD.FFFFFFFA14. float类型(即IEEE754单精度浮点数格式)能表示的最大正整数是A.2126-2103B.2127-2104C.2127-2103D.2128-210415. 某计算机存储器按字节编址,采用小端方式存

14、放数据。假定编译器规定int和short型长 度分别为32位和16位,并且数据按边界对齐存储。某C语言程序段如下:structinta;charb;shortc;record;record.a=273;若record变量的首地址为0Xc008,则低至0Xc008中内容及record.c的地址分别为A.0x00、0xC00DB.0x00、0xC00EC.0x11、0xC00D.0x11、0xC00E16. 下列关于闪存(FlashMemory)的叙述中,错误的是A. 信息可读可写,并且读、写速度一样快B. 存储元由MOS管组成,是一种半导体存储器C. 掉电后信息不丢失,是一种非易失性存储器D.

15、采用随机访问方式,可替代计算机外部存储器17. 假设某计算机按字编址,Cache有4个行,Cache和主存之间交换的块为1个字。若Cache 的内容初始为空,采用2路组相联映射方式和LRU替换算法。当访问的主存地址依次为 0,4, & 2,0,6,&6,4,8 时,命中 Cache 的次数是A.1B.2C.3D.418. 某计算机的控制器采用微程序控制方式,微指令中的操作控制字段采用字段直接编码 法,共有33个微命令,构成5个互斥类,分别包含7、 3、 12、 5和6个微命令,则操作控制 字段至少有A.5 位 B.6 位 C.15 位 D.33 位19某同步总线的时钟频率为100MHz,宽度为

16、32位,地址/数据线复用,每传送一次地址 或者数据占用一个时钟周期。若该总线支持突发(猝发)传输方式,则一次“主存写”总线 事务传输128位数据所需要的时间至少是A.20nsB.40nsC.50nsD.80ns20. 下列关于USB总线特性的描述中,错误的是A.可实现外设的即插即用和热拔插B.可通过级联方式连接多台外设C.是一种通信总线,连接不同外设D.同时可传输2位数据,数据传输率高21. 下列选项中,在I/O总线的数据线上传输的信息包括I.I/ O接口中的命令字II.I/ O接口中的状态字III .中断类型号A.仅I、IIB.仅I、IIIC.仅II、IIID.I、II、III22. 响应外

17、部中断的过程中,中断隐指令完成的操作,除保护断点外,还包括I关中断II.保存通用寄存器的内容Ill.形成中断服务程序入口地址并送PCA.仅I、IIB.仅I、IIIC.仅II、IIID.I、II、III参考答案:12-15DBDD16-20ACCCD21-22DB43. (11分)假设某计算机的CPU主频为80MHz, CPI为4,并且平均每条指令访存1.5次,主 存与Cache之间交换的块大小为16B, Cache的命中率为99%,存储器总线宽度为32位。请回 答下列问题。(1)该计算机的MIPS数是多少?平均每秒Cache缺失的次数是多少?在不考虑DMA传送的 情况下。主存带宽至少达到多少才

18、能满足CP U的访存要求?(2)假定在Cache缺失的情况下访问主存时,存在0.0005%的缺页率,贝0CPU平均每秒产生 多少次缺页异常?若页面大小为4KB,每次缺页都需要访问磁盘,访问磁盘时DMA传送采用 周期挪用方式,磁盘I/O接口的数据缓冲寄存器为32位,则磁盘I/O接口平均每秒发出的DMA 请求次数至少是多少?(3)CPU和DMA控制器同时要求使用存储器总线时,哪个优先级更高?为什么?(4)为了提高性能,主存采用4体低位交叉存储器,工作时每1/4周期启动一个存储体, 每个存储体传送周期为50ns,则主存能提供的最大带宽是多少?【解析】(1)MIPS=CPU主频xl0-6/CPI=80

19、M/4=20;平均每条指令访存1.5次,Cache的命中 率为99%,故每秒Cache缺失的次数=20Mx1.5x1%=300000 (次);(2)在不使用DMA传送的情况下,所有主存的存取操作都需要经过CPU,所以主存带宽 至少应为20M/sx1.5x4B=120MB/s。由于页式虚拟存储方式的页表始终位于内存,则产生缺页异常的只能是指令的访存。每秒 产生缺页中断20M/sx1.5x0.0005%=15 0次。因此平均每秒发出的DMA请求次数至少是 150x4KB/4B=150K 次。(3)优先响应DMA请求。DMA通常连接高速I/O设备,若不及时处理可能丢失数据。(4)当4体低位交叉存储器

20、稳定运行时,能提供的最大带宽为4x4B/50ns=320MB/s。44. (12分)某16位计算机中,带符号整数用补码表示,数据Cache和指令Cache分离。题44 表给出了指令系统中部分指令格式,其中Rs和Rd表示寄存器,mem表示存储单元地址,(x) 表示寄存器x或存储单元x的内容。题44表指令系统中部分指令格式名称指令的汇编格式指令功能加法指令ADDRs, Rd(Rs)+(Rd)-Rd算术/逻辑左移SHLRd2*(Rd)-Rd算术右移SHRRd(Rd)/2-Rd取数指令LOADRd, mem(mem)-Rd存数指令STORERs, memRs-(mem)该计算机采用5段流水方式执行指令

21、,各流水段分别是取指(IF)、译码/读寄存器(ID)、 执行/计算有效地址(EX)、访问存储器(M)和结果写回寄存器(WB),流水线采用“按 序发射,按序完成”方式,没有采用转发技术处理数据相关,并且同一寄存器的读和写操作 不能在同一个时钟周期内进行。请回答下列问题。(1)若int型变量x的值为-513,存放在寄存器R1中,则执行“WHLR1”后,R1中的内容是多 少?(用十六进制表示)(2)若在某个时间段中,有连续的4条指令进入流水线,在其执行过程中没有发生任何阻 塞,则执行这4条指令所需的时钟周期数为多少?(3)若高级语言程序中某赋值语句为x=a+b, x、a和b均为int型变量,它们的存

22、储单元地 址分别表示为x、a和b。该语句对应的指令序列及其在指令流中的执行过程如题44图所 示。I1LOADR1,aI2LOADR2,bI1ADDR1,R2 I2STORER2,x 题44图指令序列及其执行过程示意图(4)若高级语言程序中某赋值语句为x=x*2+a, x和a均为unsignedint类型变量,它们的存 储单元地址分别表示为x、a,则执行这条语句至少需要多少个时钟周期?要求模仿题44 图画出这条语句对应的指令序列及其在流水线中的执行过程示意图。【解析】(1)x的机器码为X补=111111011111B,即指令执行前(R1) =FDFFH,右移1位后位 11111110111111

23、11B,即指令执行后(R1) =FEFFH。(2)至少需要4+(51 ) =8个时钟周期数。(3)I3的ID段被阻塞的原因:因为13与11和12都存在数据相关,需等到11和12将结果写回寄 存器后,13才能读寄存器内容,所以13的ID段被阻塞。14的IF段被阻塞的原因:因为14的 前一条指令13在ID段被阻塞,所以14的IF段被阻塞。(4)因2*x操作有左移和加法两种实现方法,故x=x *2+a对应的指令序列为2013 年计算机组成原理真题12. 某计算机主频为1.2GHz,其指令分为4类,它们在基准程序中所占比例及CPI如下表所 示指令类型所占比例CPIA50%2B20%3C10%4D20%

24、5该机的MIPS数是A.100B.200C.400D.60012. C解析:基准程序的CPI=2*0.5+3*0.2+4*0.1+5*0.2=3?,计算机的主频为 1.2GHa, 为 1200MHz,该机器的是MIPS为 1200/3=400。13. 某数采用IEEE754单精度浮点数格式表示为C6400000H,则该数的值是A.-1.5x2i3B.-1.5x2i2C.-0.5xx2i3D.-0.5x2i213. A解析:IEEE754单精度浮点数格式为C6400000H,二进制格式为 11000110010000000000000000000000,转换为标准的格式为:因此,浮点数的值为-1

25、.5X2】314. 某字长为8位的计算机中,已知整型变量x、y的机器数分别为x补=11110100, y补 = 10110000。若整型变量z=2*x+y/2,贝贬的机器数为A.B.00100100C.10101010D. 溢出14. A解析:将x左移一位,y右移一位,两个数的补码相加的机器数为15. 用海明码对长度为8位的数据进行检/纠错时,若能纠正一位错。则校验位数至少为A.2B.3C.4D.516. 某计算机主存地址空间大小为256MB,按字节编址。虚拟地址空间大小为4GB,采用页 式存储管理,页面大小为4KB, TLB (快表)采用全相联映射,有4个页表项,内容如下表 所示。有效位标记

26、页框号0FF180H0002H13FFF1H0035H002FF3H0351H103FFFH0153H则对虚拟地址03FFF180H进行虚实地址变换的结果是 A.0153180HB.0035180HC.TLB缺失D.缺页16. A解析:虚拟地址为03FFF180H,其中页号为03FFFH,页内地址为180H,根据题目中给 出的页表项可知页标记为03FFFH所对应的页框号为0153H,页框号与页内地址之和即为物 理地址0153180H。17假设变址寄存器R的内容为1000H,指令中的形式地址为2000H ;地址1000H中的内容为 2000H,地址2000H中的内容为3000H,地址3000H中

27、的内容为4000H,则变址寻址方式下访 问到的操作数是A.1000HB.2000HC.3000HD.4000H17. D解析:根据变址寻址的主要方法,变址寄存器的内容与形式地址的内容相加之后,得 到操作数的实际地址,根据实际地址访问内存,获取操作数4000H。18. 某CPU主频为1.03GHz,采用4级指令流水线,每个流水段的执行需要1个时钟周期。假 定CPU执行了 100条指令,在其执行过程中,没有发生任何流水线阻塞,此时流水线的吞吐 率为A. 0.25x109条指令/秒B. 0.97X109条指令/秒C. 1.0x109条指令/秒D. 1.03X109条指令/秒18. C解析:采用4级流

28、水执行10 0条指令,在执行过程中共用4+(100-1)=103个时钟周期。CPU的主频是1.03GHz,也就是说每秒钟有1.03G个时钟周期。 流水线的吞吐率为1.03G *100/103=1.0*109条指令/秒。19. 下列选项中,用于设备和设备控制器(1/O接口)之间互连的接口标准是A.PCIB.USBC.AGPD.PCI-Express19. B解析:设备和设备控制器之间的接口是USB接口,其余选项不符合,答案为B。20. 下列选项中,用于提高RAID可靠性的措施有I.磁盘镜像II.条带化III.奇偶校验IV增加Cache机制A.仅I、IIB.仅I、IIIC.仅I、III和IVD.仅

29、II、III和IV20. B解析:能够提高RAID可靠性的措施主要是对磁盘进行镜像处理和进行奇偶校验。其余 选项不符合条件。21某磁盘的转速为10000转/分,平均寻道时间是6ms,磁盘传输速率是20MB/s,磁盘控制 器延迟为0.2ms,读取一个4KB的扇区所需的平均时间约为A.9msB.9.4msC.12msD.12.4ms21. B解析:磁盘转速是10000转/分钟,平均转一转的时间是6ms,因此平均查询扇区的时 间是3ms,平均寻道时间是6ms,读取4KB扇区信息的时间为0.2ms,信息延迟的时间为0.2ms, 总时间为 3+6+0.2+0.2=9.4ms。22. 下列关于中断I/O方

30、式和DMA方式比较的叙述中,错误的是A.中断I/O方式请求的是CPU处理时间,DMA方式请求的是总线使用权B. 中断响应发生在一条指令执行结束后,DMA响应发生在一个总线事务完成后C. 中断I/O方式下数据传送通过软件完成,DMA方式下数据传送由硬件完成D. 中断I/O方式适用于所有外部设备,DMA方式仅适用于快速外部设备22.D解析:中断处理方式:在I/O设备输入每个数据的过程中,由于无需CP U干预,因而 可使CP U与1/O设备并行工作。仅当输完一个数据时,才需CPU花费极短的时间去做些中断 处理。因此中断申请使用的是CPU处理时间,发生的时间是在一条指令执行结束之后,数 据是在软件的控

31、制下完成传送。而DMA方式与之不同。DMA方式:数据传输的基本单位是数 据块,即在CPU与I/O设备之间,每次传送至少一个数据块;DMA方式每次申请的是总线的 使用权,所传送的数据是从设备直接送入内存的,或者相反;仅在传送一个或多个数据块 的开始和结束时,才需CP U干预,整块数据的传送是在控制器的控制下完成的。答案D的说 法不正确。43. (9分)某32位计算机,CPU主频为800MHz,Cache命中时的CPI为4,Cache块大小为32 字节;主存采用8体交叉存储方式,每个体的存储字长为32位、存储周期为40ns ;存储器 总线宽度为32位,总线时钟频率为200MHz,支持突发传送总线事

32、务。每次读突发传送总线 事务的过程包括:送首地址和命令、存储器准备数据、传送数据。每次突发传送32字节, 传送地址或32位数据均需要一个总线时钟周期。请回答下列问题,要求给出理由或计算过 程。(1)CPU和总线的时钟周期各为多少?总线的带宽(即最大数据传输率)为多少?(2)Cache缺失时,需要用几个读突发传送总线事务来完成一个主存块的读取?(3)存储器总线完成一次读突发传送总线事务所需的时间是多少?(4)若程序BP执行过程中,共执行了 100条指令,平均每条指令需进行1.2次访存,Cache 缺失率为5%,不考虑替换等开销,则BP的CP U执行时间是多少?43. 【参考答案】(1)CPU的时

33、钟周期为:1/800MHz=1.25ns。总线的时钟周期为: 1/200MHz=5ns。总线带宽为:4BX 200MHz=800MB/s或4B/5ns=800MB/s。(2)Cache块大小是32B,因此Cache缺失时需要一个读突发传送总线事务读取一个主存块。(3)一次读突发传送总线事务包括一次地址传送和32B数据传送:用1个总线时钟周期传 输地址;每隔40ns/8=5ns启动一个体工作(各进行1次存取),第一个体读数据花费40ns, 之后数据存取与数据传输重叠;用8个总线时钟周期传输数据。读突发传送总线事务时间: 5ns+40ns+8X 5ns=85ns。(4)BP的CPU执行时间包括Ca

34、che命中时的指令执行时间和Cache缺失时带来的额外开销。 命中时的指令执行时间:100X4X 1.25ns=500ns。指令执行过程中Cache缺失时的额外开 销:1.2X100X5%X85ns=510ns。BP的CPU执行时间:500ns+510ns=1010ns。44. (14分)某计算机采用16位定长指令字格式,其CPU中有一个标志寄存器,其中包含进 位/借位标志CF、零标志ZF和符号标志NF。假定为该机设计了条件转移指令,其格式如下: 其中,00000为操作码OP; C、Z和N分别为CF、ZF和NF的对应检测位,某检测位为 1时表示需检测对应标志,需检测的标志位中只要有一个为1就转

35、移,否则不转移,例如, 若C=1,Z=0,N=1,则需检测CF和NF的值,当CF=1或NF=1时发生转移;OFFSET是相对偏移 量,用补码表示。转移执行时,转移目标地址为(PC) +2+2XOFFSET;顺序执行时,下条 指令地址为(PC) +2。请回答下列问题。(1)该计算机存储器按字节编址还是按字编址?该条件转移指令向后(反向)最多可跳 转多少条指令?(2)某条件转移指令的地址为200CH,指令内容如下图所示,若该指令执行时CF=0, ZF=0, NF=1,则该指令执行后PC的值是多少?若该指令执行时CF=1,ZF=0, NF=0, 则该指令执行后PC的值又是多少?请给出计算过程。151

36、110987000000 |0| 1 |1 |(3)实现“无符号数比较小于等于时转移”功能的指令中,C、Z和N应各是什么?(4)以下是该指令对应的数据通路示意图,要求给出图中部件的名称或功能说明。44. 【参考答案】(1)因为指令长度为16位,且下条指令地址为(PC) +2,故编址单位是字节。偏移OFFSET为8位补码,范围为-128127,故相对于当前条件转移指令,向后最多可跳转 127条指令。(2)指令中C=0,Z=1,N=1,故应根据ZF和NF的值来判断是否转移。当CF=0,ZF=0,NF= 1时,需转移。已知指令中偏移量为11100011B=E3H,符号扩展后为FFE3H,左移 一位(乘2)后为FFC6H,故PC的值(即转移目标地址)为200CH+2+FFC6H=1FD4H(2分) 当CF=1,ZF=0,NF=0时不转移。PC的值为:200CH+2=200EH。(3)指令中的C、Z和N应分别设置为C=Z=1,N=0。(4)部件:指令寄存器(用于存放当前指令);部件:移位寄存器(用于左移一位); 部件:加法器(地址相加)。参考资料:20112013年计算机专业考研真题

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。