FPGA静态时序分析模型——寄存器到寄存器

FPGA静态时序分析模型——寄存器到寄存器

《FPGA静态时序分析模型——寄存器到寄存器》由会员分享,可在线阅读,更多相关《FPGA静态时序分析模型——寄存器到寄存器(11页珍藏版)》请在装配图网上搜索。

1、FPGA静态时序分析模型寄存器到寄存器1.适用范围本文档理论适用于Actel FPGA并且采用Libero软件进行静态时序分析(寄存器到寄存器)。2. 应用背景静态时序分析简称STA,它是一种穷尽的分析方法,它按照同步电路设计的要求,根据电路网表 的拓扑结构,计算并检查电路中每一个DFF(触发器)的建立和保持时间以及其他基于路径的时延要 求是否满足。STA作为FPGA设计的主要验证手段之一,不需要设计者编写测试向量,由软件自动 完成分析,验证时间大大缩短,测试覆盖率可达10 0%。静态时序分析的前提就是设计者先提出要求,然后时序分析工具才会根据特定的时序模型进行分 析,给出正确是时序报告。进行

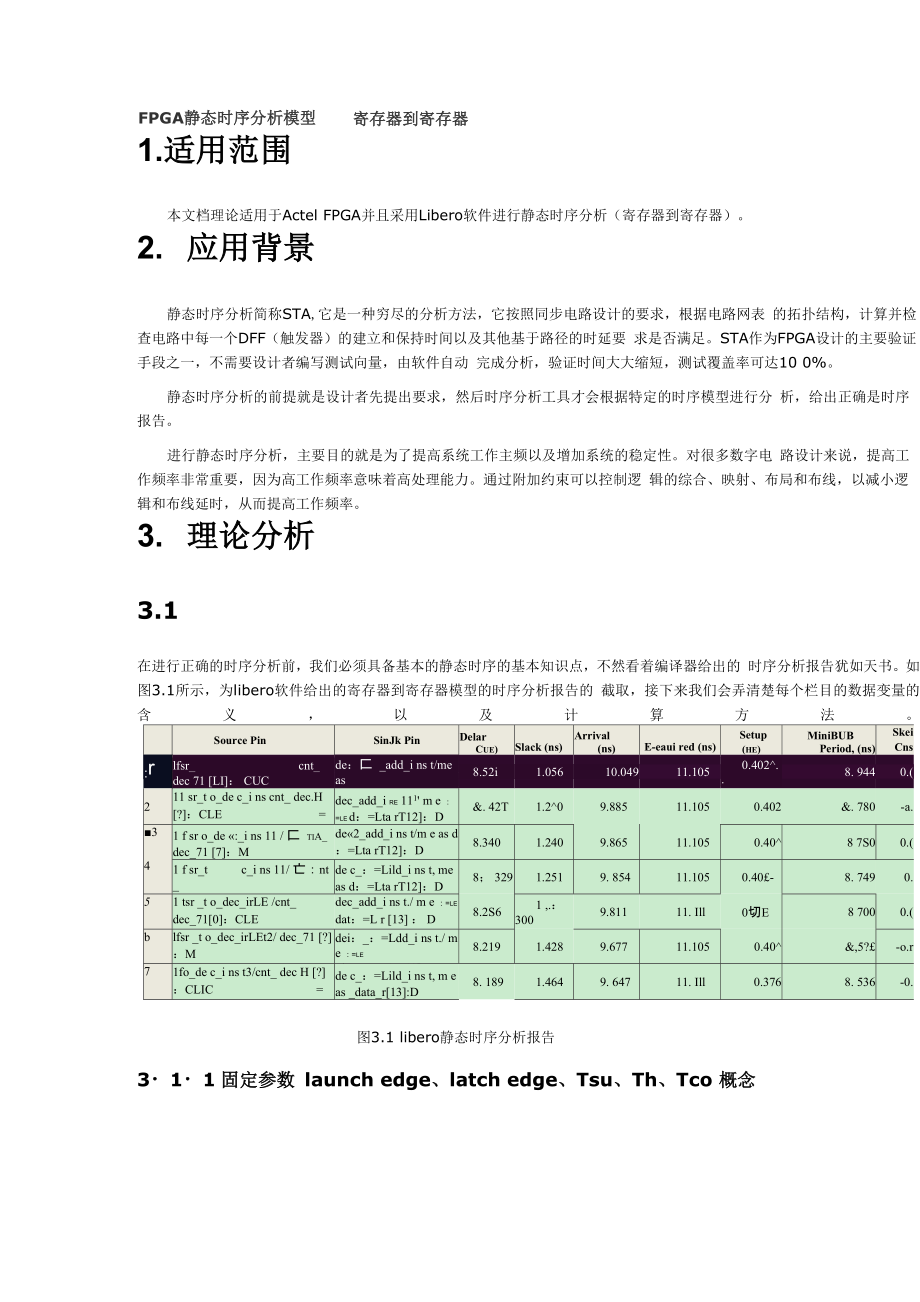

2、静态时序分析,主要目的就是为了提高系统工作主频以及增加系统的稳定性。对很多数字电 路设计来说,提高工作频率非常重要,因为高工作频率意味着高处理能力。通过附加约束可以控制逻 辑的综合、映射、布局和布线,以减小逻辑和布线延时,从而提高工作频率。3. 理论分析3.1在进行正确的时序分析前,我们必须具备基本的静态时序的基本知识点,不然看着编译器给出的 时序分析报告犹如天书。如图3.1所示,为libero软件给出的寄存器到寄存器模型的时序分析报告的 截取,接下来我们会弄清楚每个栏目的数据变量的含义,以及计算方法。Source PinSinJk PinDelarCue)Slack (ns)Arrival(

3、ns)E-eaui red (ns)Setup(he)MiniBUBPeriod, (ns)Skei Cns:rlfsr_cnt_dec 71 LI: CUCde:匚 _add_i ns t/me asdata r12:D8.52i1.05610.04911.1050.402.8. 9440.(211 sr_t o_de c_i ns cnt_ dec.H ?:CLE=dec_add_i re 111 m e :=le d:=Lta rT12:D&. 42T1.209.88511.1050.402&. 780-a.341 f sr o_de :_i ns 11 / 匚 tiA_ dec_71

4、7:Mde2_add_i ns t/m e as d:=Lta rT12:D8.3401.2409.86511.1050.408 7S00.(1 f sr_tc_i ns 11/ 亡:nt _dec H Ll: CUCde c_:=Lild_i ns t, me as d:=Lta rT12:D8; 3291.2519. 85411.1050.40-8. 7490.51 tsr _t o_dec_irLE /cnt_ dec_710:CLEdec_add_i ns t./ m e :=le dat:=L r 13 : D8.2S61 ,.:3009.81111. Ill0切E8 7000.(b

5、lfsr _t o_dec_irLEt2/ dec_71 ?:Mdei:_:=Ldd_i ns t./ m e :=le,d:=Lt:rT12:D8.2191.4289.67711.1050.40&,5?-o.r71fo_de c_i ns t3/cnt_ dec H ?:CLIC=de c_:=Lild_i ns t, m e as _data_r13:D8. 1891.4649. 64711. Ill0.3768. 536-0.图3.1 libero静态时序分析报告311固定参数 launch edge、latch edge、Tsu、Th、Tco 概念1launch edge时序分析起点(

6、launch edge):第一级寄存器数据变化的时钟边沿,也是静态时序分析的起点。2latch edge时序分析终点(latch edge):数据锁存的时钟边沿,也是静态时序分析的终点。3Clock Setup Time (Tsu)建立时间(Tsu):是指在时钟沿到来之前数据从不稳定到稳定所需的时间,如果建立的时间不满足要求那么数据将不能在这个时钟上升沿被稳定的打入触发器。如图3.2所示:rsuelkDataA图3.2建立时间图解4.Clock Hold Time (Th)保持时间(Th):是指数据稳定后保持的时间,如果保持时间不满足要求那么数据同样也不能被稳定的打入触发器。保持时间示意图如图

7、3.3所示:ThelkData图3.3保持时间图解5.Clock-to-Output Delay (tco)数据输出延时(Tco):这个时间指的是当时钟有效沿变化后,数据从输入端到输出端的最小时间间隔。312 Clock skew时钟偏斜(clock skew):是指一个时钟源到达两个不同寄存器时钟端的时间偏移,如图3.4所示:时钟偏斜计算公式如下:Tskew = Tclk2 - Tclkl(公式3-1)313 Data Arrival Time数据到达时间(Data Arrival Time):输入数据在有效时钟沿后到达所需要的时间。主要分为 三部分:时钟到达寄存器时间(Tclk1),寄存器

8、输出延时(Teo)和数据传输延时(Tdata),如图3.5 所示ciir图3.5数据到达时间数据到达时间计算公式如下:Data Arr ival Time = Launch edge + Tclkl +Tco + Tdata(公式3-2)314 Clock Arrival TimeLatch edgecIQ时钟到达时间(Clock Arrival Time):时钟从latch边沿到达锁存寄存器时钟输入端所消耗的时间为时钟到达时间,如图3.6所示Tclk2图3.6时钟到达时间时钟到达时间计算公式如下:Clock Arr ival Time = Lacth edge + Tclk2(公式3-3)3

9、15 Data Required Time (setup/hold)Latch edgecBT数据需求时间(Data Required Time):在时钟锁存的建立时间和保持时间之间数据必须稳定, 从源时钟起点达到这种稳定状态需要的时间即为数据需求时间。如图3.7所示:Tclk2图3.7数据需求时间(建立)数据需求时间计算公式如下:Data Requi red Time = Clock Arr ival Time - Tsu(公式3-4)(保持)数据需求时间计算公式如下:Data Requi red Time = Clock Arr ival Time +Th(公式3-5)316 Setup

10、slack建立时间余量(setup slack):当数据需求时间大于数据到达时间时,就说时间有余量,Slack 是表示设计是否满足时序的一个称谓。REG1REG2Tclk2如图3.8所示,建立时间余量的计算公式如下:Setup slack = Data Requi red Time - Data Arr ivalTime(公式 3-6)由公式可知,正的slack表示数据需求时间大于数据到达时间,满足时序(时序的余量),负的 slack表示数据需求时间小于数据到达时间,不满足时序(时序的欠缺量)。317时钟最小周期时钟最小周期:系统时钟能运行的最高频率。1. 当数据需求时间大于数据到达时间时,时

11、钟具有余量;2. 当数据需求时间小于数据到达时间时,不满足时序要求,寄存器经历亚稳态或者不能正确 获得数据;3. 当数据需求时间等于数据到达时间时,这是最小时钟运行频率,刚好满足时序。从以上三点可以得出最小时钟周期为数据到达时间等于数据需求时间,的运算公式如下:Data Requi red Time = Data Arr ival Time(公式3-7)由上式推出如下公式:Tmin + Latch edge + Tclk2 - Tsu = Lau nch edge + Tclk1 + Tco + Tdata最终推出最小时钟周期为:Tmin = Tco + Tdata + Tsu - Tskew

12、(公式3-8)4.应用分析4.1设置时钟主频约束所有的静态时序分析都是在有约束的情况下编译器才给出分析报告,所以进行时序分析的第一步 就是设置约束。Libero软件设置时钟约束的途径三种,单时钟约束,多时钟约束和在Designer里面进行约束。411单时钟约束有时我们系统所有模块都采用同一个时钟,这种方式最为简单,直接在Synplify主界面上有个 设置时钟约束的,如图4.1中红框所示:图4.1单时钟设置设置完成后,编译,通过Synplify时钟报告看初步时钟运行频率能否达到要求,时钟报告如图4.2所示,设定10OMh z,能运行102.7Mhz,满足时序。图4.2时序报告4.2多时钟约束当系

13、统内部模块采用了多个时钟时,那就需要进行多时钟约束了。首先需要打开设置界面,在Synplify中选择:File-New-Constraint File建立SDC文件,选择时钟约束如图4.3所示:图4.3多时钟约束4.3Designer SmartTime 时钟约束对时钟进行如下约束后保存SDC文件,约束如图4.4所示-1EnabledClock Obj ectClock Ali asFrequerLcy(MHz)Feri od(n或n: Ey5_FLL_irLEt. GIAn: Ey5_FLL_irLst. GLA300H 333333333n: EyE_FLL_irLEt. GLBn: Ey

14、E_FLL_inEt. GLB3001.3333&3an: EyE_FLL_irLEt. GLCn: EyE_FLL_irLEt. GLC300蕉 3333333334clk2clk210010图4.4多时钟约束完成时钟约束除了在Synplify中可以约束外,还可以在Designer SmartTime中设置时钟约束,打开Designer Constraint,选择Clock进行针对每个使用时钟的设置,如图4.5所示:4.4图4.5 Designer时序约束时序报告分析441 Synplify时序报告当约束了时序后,需要观察时序报告,看时钟能否达到我们需要的时钟,首先观察Synplify综 合

15、报告。以多时钟约束为例子,从Synplify得到的时序报告如图4.6所示:St-art-ing ClockP.eiT-iestedFreii-iencyE st- iiiiat ed Freii-iencyP.est e dPeriodEstiiiiatedPeriodSlackclkZ100.0 HHz102 J MHz10.0009-740 . Z60sys PLL ins直300-0 MHz3E3-3 MHz3_ 3333.093CL 240sye P L L inst. GLE:300.0 HHz3Z3.3 MHz3.3333.0930.240sys_P L L_inst. GLC30

16、0.0 MHz323-3 MHz3.3333.0930.Z40图4.6多时钟约束时序报告由上图可知时序都满足约束,未出现违规,可以在下面的报告中查看最差路径,如图4.7所示是clk2 的最差路径。Worst Path InfornLationView Worst Path in Analyst-P ath inf or illation for p at h ni-Uiiki e r 1: P.est-ed Period:-Setup tiiiie:+ C1 ck delay at ending point-:= P.eii-iired t-iiae:一 Propagation time:一

17、C1ock delay at starting point: = Slack (non-critical):Ni-UllLi e r o f logic level (s):Starting pint:Ending p o int-:Thest artp o int.isclockedbyTheendp o intisclockedby10-0000.3760.000 (ideal)9.6Z49.3630.000 (ideal)0.26081fsr_to_dec_inst3-cnt_dec_r10 / Q de c_add_inst. ills as_dat a_r 1Z / D clkZ r

18、ising on pin CLKclkZ rising on pin CLK图4.7最差路径442Designer SmartTime时序分析报告当设计经过Synplify综合给出网表文件后,还需要Designer进行布局布线,通过布局布线优 化后的时序会有变化,因此,还需要分析布局布线后的时序,打开Designer-Timing Analyzer 查阅整体时序分析报告如图4.8所示:Clock Details:EasePeriod (ns)FreQuencr (KHi)Keq.ul red Period (ns)Keaui red Freauencr (MHi)Ext ernal Setup

19、 (ns)Ext ernal Hold (ns)Max Clock to Out (ns)Min to(nQ elk4. 000250.00020. 00050. 0001T/A1T/AN/AN/Aclk29. 610一 05010. 000100. 000U. 5910. 1347. 000:2. $52srs PLL inEt/Core: CT.A3- 05?32T.1183. 333300. 0301. 538-o. 361H/A1T/AErE_PLL_inst/Core:CT.Ti3- 057327.1183. 333300. 0301. 598-0. 3611T/AiT/Asy s_

20、PLL_i list/Core: CT r乱05T327.1183. 333300. 0301. 538-0. 3611T/A1T/A图4.8布局布线后时序报告由Synplify综合后的报告和Designer进行布局布线后的报告可以看出,布局布线后优化了一 些时序,特别是clk2时钟,通过布局布线后优化到了 184Mhz,完全满足时序。4.4.3详细时序报告图通过Synplify综合后的和Designer进行布局布线都只是看到了一个大体的时序报告,当我们 需要分析时序时候必须观察仔细的时序报告,在SmartTime中提供这种报告功能,以clk2分析为 例,在Timing Analyzer找到如下区域。图4.9时序报告选择如图4.9所示,选择寄存器到寄存器进行分析时钟主频。图4.10寄存器到寄存器分析如图4.10所示,时序报告中给出了数据延时,时序余量,数据到达时间,数据需求时间,数据 建立时间,以及最小周期和时钟偏斜等信息,有了上一节的时序分析基础知识,我们完全能看懂这些数据代表的意义,这样对我们时序分析就知己知彼,进一步双击其中一条路径,还会给出这条路径的 硬件电路图,如图4.11所示,有了这些详细的时序报告,对设计进行调整更加清晰。图4.11硬件路径

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。