频综的现状与未来展望

频综的现状与未来展望

《频综的现状与未来展望》由会员分享,可在线阅读,更多相关《频综的现状与未来展望(17页珍藏版)》请在装配图网上搜索。

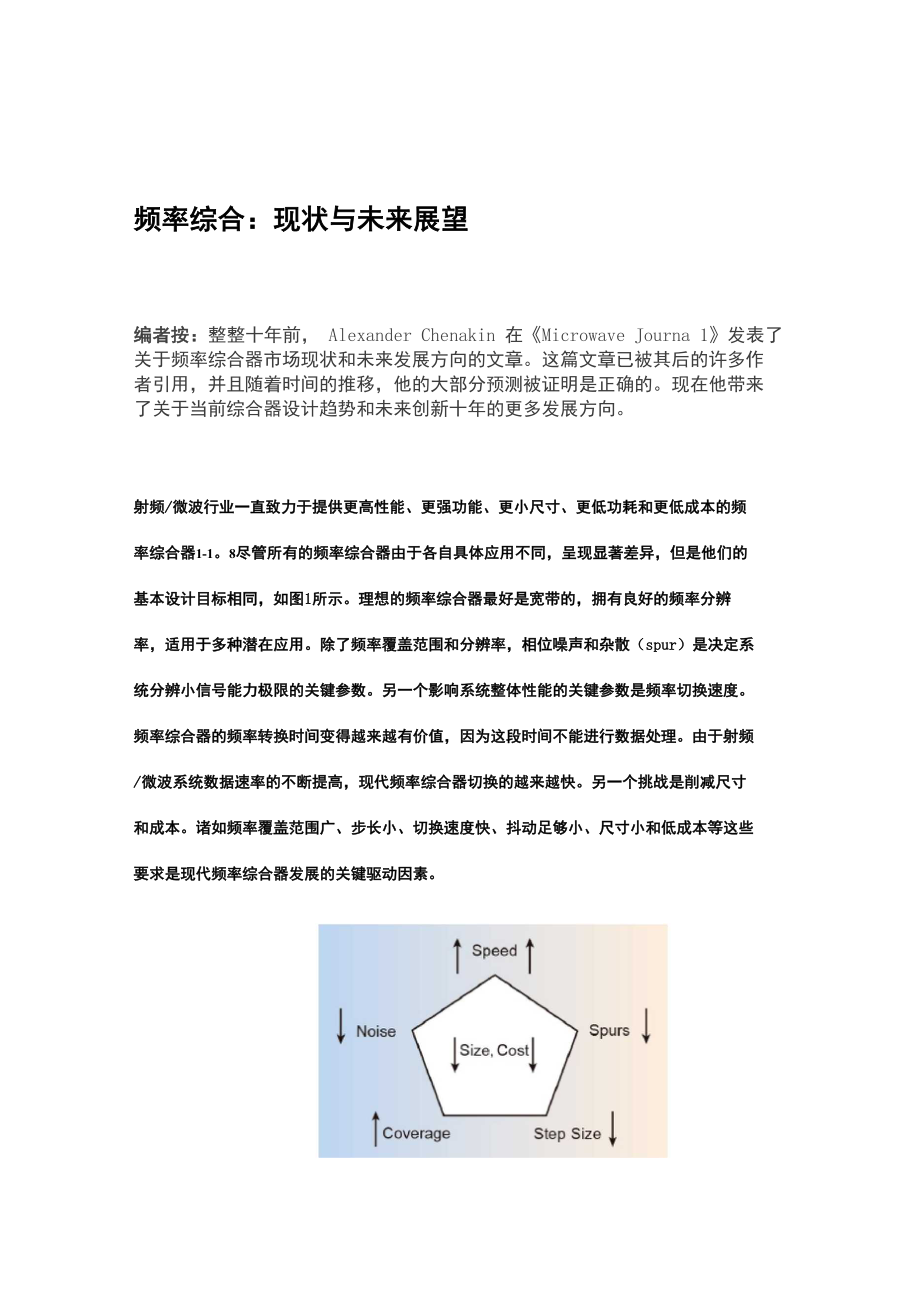

1、频率综合:现状与未来展望编者按:整整十年前, Alexander Chenakin 在Microwave Journa 1发表了 关于频率综合器市场现状和未来发展方向的文章。这篇文章已被其后的许多作 者引用,并且随着时间的推移,他的大部分预测被证明是正确的。现在他带来 了关于当前综合器设计趋势和未来创新十年的更多发展方向。射频/微波行业一直致力于提供更高性能、更强功能、更小尺寸、更低功耗和更低成本的频 率综合器1-1。8尽管所有的频率综合器由于各自具体应用不同,呈现显著差异,但是他们的 基本设计目标相同,如图1所示。理想的频率综合器最好是宽带的,拥有良好的频率分辨 率,适用于多种潜在应用。除了

2、频率覆盖范围和分辨率,相位噪声和杂散(spur)是决定系 统分辨小信号能力极限的关键参数。另一个影响系统整体性能的关键参数是频率切换速度。 频率综合器的频率转换时间变得越来越有价值,因为这段时间不能进行数据处理。由于射频 /微波系统数据速率的不断提高,现代频率综合器切换的越来越快。另一个挑战是削减尺寸 和成本。诸如频率覆盖范围广、步长小、切换速度快、抖动足够小、尺寸小和低成本等这些 要求是现代频率综合器发展的关键驱动因素。图1:综合器的设计挑战。架构频率综合器的特性在很大程度上取决于其特殊架构,可以被分成几个主要的类型,如图 2 所示。直接频率综合架构是直接从获得的参考信号中创建输出信号,通过

3、在频域控制和组 合参考信号(直接模拟综合),或通过在时域构造输出波形(直接数字综合)间接频率综合 方法假定输出信号以一种输出频率和输入参考信号相关的形式(例如,锁相)在频率综合器 内部生成。同样,间接频率综合可以用模拟和数字技术来完成。然而实际的综合器为了得到 多种技术的各自优势,通常是结合多种技术的混合设计。图2:频率综合器种类。间接频率综合几十年来,间接锁相环(PLL )综合器是(并且仍然是)最常见和最流行的技术。一个 通用的单回路锁相环(图3)包括一个可调电控振荡器(VCO),可产生一个所需频率范围 内的信号。这个信号通过具有可变分频比 N 的分频器被反馈到鉴相器。鉴相器的另一个输 入是

4、被划分成所需频率步长的参考信号。鉴相器对比两个输入信号从而产生误差电压,使其 经过滤波(和可选放大)后调节VCO产生锁定的频率:fOUT=NfPD,其中fPD是鉴相器输入端的 比较频率。因此通过改变分频系数N,以等于fPD的离散频率步长实现频率调谐。图3:单回路锁相环综合器。一个简单的 PLL 频率综合器表现出各种限制和权衡。对频率综合器性能的主要影响是 由为了实现较高的频率所需的大分频比和较高的分辨率引起的。注意由 PLL 器件产生的任 何噪声以 20logN 的速度恶化,其中 N 为分频比。工作在小步长的传统的整数分频锁相环, 分频比较大是因为步长必须等于鉴相器的比较频率。结果相位噪声大幅

5、恶化。此外频率综合 器的切换速度由其环路带宽决定,因此受限于鉴相器比较频率。由于环路滤波器带外抑制不 足,或者甚至环路不稳定,增加环路带宽可能会导致更高频的参考杂散。因此,这个简单的 单环架构锁相环受限于相互排斥的设计目标。它通常用于要求不高的应用领域或侧重于低 成本应用。小数分频频率综合器小数 N 分频综合器打破了频率分辨率和其它特性之间的联系,通过采用小数分频比使 得对于一个给定的步长允许更高的比较频率。通过改变两个(或更多)分频比(比方说,n 和n+1)并且在一定时间内平均其输出频率实现小数分频。另一种了解这个过程的方法是计 算在给定时间间隔内由此复杂的分频器产生的脉冲数。显然,平均分频

6、系数介于n和n +1之 间,且取决于每个分频器处理多少个脉冲。此方案最大的问题是小数 N 分频器输出的瞬时 频率不恒定。分频系数的突然变化导致了相位的不连续性,使得鉴相器输出电压产生了尖峰。由于频率划分变化以同样的频率周期性地产生,它在综合器的输出频谱中表现为离散的杂散。抑制这种谐波需要必须足够小的PLL 滤波器带宽,而这可能会影响相位噪声和速度性能。有很多技术可以降低小数分频的杂散19-。21通常可以在分频系数变化的时候通过增加或 减少鉴相器输出的电压来实现。另一种方法是使用一个允许更大的分频系数的多模分频器 在这种情况下,我们会得到大量的小幅度杂散。多模分频器往往和 Delta-Sigma

7、 调制器一 起使用,产生随机频率杂散并将它们推向更高的偏移频率,使其可以通过回路滤波器过滤 掉。尽管存在各种改进的技术,小数分频技术的主要缺点是由小数划分机制导致的相位误差 过量产生的大量杂散电平。一种降低小数分频杂散的聪明的做法是利用一个可变参考频率。该技术基于一个小数N 分频综合器的杂散的位置是其特定分频比和输出频率的函数的原理。因此,对于一个给定的 输出频率,可以通过改变参考频率和相应的分频比的方式来移动(然后过滤掉)一个不想要 的杂散。这涉及到频率规划,因此需要一个额外的频率综合器(用作参考频率)。此外尽管 减小了分频比,其依然可能大到影响PLL性能。PLL频率综合器内部直接数字频率综

8、合(DDS)DDS 是另一个产生良好的频率分辨率的有效解决方案,且没有通常的鉴相器频率下降问 题。DDS具有良好的频率分辨率,用于高频参考频率或作为小数分频器,如图4所示。虽然 DDS提供了良好的频率分辨率,但其杂散水平通常很高。此外由于PLL的乘法机制,进一步 恶化了杂散。虽然图4中两种方案看起来不同,但是它们对DDS杂散的影响方式相同。在 这两种情况下,总的环路分频系数由 VCO 输出和鉴相器比较频率之间的比率决定。可以利 用许多技术减少DDS杂散,例如使用可调时钟(如上述的小数N综合器)或如图5所示将 其上变频后再将DDS信号进行分频。注意上变频相关的DDS带宽减少,往往需要根据所需的特

9、定的频率规划进一步扩展。这可以通过多种方法实现,例如,利用可调(相对固定)分频系数。four0DOSfOUT0DDS-*图4:在PLL综合器内部采用DDS作为高分辨率高频参考源a)或小数分频器b)。图 5:DDS 信号的上变频和分频。PLL 综合器中的频率偏移和倍频在频率综合器反馈路径上使用频率转换(混频)技术可以大大提高频率综合器的主要特 性,如图 6所示。其主要思路是将 VCO 的输出在混频器和偏移频率源的帮助下转换成一个 低得多的频率。在某些情况下(例如,当工作频率范围较窄时)可以完全消除分频器的反馈。 在这种情况下,环路分频系数等于1,相位噪声没有发生恶化。此外,通过在反馈路径中用 乘

10、法器代替分频器可以进一步减少PLL器件的残余噪声的影响,如图7所示。图6:频率偏移方法改善锁相环性能。图7:在PLL反馈路径中插入乘法器。多环综合器方案简单的频率偏移方案的主要缺点是频率覆盖范围有限。对于一个固定的偏移频率,扩大输出频率带宽会导致混频器输出的中频频率升高。这就需要一个分频系数更大的分频器,从而使这种方法失效。为了保证分频比最小,偏移信号频率应尽量靠近射频输出频率。这可以 通过使用宽带偏移信号的多环路方案来实现(图8)。图8:多回路综合器。在反馈回路中使用混频器一个聪明的解决方案是如图 9 所示在锁相环反馈路径内利用一连串混频器。从一个共 同的高频可调参考频率使用分频器和/或乘法

11、器可以获得各自的频率偏移信号。在这种情况 下混频器互调产物和鉴相器频率谐波可以很容易地被环路滤滤除22。图9:在锁相环反馈路径中使用一连串混频器。直接综合直接模拟综合器直接模拟综合有着完全不同的玩法。顾名思义,所需信号通过混频和滤波直接产生(即不用再生),如图 10所示。基频通常是由一个共同的参考频率倍频、分频和/或混合得到。直接模拟综合技术的关键优势是切换速度非常快,范围在微秒到纳秒级。由于直接模拟综合没有反馈回路,开关速度仅受限于开关及其控制电路和滤波器设定的传播时延。图10:直接模拟综合器。另一个明显的优势是由于使用具有几乎可忽略的低残留噪声的元件,从而产生很低的 相位噪声。相位噪声主要

12、取决于所用的固定频率源的噪声,可以做到非常低。主要缺点是频 率覆盖范围和步长有限。输出频率的数量可以通过增加基础频率的数量和/或混频器的阶数 来实现,然而,这迅速增加了设计复杂性和元件的总数量。另一个严重的问题是必须过滤大量的混频后产物。包括需要去掉的边带、本振泄漏和互 调产物。取决于特定的频率规划,过滤中心附近的杂散是一项艰巨的任务。此非凡的设计需 要付出一定的努力和仔细的频率规划。虽然各种各样的混频和滤波方案是可行的,但如果需 要较小的频率步长和较宽的频率范围时,结果往往是需要大量的硬件。因此,虽然直接模拟 综合提供了极好的调谐速度和相位噪声,它只有限适合于可以忍受相当高成本的应用。直接数

13、字频率综合器与传统概念相反,直接数字频率综合器利用数字信号处理技术根据参考时钟频率一点 一点地在时域上构造一个输出信号波形。最初,使用相位累加器和查表来创建所需信号的数 字代码(见图11)。然后使用一个数字到模拟转换器(DAC)来重新构造一个正弦波或其它 所需波形。最后使用低通滤波器滤除杂散,完成波形创建。这个过程非常快速,主要受数字 控制逻辑的速度限制。因此频率切换速度非常高,和直接模拟方案速度差不多。DDS还具有 相当低的相位噪声,甚至能改善(受其残留本底噪声限制)其时钟源本身的相位噪声。然而 最有价值的 DDS 的特性是其由相位累加器的长度确定的极精细的频率分辨率,很容易实现 亚赫兹的水

14、平。图11:直接数字频率综合器。主要的缺点是可用带宽受限。虽然DDS工作频点接近直流,但根据奈奎斯特原理,其最 高频率只能到时钟频率的一半。虽然可以工作在高于奈奎斯特区,但是性能下降非常快。另 一个严重的问题是由于 DDS 技术中固有的许多因素导致的较高杂散,例如数位截取、量化 和 DAC 转换误差。DSS的形式可以是完全集成的专用芯片或可以使用单独的现场可编程门阵列(FPGA)和 DAC芯片来实现。后者可将数字部分限制在FPGA内部,因此隔离了 EMI引起的杂散。如今 FPGA 有足够的能力来建立相当复杂的多核相位累加器和索引表,由数位截取导致的杂散电 平可忽略不计。结果主要的杂散源通常是由

15、于 DAC 的非线性和量化噪声引起的。虽然目前 并不常见,不适用DAC的解决方案也是可以的(例如,使用数字时间转换)23直到最近,DS技术很少单独在微波频率使用。然而高频集成电路的快速发展可以使DDS 工作在微波频率,具有微赫兹的分辨率、纳秒级的切换速度和内置调制oDDS的可用带宽的 扩展(并且减小其杂散)是业界所需的关键改进。发展和未来预测传统上综合器是为了在其工作频率范围内产生一个连续信号。其振幅在一定范围内随 频率变化。然而,较新的设计带来更多的如振幅均衡和控制功能。输出电平可以采用开环控 制(查表)或更复杂的闭环自动电平控制(ALC)方案来校准和控制。此外,现在工业界需 要更复杂的包括

16、传统的模拟调制(幅度、频率、相位和脉冲)到复杂的矢量形式,如IQ调 制的波形。这些调制功能连同振幅控制和谐波抑制现在不仅可以制作成笨重的测试和测量 信号发生器,也可以制作成较小的模块形式。主要性能特点(如相位噪声、杂散和切换速度) 正在逐步接近那些专用测试和测量信号发生器。提到相位噪声性能,综合器设计师主要依靠100MHz恒温晶体振荡器(OCXO)技术。如 今商用OCXO的输出在10KHz和100MHz偏移量达到T70至-176dBc/Hz (甚至更好)。如果 频率综合器电路是“理想”的话,在10GHz可实现-130或-136dBc/Hz的相位噪声。虽然没 有理想电路,所有当前的发展方向是力求

17、理想。10MHz的OCXO的表现在较低的频率偏移(100Hz以下)时更好。此外,它的短期稳定性也优于100MHz振荡器。因此,综合器的设 计通常将其输出到锁定10MHz参考频率。同样高频振荡器(如SAW和DRO)在100KHz及其 以上频率偏移量上有更好的表现24-29。一个组合参考源包含几个彼此锁定的振荡器,可在任 何频率偏移上实现最低的相位噪声。通过使用蓝宝石谐振腔或者光学方法的高Q值振荡器 可以进一步提高性能 30-33o结论总的来说,间接的基于VCO的PLL频率综合器是目前最流行的方案。将来预计通过减 少PLL残留本底噪声来提高性能,以支持兆赫范围的环路滤波。迅速的切换速度(几微秒)

18、和低相位噪声(10GHz输出,在10kHz偏移频率约为-130dBc/Hz)是当今设计者近期共同的 目标。小尺寸、可扩展的功能(如内置的调制和幅度控制)和低成本是工业界的设计目标。然而未来最激动人心的发展,可能是结合具有巨大的发展潜力的DDS技术。通过拓展 DDS可用带宽和减小其杂散会带来许多进步。倍频和/或上变频技术可能为毫米波或更高频 率(虽然DDS本身带宽会不断增加)带来可用的带宽。在一些点上,直接综合技术通过提供 快得惊人的切换速度、纳秒级的调谐速度以及复杂的输出波形,有望争夺并最终取代间接综 合设计。远期的重大突破预计是利用其它物理原理或材料设计和制作参考源。例如,有人发布了 10G

19、Hz输出频率、相位噪声在10kHz偏移量为-170dBc/Hz的基于蓝宝石谐振器的振荡器34 这些期望会极大地改变制造新的综合器的概念方法,甚至改变思考问题的整体方式。最终能 实现什么样的性能?只有未来知道。未来几十年将有许多惊人的发展。 (译者:于斌)参考文献1. A. Chenakin, “Frequency Synthesis: Current Solutions and NewTrends, Microwave Journal , Vol. 50, No. 5, May 2007, pp. 256 - 266.2. A. Chenakin, “Frequency Synthesizer

20、s: Concept to Product,” Artech House,Norwood, MA,2010.3. J. Crawford, “Frequency Synthesizer Design Handbook,” Artech House, Norwood, MA, 1994.4. J. Crawford, “Advanced Phase-Lock Techniques,” Artech House, Norwood, MA, 2008.5. W. Egan, “Phase-Lock Basics,” Wiley, 2nd Edition, Hoboken, NJ, 2007.6. W

21、. Egan, “Frequency Synthesis by Phase Lock,” Wiley, 2nd Edition, New York, NY, 1999.7. Z. Galani and R. Campbell, “An Overview of Frequency Synthesizers for Radars,” IEEE Transactions on Microwave Theory and Techniqu,esVol. 39, No. 5, May 1991, pp. 782 - 790.8. F. Gardner, “Phaselock Techniques,” Wi

22、ley, 3rd Edition, Hoboken, NJ, 2005.9. S. Goldman, “Phase-Locked Loop Engineering Handbook for Integrated Circuits,” Artech House, Norwood, MA, 2007.10. J. Klapper and J. Frankle, “Phased-Locked and Frequency-Feedback Systems,” Academic Press, New York, NY, 1972.11. V. Kroupa, “Frequency Synthesis:

23、Theory, Design and Applications,” Wiley, New York, NY, 1973.12. V. Kroupa (ed.), “Direct Digital Frequency Synthesizers,” New York, NY, IEEE Press, 1999.13. V. Kroupa, “Phase Lock Loops and Frequency Synthesis,” Wiley, Hoboken,NJ, 2003.14. V. Manassewitsch, “Frequency Synthesizers: Theory and Design

24、,” 3rd Edition, Wiley, Hoboken, NJ, 2005.15. V. Reinhardt, “A Short Survey of Frequency Synthesizer Techniques,” Proceedings of the 40th Annual Symposium on Frequency Control, May 1986, pp. 355 - 365.16. U. Rohde, “Digital PLL Frequency Synthesizers: Theory and Design,” Prentice-Hall, Englewood Clif

25、fs, NJ, 1983.17. U. Rohde, “Microwave and Wireless Synthesizers: Theory and Design,” Wiley, New York, NY, 1997.18. R. Stone, “Frequency Synthesizers,” Proceedings of the 21st Annual Symposium on Frequency Control” April 1967, pp. 294 - 307.19. T. Riley, M. Copeland and T. Kwasniewski, “Delta-Sigma M

26、odulation inFractional-N Frequency Synthesis,” IEEE Journal of Solid-State Circui,ts Vol. 28, No. 5, May 1993, pp. 553-559.20. H. Wang, P. Brennan and D. Jiang, “A Generic Multi-Modulus Divider Architecture for Fractional-N Frequency Synthesizers,” IEEE Frequency Control Symposium, May 2007, pp. 261

27、-265.21. H. Wang and P. Brennan, “A New Spurious Component Suppressing Techniquein Fractional-N Frequency Synthesizers,” IEEE Frequency Control Symposium, May 2008, pp. 753-757.22. A. Chenakin, “Low Phase Noise PLL Synthesizer,” US Patent No. 770129,9 April 2010.23. F. Baronti, D. Lunardini, R. Ronc

28、ella and R. Saletti, “PicosecondAccuracy Digital-to-Time Converter for Phase-Interpolation DDS,” 35th Annual Precise Time and Time Interval Meet,inDgecember 2003, pp. 347 - 358.24. M. Driscoll, “Low-Noise Microwave Signal Generation Using Bulk- and Surface-Acoustic-Wave Resonators,” IEEE Transaction

29、s on Ultrasonics, Ferroelectries and Frequency ControlVol. 35, No. 3, May 1988, pp. 426 - 434.25. G. K. Montress, T. E. Parker, M. J. Loboda and J. A. Greer, “ExtremelyLow-Phase-NoiseSAW Resonators and Oscillators: Design andPerformance,” IEEE Transactions on Ultrasonics, Ferroelectrics and Frequenc

30、y Control, Vol. 35, No. 6, November 1988, pp. 657 - 667.26. T. Parker, “Current Developments in SAW Oscillator Stability,” IEEE International Frequency Control SymposiumProceedings, June 1977, pp. 359 - 364.27. J. Everard, “A Review of Low Noise Oscillator. Theory and Design,”IEEE International Freq

31、uency Control Symposium ProceedingMay 1997, pp. 909- 918.28. Z. Galani, M. J. Bianchini, R. C. Waterman, R. Dibiase, R.W. Laton and J.B. Cole, “Analysis and Design of a Single-Resonator GaAs FET Oscillator With Noise Degeneration,” IEEE Transactionson Microwave Theory and Techniques, Vol. 32, No. 12

32、, December 1984, pp. 1556-1565.29. D. Tsarapkin, “Phase Noise in Microwave Bridge Oscillators,” IEEEInternational Frequency Control SymposiumProceedings, August 2005, pp.534- 538.30. D. Tsarapkin, “Low Phase Noise Sapphire Disk Dielectric ResonatorOscillator with Combined Stabilization,” IEEE Intern

33、ational FrequencyControl Symposium Proceedings June 1994, pp. 451 - 458.31. D. Santiago and G. Dick, “Microwave Frequency Discriminator with a CooledSapphire Resonator for Ultra-Low Phase Noise,” IEEE InternationalFrequency Cont rol Symposium ProceedingsMay 1992, pp. 176 - 182.32. E. Ivanov, M. Toba

34、r and R. Woode, “Microwave Interferometry: Application to Precision Measurements and Noise Reduction Techniques,” IEEETransactions onUltrasonics, Ferroelectrics and Frequency Control, Vol.45, No. 6, November 1998, pp. 1526-1536.33. S. Yao and L. Maleki, “Characteristics and Performance of a Novel Ph

35、otonicOscillator,” IEEE International Frequency Control Symposium Proceedi,ngsMay-June 1995, pp. 161-168.C. McNeilage, J. H. Searls, E. N. Ivanov, P. R. St ockwell, D. M. Green and M. Mossamaparast, “A Review of Sapphire Whispering Gallery-Mode Oscillators Including Technical Progress and Future Potential of the Technology, IEEE International Frequency Control Symposium ProceedingAugust 2004, pp. 210 - 218.欢迎您的下载,资料仅供参考!

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。