建立时间与保持时间

建立时间与保持时间

《建立时间与保持时间》由会员分享,可在线阅读,更多相关《建立时间与保持时间(6页珍藏版)》请在装配图网上搜索。

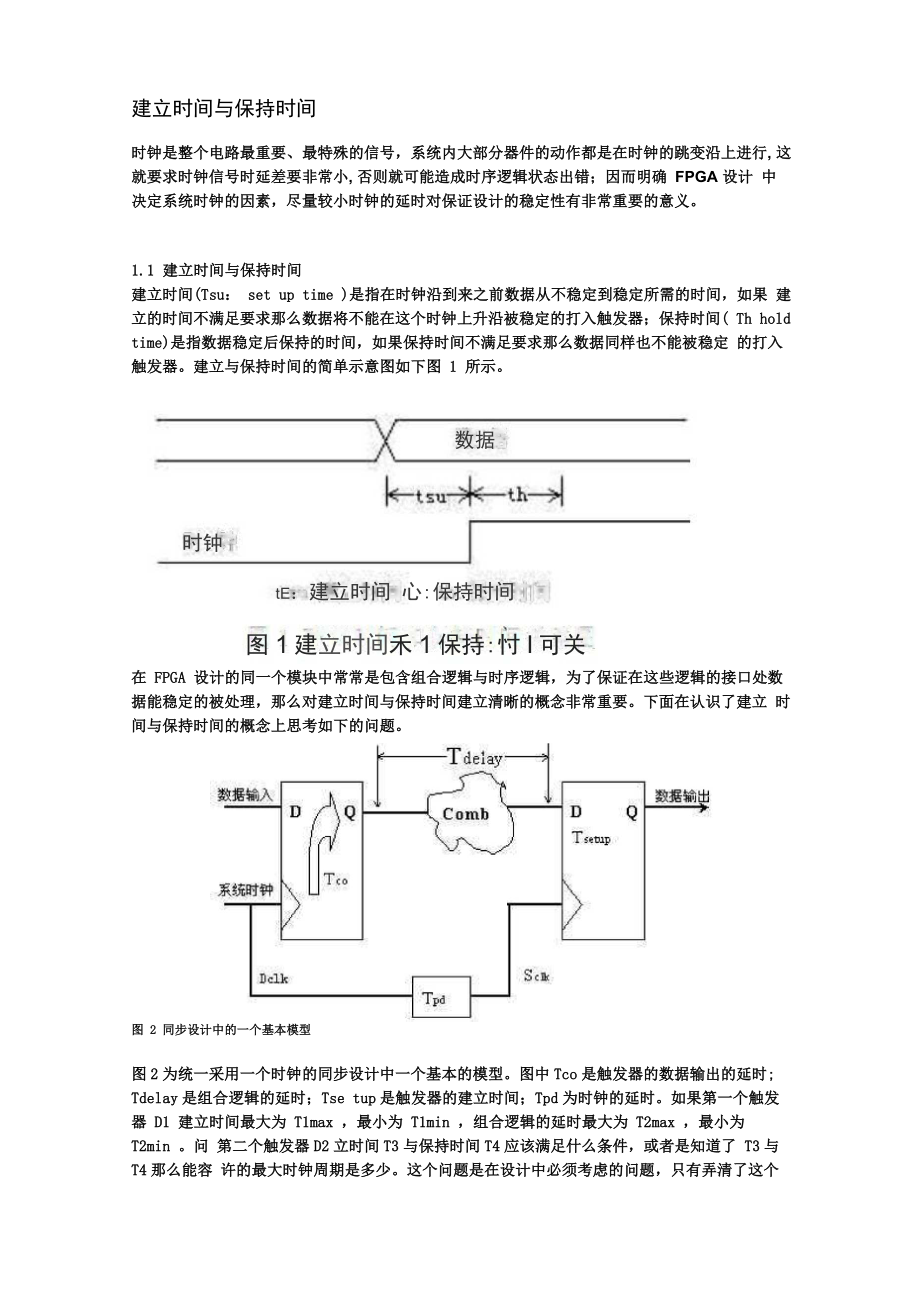

1、建立时间与保持时间时钟是整个电路最重要、最特殊的信号,系统内大部分器件的动作都是在时钟的跳变沿上进行, 这就要求时钟信号时延差要非常小, 否则就可能造成时序逻辑状态出错;因而明确 FPGA 设计 中决定系统时钟的因素,尽量较小时钟的延时对保证设计的稳定性有非常重要的意义。1.1 建立时间与保持时间建立时间(Tsu: set up time )是指在时钟沿到来之前数据从不稳定到稳定所需的时间,如果 建立的时间不满足要求那么数据将不能在这个时钟上升沿被稳定的打入触发器;保持时间( Th hold time)是指数据稳定后保持的时间,如果保持时间不满足要求那么数据同样也不能被稳定 的打入触发器。建立

2、与保持时间的简单示意图如下图 1 所示。时钟数据tE:建立时间 心:保持时间图1建立时间禾1保持:忖I可关系图在 FPGA 设计的同一个模块中常常是包含组合逻辑与时序逻辑,为了保证在这些逻辑的接口处数 据能稳定的被处理,那么对建立时间与保持时间建立清晰的概念非常重要。下面在认识了建立 时间与保持时间的概念上思考如下的问题。图 2 同步设计中的一个基本模型图2为统一采用一个时钟的同步设计中一个基本的模型。图中Tco是触发器的数据输出的延时; Tdelay是组合逻辑的延时;Tse tup是触发器的建立时间;Tpd为时钟的延时。如果第一个触发 器 D1 建立时间最大为 T1max ,最小为 T1mi

3、n ,组合逻辑的延时最大为 T2max ,最小为 T2min 。问 第二个触发器D2立时间T3与保持时间T4应该满足什么条件,或者是知道了 T3与T4那么能容 许的最大时钟周期是多少。这个问题是在设计中必须考虑的问题,只有弄清了这个问题才能保 证所设计的组合逻辑的延时是否满足了要求。下面通过时序图来分析:设第一个触发器的输入为D1,输出为Q1,第二个触发器的输入为D2, 输出为 Q2;时钟统一在上升沿进行采样,为了便于分析我们讨论两种情况即第一:假设时钟的延时 Tpd 为 零,其实这种情况在FPGA设计中是常常满足的,由于在FPGA设计中一般是釆用统 一的系统时钟,也就是利用从全局时钟管脚输入

4、的时钟,这样在内部时钟的延时完全可以 忽略不计。这种情况下不必考虑保持时间,因为每个数据都是保持一个时钟节拍 同时又有线路的延时,也就是都是基于CLOCK的延迟远小于数据的延迟基础上,所以保持时间 都能满足要求,重点是要关心建立时间,此时如果D2的建立时间满足要求那么时序图应该如图 3 所示。从图中可以看出如果:T-Tco-TdelayT3 即: Tdelay=T3这也就是要求的D2的建立时间。从上面的时序图中也可以看出,D2的建立时间与保持时间与D1的建立与保持时 间是没有关系的,而只和D2前面的组合逻辑和D1的数据传输延时有关,这也 是一个很重要的结论。说明了延时没有叠加效应。第二种情况如

5、果时钟存在延时,这种情况下就要考虑保持时间了,同时也需要 考虑建立时间。时钟出现较大的延时多是采用了异步时钟的设计方法,这种方 法较难保证数据的同步性,所以实际的设计中很少采用。此时如果建立时间与保持时间都满足要求那么输出的时序如图 5所示。图 5 时钟存在延-时但满足时序从图5中可以容易的看出对建立时间放宽了 Tpd,所以D2的建立时间需满足要求: Tpd+T-Tco-T2max =T3由于建立时间与保持时间的和是稳定的一个时钟周期,如果时钟有延时,同时数据的延时也较 小那么建立时间必然是增大的,保持时间就会随之减小,如果减小到不满足D2的保持时间要求 时就不能采集到正确的数据,如图6所示。

6、这时即 T(TpdTco-T2min)T-(Tpd+T-Tco-T2min) =T4 即 Tco+T2min-Tpd=T4从上式也可以看出如果Tpd=0也就是时钟的延时为0那么同样是要求Tco+T2minT4,但是在 实际的应用中由于T2的延时也就是线路的延时远远大于触发器的保持时间即T4所以不必要关系保持时间。elkTeo ;!;jQE/丿/ / / / / /21图 6 时钟存在延时且保持时间不满足要求综上所述,如果不考虑时钟的延时那么只需关心建立时间,如果考虑时钟的延时那么也需关心 保持时间。在进行后仿真时,最大延迟用来检查建立时间,最小延时用来检查保持时间(见上面推理的公 式)。下面用

7、数字来说明一下加深理解(以下举例暂不考虑hold time):建立时间 Tsetup=Tdelay+ Teo- Tpd假设Teo (触发器固有的建立时间)=2ns假设1, Clock Delay =0, Data delay=0,那么数据port的新数据必须在时钟port的时钟 沿到来之前2ns赶到数据port, 才能满足触发器的Teo。假设2, Clock delay=0, data Delay = 3ns,那么数据port的新数据必须在时钟port的 时钟沿到来之前5ns就得赶到数据port,其中的3ns用来使新数据从数据port赶到触发器的 D端由于data Delay ),剩下的2ns

8、用来满足触发器的Teo。假设3, Clock delay=1ns , data Delay = 3ns,由于时钟port的时钟沿推后1ns到达触 发器的时钟端,那么数据port的新数据只需在时钟port的时钟沿到来之前4ns赶到数据port 即可。假设4,假设时钟的周期T=4ns,即你的系统需要运行在250M频率上,那么以上的假设中, 假设2显然是不成立的,也就是说在假设2的情况下,你的系统运行频率是低于250M的,或 者说在250M系统里是有setup time violation的。在假设2的情况下,由于Teo及Tpd均 是FPGA的固有特性,要想满足4ns的T,那么唯一你能做的就是想方设

9、法减小Tdelay,也就 是数据路径的延时。即所谓的找出关键路径,想办法优化之。总结,在实际的设计中,对于一个给定的IC,其实我们很容易看到T,Tpd,Tsetup,Th都是 固定不变的(在跨时钟域时,Tpd会有不同),那么我们需要关心的参数就是Tdelay,即数据 路径的延时,控制好了这个延时,那我们的设计就不会存在建立时间和保持时间不满足的情况 了!后记:有个著名的笔试题,这样说道:时钟周期为T,触发器D1的建立时间最大为T1max,最小 为T1min,该触发器的数据输出延时为Teo。组合逻辑电路最大延迟为T2max,最小为T2min。假设D1在前,D2去采样D1的数据(实际就是对图2的文字描述),问,触发器D2的建立 时间T3和保持时间应满足什么条件。这里给出一个简易公式供大家死记一下,以下两个公式确定了 D2的Tsetup和Thold:1) D1 的 Teo + max 数据链路延时 + D2 的 Tsetup T(即 T3 D2 的 Thold (即 T4 Teo + T2min)其实上面的式2可以从T3+T4=T推出,不过要注意把1)中的T2max改为T2min即可。 总之,建立时间长了,保持时间就短了。实际中,某条数据链路延时是一个定值,只不过要求它落在区间T2min,T2max。这也是T2min 和T2max的实际意义。

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。